Fターム[5F110FF35]の内容

Fターム[5F110FF35]に分類される特許

201 - 220 / 286

半導体装置および半導体装置の作製方法

【課題】基板表面と基板上に形成された配線とで形成される段差部分にシリコン膜を形成した場合においても、メモリ素子の書き込み特性を低下させない半導体装置および当該半導体装置の作製方法を提供する。

【解決手段】絶縁表面を有する基板10上に形成された第1の電極11と、第1の電極11の側壁部に形成されたサイドウォール絶縁層12と、第1の電極11上及びサイドウォール絶縁層12を覆って形成されたシリコン膜13と、シリコン膜13上に形成された第2の電極14と、を有し、第1の電極11又は第2の電極14は、シリコン膜13と合金化する材料で形成されているメモリ素子を複数有している。

(もっと読む)

電気光学装置の製造方法、電気光学装置、液晶装置、有機エレクトロルミネッセンス装置、及び電子機器

【課題】有機半導体層を液滴吐出法にて形成する際に、より信頼性の高いものを得る、電

気光学装置の製造方法、電気光学装置、液晶装置、有機エレクトロルミネッセンス装置、

及び電子機器を提供する。

【解決手段】基板10A上に、第1隔壁12をパターン状に設ける。基板10Aに金属材

料を蒸着し、第1隔壁12の上面に画素電極13及び信号線14を形成するとともに、第

1隔壁12に囲まれた領域にゲート線16を形成する。基板10A上に、ゲート絶縁膜形

成領域18、及びゲート絶縁膜形成領域18に一部重なる半導体層形成領域を少なくとも

区画する第2隔壁17を形成する。ゲート絶縁膜形成領域18にゲート絶縁膜26を形成

し、有機半導体層の形成材料を含む機能液を半導体層形成領域に吐出し、ゲート電極16

a及びゲート絶縁膜26の一部を跨ぎ、画素電極13及び信号線14間を電気的に接続す

る有機半導体層28を形成する。

(もっと読む)

有機トランジスタ

【課題】高い移動度、大きな電流オン/オフ比を有し、保存安定性に優れた有機トランジスタを提供する。

【解決手段】有機半導体層を有する有機トランジスタにおいて、該有機半導体層にジベンゾ[fg,ij]ペンタフェン誘導体を少なくとも1種含有してなる有機トランジスタ。

(もっと読む)

半導体装置の製造方法、電子機器の製造方法、半導体装置および電子機器

【課題】SOI基板上に形成された半導体素子の特性を向上させることができる半導体装置の製造方法を提供する。

【解決手段】シリコン基板1と、埋め込み酸化膜3と、シリコン膜5とを有するSOI基板10のシリコン膜5の素子形成領域Acを取り囲む素子分離領域Isを熱酸化することにより熱酸化膜15を形成し、素子形成領域Acに形成された酸化膜を除去した後、堆積膜17を堆積し、素子形成領域Acに位置するシリコン膜5が露出するまで堆積膜17をエッチバックし、露出したシリコン膜5上にMISFETを形成する。その結果、酸化膜の除去の際、熱酸化膜が侵食され素子形成領域と素子分離領域との境界に凹部16が生じても、堆積膜17で埋め込むことができる。

(もっと読む)

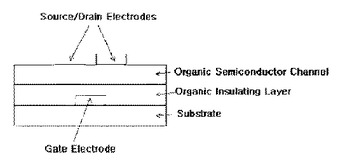

有機半導体素子、有機半導体素子の製造方法、有機トランジスタアレイ、およびディスプレイ

【課題】トランジスタ性能が良好な有機半導体トランジスタを備え、高生産性で製造可能な有機半導体素子を提供することを主目的とする。

【解決手段】本発明は、基板と、上記基板上に形成されたソース電極およびドレイン電極と、上記ソース電極および上記ドレイン電極上に形成され、絶縁性材料からなり、かつ、上記ソース電極および上記ドレイン電極によって構成されるチャネル領域上が開口部となるように形成され、かつ層間絶縁層としての機能を備える絶縁性隔壁部と、上記絶縁性隔壁部の開口部内であり、かつ上記ソース電極および上記ドレイン電極上に形成され、有機半導体材料からなる有機半導体層と、上記有機半導体層上に形成され、絶縁性樹脂材料からなるゲート絶縁層と、上記ゲート絶縁層上に形成されたゲート電極と、を有する有機半導体素子であって、上記絶縁性隔壁部の高さが0.1μm〜1.5μmの範囲内であることを特徴とする、有機半導体素子を提供することにより、上記課題を解決するものである。

(もっと読む)

有機半導体素子、有機半導体素子の製造方法、有機トランジスタアレイ、およびディスプレイ

【課題】有機半導体トランジスタを有する有機半導体素子であって、高効率で製造可能な有機半導体素子を提供することを主目的とする。

【解決手段】本発明は、基板と、上記基板上に形成されたソース電極およびドレイン電極と、上記ソース電極および上記ドレイン電極上に形成され、絶縁性材料からなり、かつ、上記ソース電極および上記ドレイン電極の少なくとも一部を囲うように形成された枠状の絶縁性隔壁部と、上記絶縁性隔壁部の開口部内であり、かつ、上記ソース電極および上記ドレイン電極上に形成され、有機半導体材料からなる有機半導体層と、上記有機半導体層上に形成されたゲート絶縁層と、上記ゲート絶縁層上に形成されたゲート電極と、を有することを特徴とする有機半導体素子を提供することにより、上記課題を解決するものである。

(もっと読む)

有機トランジスタ

【課題】無機半導体デバイスに比べて簡便なプロセスで素子を作製することが可能であり、かつ長時間安定したトランジスタ特性を示す有機トランジスタを提供する。

【解決手段】半導体層が、下記一般式で表される化合物を含有する有機トランジスタ。

(AおよびCは、酸素原子、硫黄原子またはN−R9を表し、BおよびDは、酸素原子または硫黄原子を表し、R1〜R9は、水素原子もしくは1価の有機残基を表す。さらに、R1〜R8のうち隣り合う置換基同士は互いに連結して環を形成していてもよい。)

(もっと読む)

電界効果型トランジスタの製造方法

【課題】 LSIを構成する微細な縦型電界効果型トランジスタ、特に半導体層の両側にゲート電極を有するダブルゲート縦型電界効果型トランジスタの製造方法として最適な縦型電界効果型トランジスタの製造方法を提供する。

【解決手段】 矩形断面を持つ半導体領域を跨ぐように、ゲート絶縁膜を介してゲート電極5を設け、続いてゲート電極5のうち、少なくとも前記略矩形の断面を持つ半導体領域の上端よりも低い位置を絶縁膜で覆うとともに、前記略矩形の断面を持つ半導体の側面のうちゲート電極に覆われない領域の少なくとも一部を露出させ、前記露出した前記略矩形の断面を持つ半導体の側面に、半導体を選択的に成長させ、選択成長と同時または選択成長後に選択的に成長させた前記半導体に不純物を導入することにより、選択的に成長させた前記半導体をソース/ドレイン領域もしくはソース/ドレインエクステンション領域となす

(もっと読む)

有機半導体材料並びにそれを用いた有機半導体素子及び電界効果トランジスタ

【課題】キャリア移動度が高い有機半導体材料及びそれを用いた有機半導体素子を得る。

【解決手段】2級または3級アミンの構造を有するアミン単位と、チオフェン環の構造を有するチオフェン単位とからなることを特徴とする有機半導体材料であり、アミン単位が、好ましくは、以下の構造を有することを特徴としている。

(式中、R1、R2及びR3は、水素、置換されてもよいアルキル基、置換されてもよいアルコキシ基、置換されてもよいエーテル基、または置換されてもよいアリール基であり、互いに同一または異なっていてもよい。)

(もっと読む)

半導体装置及びその製造方法

【課題】SOI基板を用い、LOCOS酸化膜によって素子分離された素子領域にMOSトランジスタにおいてLOCOS酸化膜端部下のシリコン層を介したリーク電流の発生を防止する。

【解決手段】SOI基板のシリコン層5に形成されたLOCOS酸化膜7とLOCOS酸化膜7によって囲まれた素子領域のシリコン層5に互いに間隔をもって形成されたソース領域9及びドレイン領域11と、ソース拡散層9とドレイン拡散層11の間に設けられたチャネル領域と、そのチャネル領域上にゲート絶縁膜15を介して形成されたゲート電極17をもつMOSトランジスタを備え、ゲート電極17はLOCOS酸化膜7とは間隔をもって形成されており、ソース領域9及びドレイン領域11はLOCOS酸化膜7との間に反対導電型領域19を挟んでLOCOS酸化膜7とは間隔をもって形成されている。

(もっと読む)

半導体装置の作製方法

【課題】フォトマスクを使用することなく、微細な加工パターンを高い位置精度で形成する方法、代表的には半導体装置を製造する工程の中でのコンタクト開口に関する方法を提示する。

【解決手段】基板上に薄膜を形成し、薄膜上に層間絶縁膜を形成し、層間絶縁膜及び薄膜に開口部を形成する位置と重なる領域に液滴吐出法によりレンズ材料となる液状物質を着弾させマイクロレンズを形成し、レーザ光をマイクロレンズに照射し薄膜に集光することにより、薄膜及び層間絶縁膜の一部を除去して開口部を形成する。

(もっと読む)

表示装置とその製造方法

【課題】薄膜トランジスタ特性の向上した表示装置を提供する。

【解決手段】本発明は表示装置とその製造方法に関するものであって、本発明による表示装置は絶縁基板と、絶縁基板上に形成されておりシリコンおよびフッ素を含む半導体層と、少なくとも一部が半導体層上に形成されるソース電極と、少なくとも一部が半導体層上に形成されておりソース電極とチャンネル領域を介して離隔されているドレイン電極と、半導体層とソース電極の間および半導体層とドレイン電極の間に形成されるオーミックコンタクト層と、半導体層上に形成される絶縁膜とを含むことを特徴とする。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】本発明は、有機薄膜トランジスタの特性を維持して、必要とするマスク数を減らす。

【解決手段】本発明は、基板と、前記基板上に形成されているデータ線と、前記データ線と交差してゲート電極を含むゲート線と、前記データ線と接続されているソース電極と、前記ソース電極と対向するドレイン電極と、前記ソース電極及び前記ドレイン電極と一部接触している有機半導体と、前記ゲート電極及び前記有機半導体の間に位置するゲート絶縁部材と、そして前記有機半導体及び前記ゲート絶縁部材が位置して横部及び縦部が交差する十字状に形成されている開口部とを有する隔壁を含む薄膜トランジスタ表示板及びその製造方法を提供する。

(もっと読む)

半導体装置の作製方法

【課題】触媒元素のスピン添加法は、対角線の長さが500mm以上の大型基板を用いる際、触媒元素添加量の基板内均一性が良くないという問題が顕著となる。触媒元素添加量の基板内不均一性は、熱結晶化後の結晶質半導体膜に於ける結晶性のバラツキに影響し最終的に当該結晶質半導体膜で構成されたTFTの電気特性に悪影響を及ぼすことが考えられる。本発明は、上記問題点を解決することを課題とする。

【解決手段】触媒元素のスピン添加工程に於いて、絶縁性基板の中央部と、端部とにおける触媒元素の濃度比が2倍以内となるように添加するために、「触媒元素溶液の滴下」処理から「高速スピンによるスピン乾燥」処理に移行する間のスピン回転加速度を低くし、触媒元素添加量の基板内不均一性を改善する。

(もっと読む)

カラー液晶表示装置、カラー表示装置

【課題】フォトリソグラフィー工程数を低減することで製造コストの低減および歩留まりの向上を実現し得るカラー表示装置の製造方法を提供する。

【解決手段】透明基板710上にソース線705、ドレイン電極708となる線状遮光体701、701kを形成した後、開口部711に色素材702を定着させてカラーフィルターとする。次に、色素材を覆う透明保護膜723を成膜し、その上に多結晶シリコン薄膜717を形成する。そして、画素マトリックス外のソース線端子を覆うポリイミド膜を形成した後、ゲート絶縁膜719を成膜し、ポリイミド膜を除去する。次に、ゲート絶縁膜上にゲート線707を形成する。本方法におけるフォトリソグラフィー工程は、線状遮光体形成、多結晶シリコン薄膜形成、ゲート電極形成、の3工程のみとなる。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】ゲート絶縁膜の被覆不良によるゲート電極と半導体層とのショート及びリーク電流などの不良が防止された信頼性の高い半導体装置、及びそのような半導体装置の作製方法を提供することを目的とする。

【解決手段】絶縁表面上に複数の半導体素子を形成するために、連続した半導体層中に半導体素子として機能する素子領域と、抵抗が高く素子領域間を電気的に分離する機能を有する素子分離領域を形成する。素子分離領域は、連続した半導体層において、素子間を電気的に分離するために、選択的に酸素、窒素、及び炭素のうち少なくとも一種以上の不純物元素を添加して形成する。

(もっと読む)

薄膜トランジスタ基板及びその製造方法、表示装置

【課題】絶縁耐圧の低下を抑制した薄膜トランジスタ基板を提供すること。

【解決手段】本発明の一態様に係る薄膜トランジスタアレイ基板は、TFTアレイ基板103上に形成されたシリコン酸化膜122と、シリコン酸化膜122上に形成された多結晶シリコン膜123のパターンと、多結晶シリコン膜123のパターン上に形成されたゲート絶縁膜124とを有する多結晶シリコン薄膜トランジスタを有し、多結晶シリコン膜123のパターンからはみ出したシリコン酸化膜122のTFTアレイ基板103に垂直な方向の削れ量は、10nm以下であるものである。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】電界効果トランジスタを構成するp型半導体層内のドーパント不純物量やp型層とゲート絶縁膜間の界面準位密度を制御することにより、チャネルとなるp型半導体層の低抵抗を確保しつつ、コラプス現象を抑制し、更に高温での動作を安定化し、良好な信頼性を確保する。

【解決手段】基板2と、前記基板2の上に形成され、p型のドーパントとともにn型のドーパントがドーピングされた前記基板と格子定数が異なるp型の窒化物系化合物半導体層3と、前記p型の窒化物系化合物半導体層3上に形成された絶縁膜4と、前記p型の窒化物系化合物半導体層3をチャネル層とするために前記p型の窒化物系化合物半導体層3と電気的に接続されたソース電極S及びドレイン電極Dと、前記絶縁膜4上に形成されたゲート電極Gと、を有する電界効果トランジスタ1。

(もっと読む)

有機薄膜トランジスタのゲート絶縁膜形成用組成物およびそれを用いた有機薄膜トランジスタ

本発明は、ポリアリレートを含む有機薄膜トランジスタのゲート電極絶縁膜形成用組成物、およびその組成物からなる、有機半導体チャネルと接するゲート絶縁膜を含む有機薄膜トランジスタを提供する。  (もっと読む)

(もっと読む)

薄膜トランジスタ

【課題】キンク効果の抑制だけでなく、チャネル長変調効果を抑制可能な薄膜トランジスタを実現する。

【解決手段】ゲート電極6を構成する第1及び第2ゲート電極6a,6bにおいて、第1ゲート電極6aのゲート長W6aよりも、第2ゲート電極6bのゲート長W6bを短く構成し、かつ、第2ゲート電極6bのゲート長W6bを、短チャネル効果を発生させる程度に短く構成する。これにより、第1ゲート電極6aに対応する第1トランジスタのしきい値電圧Vthaよりも、第2ゲート電極6bに対応する第2トランジスタのしきい値電圧Vthbを低くすることができる。第1及び第2ゲート電極6a,6bに同一電圧を印加した場合、ドレイン側のチャネル瑞における電界集中が抑制される。その結果、チャネル長変調効果を緩和することができる。

(もっと読む)

201 - 220 / 286

[ Back to top ]