Fターム[5F110FF35]の内容

Fターム[5F110FF35]に分類される特許

281 - 286 / 286

ドープされたゲート誘電体を有するトランジスタ

トランジスタおよびその製造方法。ゲート誘電体材料を堆積する前に半導体基材をドープする。別個のアニール工程、または、トランジスタを製造するために使用される後続のアニール工程の間を用いて、ドーパント種を、基材のドープされた領域から、ゲート誘電体内に出力拡散して、ドープされたゲート誘電体を生成する。ドーパント種は、ゲート誘電体の原子構造における各空孔を埋め、その結果、トランジスタの動作速度が上昇し、電力消費が低減され、電圧安定性が改善される。  (もっと読む)

(もっと読む)

高K誘電体膜

誘電体層(14,22,24,32)は、ランタン、ルテチウム、及び酸素により構成され、かつ2つの導体の間、または導体(14,20,34)と基板(12,26,30)との間に形成される。一の実施形態では、誘電体層は基板を覆って形成され、境界層を追加する必要がない。別の実施形態では、誘電体層(22,42,46)に含まれる元素の分布は、ランタン含有量またはルテチウム含有量に関して傾斜する、または誘電体層(22,42,46)は別の構成として、アルミニウムを含むことができる。更に別の実施形態では、絶縁層を導体または基板と誘電体層との間、または導体及び基板の両方と誘電体層との間に形成する。誘電体層は、分子ビームエピタキシー法によって形成することが好ましいが、原子層化学気相成長、物理気相成長、有機金属化学気相成長、またはパルスレーザ堆積によって形成することもできる。  (もっと読む)

(もっと読む)

短チャネル効果を減少させる埋め込みチャネルフラッシュ構造

短チャネル効果を減少させたメモリセルを記載する。ソース領域(54)およびドレイン領域(56)を半導体ウェーハ(58)中に形成する。ソース領域(54)およびドレイン領域(58)の間にトレンチ領域(59)を形成する。このトレンチ領域、ソース領域およびドレイン領域の下に埋め込みチャネル領域(52)を形成する。半導体基板のトレンチ領域中にゲート絶縁層(60)を形成する。このゲート絶縁層は、埋め込みチャネル領域上に、およびソース領域とドレイン領域との間に形成される。埋め込みチャネル領域の上の半導体基板上に、制御ゲート層(70)を形成する。この制御ゲート層は、ゲート絶縁層によって埋め込みチャネルから分離される。  (もっと読む)

(もっと読む)

集積回路のトランジスタにおける金属ゲート構造および形成方法(高性能デバイスの金属置換ゲートのための構造および方法)

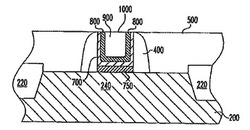

【課題】 高性能デバイスの金属置換ゲートのための構造および形成方法を提供する。

【解決手段】 まず、半導体基板(240)上に設けたエッチ・ストップ層(250)上に、犠牲ゲート構造(260)を形成する。犠牲ゲート構造(300)の側壁上に、1対のスペーサ(400)を設ける。次いで、犠牲ゲート構造(300)を除去して、開口(600)を形成する。続けて、スペーサ(400)間の開口(600)内に、タングステン等の金属の第1の層(700)、窒化チタン等の拡散バリア層(800)、およびタングステン等の金属の第2の層(900)を含む金属ゲート(1000)を形成する。

(もっと読む)

ポリマーデバイスの製造

(i)ポリマーまたはオリゴマーおよび架橋部分を含む溶液を基板上に成膜して層を形成する工程、および(ii)不溶性架橋化ポリマーを形成する条件下で工程(i)で形成された層を硬化する工程を備え、架橋部分が溶液中のポリマーまたはオリゴマーおよび架橋部分の繰返し単位のモル総数に対して0.05から5モル%の範囲の量で工程(i)に存在することを特徴とする、ポリマーデバイスを形成する方法。 (もっと読む)

半導体装置および電子機器

【課題】 本発明では剥離技術を用いることにより様々な基板上に薄膜素子を形成し、従来の技術では不可能であると考えられていた部分に薄膜素子を形成することにより、省スペース化を図ると共に耐衝撃性やフレキシビリティに優れた半導体装置を提供する。

【解決手段】 本発明では、剥離技術を用いて一旦基板から剥離させた膜厚50μm以下の素子形成層を基板上に固着することにより、様々な基板上に薄膜素子を形成することを特徴とする。例えば、可撓性基板上に固着された薄膜素子をパネルの裏面に貼り付けたり、直接パネルの裏面に固着したり、さらには、パネルに貼り付けられたFPC上に薄膜素子を固着することにより、省スペース化を図ることができる。

(もっと読む)

281 - 286 / 286

[ Back to top ]