Fターム[5F110FF35]の内容

Fターム[5F110FF35]に分類される特許

121 - 140 / 286

有機薄膜トランジスタ、有機薄膜トランジスタの製造方法、有機薄膜トランジスタアレイ及び表示装置

【課題】インクジェット法による有機半導体層のパターン形成を歩留まり良く達成することができる有機薄膜トランジスタの製造方法を提供する。

【解決手段】基板、ゲート電極、ゲート絶縁膜、該ゲート絶縁膜よりも表面自由エネルギーの高いソース電極、該ゲート絶縁膜よりも表面自由エネルギーの高いドレイン電極、有機半導体層を有する有機薄膜トランジスタの製造方法であって、有機半導体を第一の溶媒に溶解し、インクジェット法で滴下することで、該ソース電極と該ドレイン電極と該ゲート絶縁膜と、あるいは該ソース電極と該ドレイン電極と接触する島状有機半導体層を形成する段階と、該有機半導体を可溶な第二の溶媒をインクジェット法で該島状有機半導体層に滴下し、該ソース電極と該ドレインン電極と該ゲート絶縁膜と接触する島状有機半導体層を形成する段階を含み、第二の溶媒は第一の溶媒より表面張力が低く、かつ、第二の溶媒は第一の溶媒より沸点が低い、ことを特徴とする。

(もっと読む)

電界効果型トランジスタ

【課題】金属酸化物をチャネルに用いた電界効果型トランジスタにおいて、ゲート絶縁層とチャネル層との間の界面が良好な構造を提供する。

【解決手段】基板1と、前記基板1上に、ゲート電極5と、ゲート絶縁層6と、チャネル層4と、ソース電極2と、ドレイン電極3と、を有し、前記ゲート絶縁層6及び前記チャネル層4は、ガリウム(Ga)及び酸素(O)を少なくとも構成元素とする層である、電界効果型トランジスタ。

(もっと読む)

平坦な導電性膜の製造方法及び半導体装置の製造方法並びに半導体装置

【課題】半導体装置の消費電力を低減させることができる半導体装置の製造方法を提供する。

【解決手段】基板(S1)を準備する工程と、テンプレート(S2)を準備する工程と、前記テンプレート表面にゲート電極(10)を形成する工程と、前記基板およびテンプレートを貼り合わせる工程と、前記テンプレートから前記基板および前記ゲート電極を一体的に剥離して前記ゲート電極を前記テンプレートから前記基板に転写するする工程と、を有する。かかる方法によれば、ゲート電極の表面の平坦性が向上し、その上に形成されるゲート絶縁膜(12)の表面の平坦性も向上する。その結果、ゲート絶縁膜の薄膜化が容易となり、半導体装置の消費電力の低減ができる。

(もっと読む)

薄膜トランジスタの製造方法

【課題】半導体膜、及び保護膜を適正な膜厚で所定の位置に精度良く形成することができ、且つ、生産性の優れた薄膜トランジスタの製造方法を提供する。

【解決手段】半導体膜を保護する保護膜を有する薄膜トランジスタの製造方法において、下地層の表面に、該下地層の表面の所定の領域を囲むように、半導体溶液に対し該所定の領域よりも高い撥液性を有する撥液層を形成する工程と、所定の領域に、半導体溶液を塗布し半導体膜を成膜する工程と、半導体膜の表面に、保護膜材料溶液を塗布し該半導体膜を覆う保護膜を成膜する工程と、を有し、撥液層の表面の撥液性は、面内強度分布を有し、所定の領域の近傍で最も高く、保護膜材料溶液の塗布する液量は、半導体溶液の塗布する液量よりも多くする。

(もっと読む)

半導体素子の製造方法

【課題】欠陥が低減され膜質が良好なゲート酸化膜を有する半導体素子を製造する。

【解決手段】基板2のフィールド領域の表面にフィールド酸化膜4を形成する工程と、フィールド酸化膜4を形成した基板2の第1アクティブ領域および第2アクティブ領域の表面に第1ゲート酸化膜11A,11Bを形成する工程と、第1ゲート酸化膜11A,11Bに第1純水ヒーリングを施す工程と、第2アクティブ領域における第1ゲート酸化膜11Bを除去する工程と、第1アクティブ領域および第2アクティブ領域の表面に第2ゲート酸化膜12A,12Bを形成する工程と、第2ゲート酸化膜12A,12Bに第2純水ヒーリングを施す工程と、第1アクティブ領域および第2アクティブ領域における第2ゲート酸化膜12A,12B上にゲート電極8を形成する工程と、をこの順に有する半導体素子の製造方法。

(もっと読む)

有機半導体素子、及びその製造方法

【課題】有機半導体層にダメージを与えず、デバイス特性を低下させることのない保護膜を形成した有機半導体素子及びその製造方法を提供する。

【解決手段】有機半導体素子1は、基板2を有し、基板2の上面にはゲート電極3が設けられている。ゲート電極3の上面及び基板2の上面にはゲート絶縁層4が設けられている。ゲート絶縁層4の上面には、ソース電極7とドレイン電極8が離間して設けられている。ソース電極7とドレイン電極8に挟まれるゲート絶縁層4の上面には有機半導体層6が設けられている。有機半導体層6、ソース電極7、ドレイン電極8及びゲート絶縁層4の上面には下側からフッ素樹脂層11、水溶性樹脂層12、ガラスコーティング層13の3層構造の保護膜10が設けられている。保護膜10の上面には画素電極21が形成されており、この画素電極21は、コンタクトホール31により、ソース電極7と導通している。

(もっと読む)

SiGeチャネルを有するデュアル高K酸化物

PMOSデバイス領域112、113内にシリコンゲルマニウムチャネル層21を有する単一基板15にデュアルゲート酸化物(DGO)トランジスタデバイス50、52およびコアトランジスタデバイス51、53を集積するための方法および装置を記載する。各DGOトランジスタデバイス50、52は、金属ゲート25と、第2の相対的により高い高K金属酸化物層24から形成された上部ゲート酸化物領域60、86と、第1の相対的により低い高K誘電体層22から形成された下部ゲート酸化領域58、84とを含む。また、各コアトランジスタデバイス51、53は、金属ゲートと、第2の相対的により高い高K金属酸化物層24から形成されたコアゲート誘電層72、98とを含む。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】半導体装置の作製工程において、高調波のCWレーザを半導体膜上に相対的に走査させながら照射すると、走査方向に延びた長い結晶粒がいくつも形成される。このようにして形成された半導体膜は前記走査方向においては実質的に単結晶に近い特性のものとなるが、高調波のCWレーザの出力が小さくアニールの効率が悪い。

【解決手段】第2高調波に変換されたCWレーザと同時に基本波のCWレーザを半導体膜の同一部分に照射することで、出力の補助を行う。通常、基本波は1μmあたりの波長域に入り、この波長域では半導体膜に対する吸収が低い。しかしながら、可視光線以下の高調波を基本波と同時に半導体膜に照射すると、高調波により溶かされた半導体膜に基本波はよく吸収されるため、アニールの効率が著しく上がる。

(もっと読む)

発光装置の作製方法及び液晶表示装置の作製方法

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って剥離することを可能とする。

【解決手段】基板上に金属層を形成する工程と、前記金属層上に酸化物層を形成する工程と、前記酸化物層上に絶縁層を形成する工程と、前記絶縁層上に薄膜トランジスタを形成する工程と、前記薄膜トランジスタ上に発光素子を形成する工程と、人間の手又は前記薄膜トランジスタを引き剥がす装置を用いることにより、前記酸化物層の層内または界面において前記基板から前記薄膜トランジスタを剥離する工程とを有する。

(もっと読む)

半導体ゲート絶縁膜の形成方法

【課題】 低温の酸素ラジカルで酸化した膜は、初期特性こそ従来の熱酸化膜同等以上の特性を得られるが、各種のストレスを印加した場合、その特性が大きく劣化するという問題を有しており、その対策が望まれていた。

【解決手段】 500℃以下の温度で保持されたシリコン基板に対し、酸素ラジカルを用いてシリコン表面を酸化し、シリコン酸化膜を形成する半導体ゲート絶縁膜の形成方法において、ラジカル酸化を行う前に、シリコン基板表面を終端している水素原子を1x1014原子/cm2以下の面密度にまで除去することを特徴とする。

(もっと読む)

半導体装置の製造方法、半導体装置、および電気光学装置

【課題】、ポリシリコン膜に含まれる結晶欠陥を電気的に略不活性化させた場合でも、その後の工程での処理温度が限定されることがなく、かつ、能動層とゲート絶縁層との間に良好な界面を形成することができる半導体装置の製造方法、半導体装置および電気光学装置を提供すること。

【解決手段】半導体装置10tの製造工程では、電界効果型トランジスタ30nの能動層となるシリコン膜1sを結晶化させた後、シリコン膜1sに酸素プラズマ照射OPを行う酸素プラズマ照射工程と、酸素プラズマ照射工程によりシリコン膜1sに形成された表面酸化物1rを除去する表面酸化物除去工程とを行う。その後、シリコン膜1sをパターニングする。

(もっと読む)

ゲート絶縁膜層成形材料、電界効果型トランジスタ及びこの電界効果型トランジスタの製造方法

【課題】 FET特性値の向上が可能である、ゲート絶縁膜層形成材料、電界効果型トランジスタ及びこの電界効果型トランジスタの製造方法を提供する。

【解決手段】 ゲート電極、ソース−ドレイン電極、チャネル層を構成する半導体層及びゲート電極とチャネル層とに挟まれたゲート絶縁膜を備えた電界効果型トランジスタ用のゲート絶縁膜層形成材料であって、前記ゲート絶縁膜がエポキシ樹脂からなり、このエポキシ樹脂の硬化剤として下記一般式(1)で示される重縮合型アリーロキシシラン化合物を用いるゲート絶縁膜層形成材料。

(もっと読む)

半導体装置及びその作製方法

【課題】メモリ回路の高集積化、あるいは小型化を果たす上で、メモリセルの面積を縮小することが重要になると考えられる。特別なプロセスを増やすことなくメモリセルの面積を縮小化した記憶装置を提供することを課題とする。

【解決手段】選択トランジスタと、メモリ素子と、アシスト容量とを有する半導体装置であって、メモリ素子の一方の電極とアシスト容量の一方の電極は共通電極であり、アシスト容量の他方の電極は不純物を有する半導体膜から形成され、メモリ素子の一方の電極とアシスト容量の他方の電極は絶縁膜を介して重畳している。

(もっと読む)

有機薄膜トランジスタ

【課題】誘電体層と半導体層の間の所定の構造の2つの界面層を有する、オン/オフ比や移動度の改良された薄膜トランジスタを提供する。

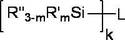

【解決手段】OTFT10は、誘電体層40と半導体層70の間に2つの界面層80,90があり、一方の界面層が、シロキサンポリマーまたはシルセスキオキサンポリマーから形成されており、他方の界面層が、式(I)のシランから形成されている。

式(I)

(上記式(I)中、R’は、約1個から約24個までの炭素原子を有するアルキルであり、R”は、約1個から約24個までの炭素原子を有するアルキル、ハロゲン、アルコキシ、ヒドロキシルまたはアミノであり、Lは、ハロゲン、酸素、アルコキシ、ヒドロキシル、またはアミノであり、kは、1または2であり、mは、1、2または3である。)

(もっと読む)

半導体装置の製造方法

【課題】安定なFET特性を得ること。

【解決手段】本半導体装置の製造方法は、基板上にGaN系半導体層を形成する工程と、ALD装置内で、ゲート絶縁膜の成長温度に比べ高い温度で熱処理を実施し、前記GaN系半導体層の表面のフッ素を除去する工程S20と、前記フッ素を除去する工程S20の後、前記ALD装置内で、前記GaN系半導体層の表面に前記ゲート絶縁膜を形成する工程S16と、前記ゲート絶縁膜上にゲート電極を形成する工程と、を含む。

(もっと読む)

アルミニウム含有有機化合物溶液、電界効果型トランジスタ及び電界効果型トランジスタの作製方法

【課題】ゲート絶縁膜の膜厚ムラや点欠陥を低減し、デバイスエラー率が低減可能なゲート絶縁膜を有する電界効果型トランジスタを提供する。

【解決手段】ゲート電極と、ソース-ドレイン電極と、チャネル層を構成する半導体層と、前記ゲート電極と前記チャネル層とに挟まれたゲート絶縁膜とを備えた電界効果型トランジスタにおいて、前記ゲート絶縁膜が絶縁性有機高分子からなり、前記ゲート絶縁膜を形成させる際、被着体の界面に、アルミニウム含有有機化合物溶液によりアルミニウム含有有機化合物層を形成してなる、電界効果型トランジスタ。

(もっと読む)

薄膜トランジスタ基板及びその製造方法

【課題】基板の大きさが大きくなっても信号遅延による問題が少なく、カラーフィルタが安定的に埋め込められる薄膜トランジスタ基板及びその製造方法を提供する。

【解決手段】薄膜トランジスタ基板は、絶縁基板と、絶縁基板上に形成され、ゲート電極を含むゲート線と、有機物質で形成され縦部を含む隔壁と、隔壁によって区画された領域に形成されたカラーフィルタと、ゲート電極を含み一部が隔壁上に形成される薄膜トランジスタと、ゲート線に交差し隔壁上で隔壁の縦部に沿って形成されるデータ線を含む。

(もっと読む)

半導体装置の製造方法

【課題】活性領域表面に凹凸を生じることなく活性領域上端の角部を丸めることができる半導体装置の製造方法を提供する。

【解決手段】活性領域を画定する素子分離絶縁膜を形成する工程と、活性領域上に、0.1nm以上、0.7nm未満の膜厚の自然酸化膜を形成する工程と、水素を含む雰囲気中で、850℃よりも高く950℃未満の温度で熱処理を行い、活性領域の角部を丸めるとともに、自然酸化膜を還元除去する工程と、自然酸化膜を除去した活性領域上に、ゲート絶縁膜を形成する工程とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】MISトランジスタを有する半導体装置の性能を向上させる。

【解決手段】シリコン基板1の主面上に半導体層を積み上げて形成された一対のソース・ドレイン領域sdn,sdpと、その側壁を覆う側壁絶縁膜ISと、側壁絶縁膜ISに平面的に挟まれた位置のシリコン基板1の主面上に、ゲート絶縁膜IGを隔てて配置されたゲート電極GEと、ゲート電極GEの側方下部からソース・ドレイン領域sdn,sdpの側方下部に渡って形成されたエクステンション領域exn,expとを有する半導体装置であって、ソース・ドレイン領域sdn,sdpの側壁は順テーパ状の傾斜を有しており、側壁絶縁膜ISの側壁のうち、ゲート絶縁膜IGおよびゲート電極GEと隣り合う方の側壁は、順テーパ状の傾斜を有している。

(もっと読む)

薄膜トランジスタおよびそれを用いた装置

【課題】薄膜トランジスタの構成部材の位置ずれを抑制し、さらに寄生容量の低減を図った薄膜トランジスタおよびそれを用いた装置の提供。

【解決手段】絶縁基板上に、ソース電極、ドレイン電極、前記ソース電極と前記ドレイン電極に電気的に接続される半導体層と、少なくとも前記半導体層上に形成されるゲート絶縁膜と、前記ゲート絶縁膜上に前記半導体層と重畳して配置されるゲート電極を備えるものであって、

前記ソース電極上に重ねられて第1バンク絶縁膜、前記ドレイン電極上に重ねられて第2バンク絶縁膜が形成され、

前記半導体層、ゲート絶縁膜、およびゲート電極は、前記第1バンク絶縁膜と前記第2バンク絶縁膜の間の領域に形成されている。

(もっと読む)

121 - 140 / 286

[ Back to top ]