Fターム[5F110FF35]の内容

Fターム[5F110FF35]に分類される特許

41 - 60 / 286

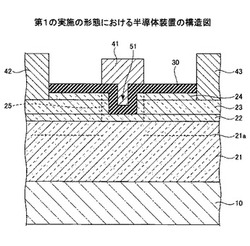

半導体装置の製造方法及び半導体装置

【課題】低コストでしきい値電圧のバラツキの少ないノーマリーオフ化されたHEMTを提供する。

【解決手段】基板10の上方に半導体層21〜24を形成する工程と、半導体層23〜24にフッ素成分を含むガスを用いたドライエッチングによりリセス51となる開口部を形成する工程と、半導体層を加熱することによりリセス51の側面及び底面に付着しているフッ素を半導体層22〜24に拡散させフッ素を含む領域を形成する工程と、リセス51の内面及び半導体層22〜24上に絶縁膜30を形成する工程と、リセス51が形成されている領域に絶縁膜30を介し電極41を形成する工程と、を有する。

(もっと読む)

化合物半導体装置の製造方法及び洗浄剤

【課題】リセス等の形成に伴う処理で生じる残渣を適切に除去することができる化合物半導体装置の製造方法及び洗浄剤を提供する。

【解決手段】化合物半導体積層構造1を形成し、化合物半導体積層構造1の一部を除去して凹部4を形成し、洗浄剤を用いて凹部4内の洗浄を行う。洗浄剤は、凹部4内に存在する残渣と相溶する基材樹脂と溶媒とを含む。

(もっと読む)

半導体装置、電源装置、増幅器及び半導体装置の製造方法

【課題】半導体層とゲート電極との間に絶縁膜が形成された半導体装置の信頼性を高める。

【解決手段】基板の上方に形成された半導体層と、前記半導体層上に形成された絶縁膜と、前記絶縁膜上に形成された電極と、を有し、前記絶縁膜は炭素を主成分とするアモルファス膜を含むものであることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置

【課題】バンド間トンネリングが横方向に起こる構造を有し、バンド間トンネリングが起こる領域が大きいトンネルトランジスタを備える半導体装置を提供する。

【解決手段】第1上面S1と、第1上面S1よりも高さの低い第2上面S2と、第1上面と第2上面との間に存在する段差側面S3と、を有する段差が形成された基板。さらに、基板の段差側面S3と第2上面S2とに連続して形成されたゲート絶縁膜と、基板の段差側面S3に形成されたゲート絶縁膜に接するよう、第2上面S2上にゲート絶縁膜131を介して形成されたゲート電極132とを備える。さらに、基板内において、第1上面の下方に形成された第1導電型のソース領域121と、第2上面の下方に形成された第2導電型のドレイン領域122と、段差側面S3とソース領域122との間に形成された第2導電型の側方拡散領域123とを備える。

(もっと読む)

記憶装置、半導体装置、検出方法

【課題】データの保持時間が所定の長さに満たないメモリセルを検出するための検証動作を、短時間にて正確に行うことができる記憶装置の提供。

【解決手段】各メモリセルに、第1容量素子と、第2容量素子と、上記第1容量素子及び第2容量素子における電荷の供給、保持、放出を制御するためのスイッチング素子として機能するトランジスタと、を少なくとも有する。また、第1容量素子の容量値が、第2容量素子の容量値の1000倍以上、好ましくは10000倍以上となるようにする。そして、通常動作の時に、第1容量素子及び第2容量素子を用いて電荷の保持を行う。また、データの保持時間が所定の長さに満たないメモリセルを検出するための検証動作を行う時に、第2容量素子を用いて電荷の保持を行う。

(もっと読む)

窒化ガリウム系半導体装置および半導体装置の製造方法

【課題】窒化ガリウム系半導体のドライエッチングに、塩素系ガスを用いたICP−RIEを用いると、誘電結合型プラズマは、温度が高いので、エッチングされた面に凹凸ができ、半導体にダメージを与え、塩素が残留する。

【解決手段】窒化ガリウム系半導体からなる第1の半導体層を形成する第1半導体層形成工程と、第1の半導体層の一部を、臭素系ガスを用いて、マイクロ波プラズマプロセスでドライエッチングして、リセス部を形成するリセス部形成工程と、を備え、窒化ガリウム系半導体装置を製造する半導体装置の製造方法を提供する。

(もっと読む)

酸化物半導体膜および半導体装置

【課題】より電気伝導度の安定した酸化物半導体膜を提供することを課題の一とする。また、当該酸化物半導体膜を用いることにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供することを課題の一とする。

【解決手段】結晶性を有する領域を含み、当該結晶性を有する領域は、a−b面が膜表面に概略平行であり、c軸が膜表面に概略垂直である結晶よりなる酸化物半導体膜は、電気伝導度が安定しており、可視光や紫外光などの照射に対してもより電気的に安定な構造を有する。このような酸化物半導体膜をトランジスタに用いることによって、安定した電気的特性を有する、信頼性の高い半導体装置を提供することができる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体膜をチャネルに用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】加熱処理により第1の結晶構造となりうる酸化物半導体膜と、加熱処理により第2の結晶構造となりうる酸化物半導体膜を積層して形成し、その後加熱処理を行うことによって、第2の結晶構造を有する酸化物半導体膜を種として第1の結晶構造を有する酸化物半導体膜へ結晶成長する。このようにして形成した酸化物半導体膜を、トランジスタの活性層に用いる。

(もっと読む)

半導体膜、半導体素子、半導体装置およびそれらの作製方法

【課題】特性が安定した半導体膜を提供することを目的の一とする。または、特性が安定した半導体素子を提供することを目的の一とする。または、特性が安定した半導体装置を提供することを目的の一とする。

【解決手段】具体的には、絶縁性の表面に一方の面を接する第1の結晶構造を有する結晶を含む種結晶層(シード層)と、当該種結晶層(シード層)の他方の面に異方性の結晶が成長した酸化物半導体膜を有する構成とすれば良く、このようなヘテロ構造とすることにより、当該半導体膜の電気特性を安定化することができる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート絶縁膜における電荷トラップを大幅に低減し、信頼性の高い化合物半導体装置を実現する。

【解決手段】化合物半導体層2と、化合物半導体層2上でゲート絶縁膜6を介して形成されたゲート電極7とを備えており、ゲート絶縁膜6は、SixNyを絶縁材料として含有しており、SixNyは、0.638≦x/y≦0.863であり、水素終端基濃度が2×1022/cm3以上5×1022/cm3以下の範囲内の値とされたものである。

(もっと読む)

半導体装置の作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体

装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体

層とソース電極層及びドレイン電極層との間に金属酸化物層でなるバッファ層が設けられ

た逆スタガ型(ボトムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース

電極層及びドレイン電極層と半導体層との間に、バッファ層として金属酸化物層を意図的

に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁膜上に保護膜を形成した構造において、絶縁耐圧の低下を防ぐ。

【解決手段】基板上に形成された第1の半導体層と、前記第1の半導体層上に形成された第2の半導体層と、前記第2の半導体層上に形成されたソース電極及びドレイン電極と、前記第2の半導体層上に形成された絶縁膜と、前記絶縁膜上に形成されたゲート電極と、前記絶縁膜を覆うように形成された保護膜と、を有し、前記保護膜は、熱CVD、熱ALD、真空蒸着のいずれかにより形成されたものであることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体膜を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体用ターゲットに含まれる複数種の原子の原子量の違いを利用し、原子量の小さい亜鉛を優先的に酸化物絶縁膜に堆積させ、亜鉛を含む種結晶を形成すると共に、種結晶上に原子量の大きいスズ、インジウム等を結晶成長させつつ堆積させることで、複数の工程を経ずとも、結晶性酸化物半導体膜を形成することを要旨とする。さらには、種結晶として、六方晶構造の亜鉛を含む結晶を有する種結晶を核として、結晶成長させて結晶性酸化物半導体膜を形成することで、単結晶、または実質的に単結晶である結晶性酸化物半導体膜を形成することを要旨とする。

(もっと読む)

パターン形成方法及び回路基板の製造方法

【課題】印刷法にて、容易にヴィアホール等のパターンを形成する方法を提供する事。

【解決手段】基板上に設けられた第一高分子材料からなる第一薄膜をパターニングする際に、第一高分子材料を溶解する第一溶媒に第二高分子材料を溶解させた高分子溶液を準備し、これを第一薄膜に滴下する高分子溶液滴下工程と、第一溶媒が乾燥した後に第一薄膜を第二溶媒に触れさせる第二溶媒接触工程と、を含み、第二溶媒は第一高分子材料を溶解せず、第二高分子材料を溶解する溶媒とする。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域となるSOI構造を有する半導体線条突出部の形状のばらつきを抑制し、トランジスタ特性のばらつきを減少することができる半導体装置を提供する。

【解決手段】半導体基板1の素子分離用の溝に埋込み絶縁膜が埋め込まれてなる素子分離領域2と、素子分離領域2によって区画されてなり、素子分離用の溝を区画する側壁面と半導体基板の1一面とを有し、かつ側壁面には埋込み絶縁膜に向けて突出した半導体線条突出部1aが素子分離用の溝に沿って設けられてなる活性領域Tと、半導体線条突出部1aを残して活性領域Tを分断するように設けられたゲート電極用のゲート溝3と、ゲート溝3の内面に形成されたゲート絶縁膜4と、ゲート溝3に埋め込まれたゲート電極5と、ゲート電極5のゲート長方向両側の活性領域Tにそれぞれ形成され、半導体線条突出部1aによって連結される不純物拡散領域7と、を具備してなることを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の優れたトランジスタを作製する。

【解決手段】基板上に酸化物絶縁膜を形成し、該酸化物絶縁膜上に酸化物半導体膜を形成した後、酸化物半導体膜に含まれる水素を除去させつつ、酸化物絶縁膜に含まれる酸素の一部を脱離させる温度で加熱した後、該加熱された酸化物半導体膜を所定の形状にエッチングして島状の酸化物半導体膜を形成し、島状の酸化物半導体膜上に一対の電極を形成し、該一対の電極及び島状の酸化物半導膜上にゲート絶縁膜を形成し、該ゲート絶縁膜上にゲート電極を形成する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】集積回路のコア部のロジックトランジスタ(MOSFET、MISFET)は、世代が進むごとに動作電圧をスケーリングすることで微細化が可能である。しかし、高耐圧部のトランジスタ(MOSFET、MISFET)は比較的高い電源電圧で動作するために縮小化が困難であり、同様に電源セル内の静電気放電(ESD)保護回路は、静電気(外来サージ)から半導体集積回路内の素子を保護するために耐圧が高いことが必須であり、電荷を逃がすために大面積である必要がある。従って、集積回路の微細化のためには、微細化が可能なトランジスタ構造が必須である。

【解決手段】本願発明は、ソース側にのみハロー領域を有するソースドレイン非対称構造の一対のMISFETから構成されたCMISインバータをESD保護回路部に有する半導体集積回路装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI基板上に形成されたメサ分離構造のMOSトランジスタのトランジスタ特性のバラツキを低減する。

【解決手段】MOSトランジスタは、埋込み酸化膜3上に形成されたメサ型SOI層5と、メサ型SOI層5の上面中央部の上に形成されたゲート酸化膜7と、メサ型SOI層5の上面端部の上にゲート酸化膜7よりも厚い膜厚で形成された第1シリコン酸化膜9と、メサ型SOI層5の側面に第2シリコン酸化膜11を介して形成されたシリコン窒化膜からなる側壁膜13と、ゲート酸化膜7上に形成されたゲート電極15を備えている。

(もっと読む)

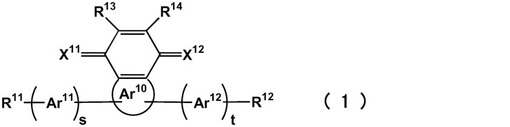

縮合環化合物、有機薄膜及び有機薄膜素子

【課題】優れた電子輸送性を有するとともに、溶媒への溶解性にも優れる有機n型半導体として利用可能な縮合環化合物の提供。

【解決手段】式(1)で表される縮合環化合物。 (もっと読む)

(もっと読む)

発光装置

【課題】画質が明るく安価な発光装置およびそれを用いた電気器具を提供する。

【解決手段】同一の絶縁体上に画素部および駆動回路を含む発光装置において、画素部および駆動回路は全てnチャネル型の半導体素子で形成され、製造工程が簡略化されている。また、画素部に設けられた発光素子は、絶縁体から遠ざかる方向に放射されるため、ほぼ画素電極(EL素子の陰極に相当する)全体が有効発光領域となる、従って、画素電極の面積を有効に活用した表示領域とすることができ、画質が明るく安価な発光装置が得られる。

(もっと読む)

41 - 60 / 286

[ Back to top ]