Fターム[5F110FF35]の内容

Fターム[5F110FF35]に分類される特許

101 - 120 / 286

半導体装置及び半導体装置の作製方法

【課題】安定した電気的特性を有する酸化物半導体を用いた半導体装置を提供することを目的の一つとする。

【解決手段】フッ素や塩素に代表されるハロゲン元素により、酸化物半導体層に含まれる水素や水分(水素原子や、H2Oなど水素原子を含む化合物)などの不純物を、酸化物半導体層より排除し、上記酸化物半導体層中の不純物濃度を低減する。ハロゲン元素は酸化物半導体層と接して設けられるゲート絶縁層及び/又は絶縁層に含ませて形成することができ、またハロゲン元素を含むガス雰囲気下でのプラズマ処理によって酸化物半導体層に付着させてもよい。

(もっと読む)

論理回路及び半導体装置

【課題】トランジスタのリーク電流を低減し、論理回路の誤動作を抑制する。

【解決手段】チャネル形成層としての機能を有する酸化物半導体層を含み、チャネル幅1μmあたりのオフ電流が1×10−13A以下であるトランジスタを有し、入力信号として、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力された第1の信号乃至第3の信号に応じて電圧状態が設定された第4の信号及び第5の信号を出力信号として出力する構成とする。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】安定した電気的特性を有する酸化物半導体を用いた半導体装置を提供することを目的の一つとする。

【解決手段】未結合手に代表される欠陥を多く含む酸化シリコン層を、酸化物半導体層に接して形成し、酸化物半導体層に含まれる水素や水分(水素原子や、H2Oなど水素原子を含む化合物)などの不純物を、上記酸化シリコン層に拡散させ、上記酸化物半導体層中の不純物濃度を低減する。また、酸化物半導体層と酸化シリコン層の界面に混合領域を設ける。

(もっと読む)

半導体装置

【課題】安定した電気的特性を有する酸化物半導体を用いた半導体装置を提供することを目的の一つとする。

【解決手段】ゲート電極層と、ゲート電極層上の膜厚100nm以上350nm以下のゲート絶縁層と、ゲート絶縁層上の酸化物半導体層と、酸化物半導体層上のソース電極層及びドレイン電極層と、酸化物半導体層を含む薄膜トランジスタと、ソース電極層及びドレイン電極層上に酸化物半導体層の一部と接する酸化シリコン層とを有し、薄膜トランジスタは温度85℃で、12時間、ゲート電極層に30V、又は−30Vの電圧を印加する測定において、測定前と測定後の薄膜トランジスタのしきい値電圧の値の差が1V以下である半導体装置とする。

(もっと読む)

自己整列グラフェン・トランジスタ

【課題】自己整列グラフェン・トランジスタを作製するスキームを提供する。

【解決手段】グラフェン電界効果トランジスタは、ゲート・スタックであってシード層とシード層の上に形成されたゲート酸化物とゲート酸化物の上に形成されたゲート金属とを含む該ゲート・スタック、絶縁層、およびシード層と絶縁層との間に転写されたグラフェン・シート、を含む。

(もっと読む)

薄膜トランジスタ

【課題】ポリスチレンを塗布プロセスにより形成し不溶化処理を行うことで、半導体層を塗布プロセスで積層可能なポリスチレンからなる絶縁体層を有し、応答速度(駆動速度)が早く、オン/オフ比が大きい、優れたトランジスタ特性を有する薄膜トランジスタを提供する。

【解決手段】少なくとも基板上にゲート電極、ソース電極及びドレイン電極の3端子、絶縁体層並びに半導体層が設けられ、ソース−ドレイン間電流をゲート電極に電圧を印加することによって制御する薄膜トランジスタにおいて、前記絶縁体層が、塗布法により積層された層であって、有機溶媒に対して不溶化したポリスチレンからなる薄膜トランジスタ。

(もっと読む)

半導体装置の作製方法

【課題】半導体膜への不純物の拡散を抑えつつ、歩留まりの低下を抑えることができるSOI基板の作製方法を提供することを、目的の一とする。

【解決手段】半導体基板の表面を熱酸化させることで、酸化膜が形成された半導体基板を形成する。そして、窒素原子を有するガス雰囲気下においてプラズマを発生させることにより、上記酸化膜の一部をプラズマ窒化させ、酸化膜上に窒素原子を含む絶縁膜が形成された半導体基板を得る。そして、窒素原子を含む絶縁膜とガラス基板を接合させた後、半導体基板を分離することで、ガラス基板上に窒素原子を含む絶縁膜、酸化膜、薄膜の半導体膜が順に積層されたSOI基板を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】画素部の開口率を高くしながら、駆動回路部の特性を向上させた半導体装置を提供することを課題とする。または、消費電力の低い半導体装置を提供することを課題とする。または、しきい値電圧を制御できる半導体装置を提供することを課題とする。

【解決手段】絶縁面を有する基板と、基板上に設けられた画素部と、画素部を駆動する駆動回路の少なくとも一部を有し、画素部を構成するトランジスタおよび駆動回路を構成するトランジスタは、トップゲートボトムコンタクト型のトランジスタであって、画素部においては、電極および半導体層が透光性を有し、駆動回路における電極は、画素部のトランジスタが有するいずれの電極よりも低抵抗である半導体装置である。

(もっと読む)

半導体基板、半導体装置及び半導体装置の製造方法

【課題】半導体層の界面に生じるダングリングボンドをフッ素で終端することで、界面準位を低減することができ、また、低熱履歴のプロセスでも活性領域のみへ効率よくフッ素を導入することができる半導体基板を提供する。

【解決手段】フッ素拡散防止膜6と該フッ素拡散防止膜6上に形成されたフッ素を含有するシリコン酸化膜7からなる絶縁層9と、前記絶縁層9上に形成された半導体層8と、を含み、前記半導体層8とフッ素を含有する前記シリコン酸化膜7とが接触していることを特徴とする。

(もっと読む)

エンハンスメント型窒化ガリウム高電子移動度トランジスタ

実施形態には、これに限定されないが、第1バリア層と、該第1バリア層上の窒化ガリウムチャネル層と、該窒化ガリウムチャネル層上に存在し、第1サブレイヤーと第2サブレイヤーと第3サブレイヤーとを備える第2バリア層と、を有するヘテロ構造を備える装置とシステムが含まれる。該第1バリア層、第1サブレイヤーおよび第3サブレイヤーは各々アルミニウムを含んでいてもよい。他の実施形態も、本明細書に記載され特許請求される。 (もっと読む)

半導体装置

【課題】半導体装置の表示領域と駆動回路に設けられたTFTの構造を機能に応じて適切なものとするとき、pチャネル型TFTにおいて、チャネル形成領域と、不純物領域との接合に欠陥が形成され、オフ電流が増加することを防止する。

【解決手段】表示領域に第1のnチャネル型TFTが配置され、駆動回路に第2のnチャネル型TFT及びpチャネル型TFTが配置された半導体装置であって、pチャネル型TFTはチャネル形成領域と、これに隣接した不純物領域を有し、不純物領域にはnチャネル型TFTのために添加された不純物元素を含ませない。そのために、pチャネル型TFTのチャネル長はnチャネル型TFTのチャネル長より短くなる。

(もっと読む)

III−V族加工基板の製造方法およびそのIII−V族加工基板

【課題】パッシベーション層を備え、改善した性能を持つデバイスを実現できるIII−V族加工基板およびその製造方法を提供する。

【解決手段】III−V族加工基板の製造方法は、<110>または<111>の結晶方位を持つ第1のIII−V化合物からなる上側層(2)を備えたベース基板(I)を用意すること、第2のIII−V化合物からなるバッファ層(3)を少なくとも形成することを含んだ、中間層(II)を形成することであって、中間層(II)は、ベース基板の上側層(2)の上に位置し、これと接触するようにすること、IV族半導体材料からなる擬似格子整合パッシベーション層(4)を成長させることであって、擬似格子整合パッシベーション層は、中間層(II)の上に位置し、これと接触するようにすることを含む。

(もっと読む)

SOI基板の作製方法

【課題】単結晶シリコン基板よりも大面積な基板に、均一な質を有する複数の単結晶半導体層を貼り付けたSOI基板の作製方法を提供することを課題とする。

【解決手段】熱処理において、ベース基板支持及び単結晶半導体基板保持のトレイとして、凹部の底が深く、ベース基板に貼り付けられた単結晶半導体基板と接触しないトレイを用いて、単結晶半導体基板の熱分布の均一化を図る。また、該トレイの各々の凹部の間にベース基板支持部を設けることによって、該トレイとベース基板との接触面積を低減する。以上より、単結晶半導体基板から単結晶半導体層を分離する熱処理の際、単結晶半導体基板及びベース基板の熱分布が均一になるようにする。

(もっと読む)

半導体装置の作製方法

【課題】TFTを用いた半導体装置において、TFT中の汚染不純物を低減し、信頼性のあるTFTを得ることを課題とする。

【解決手段】ガラス基板上のTFTの被膜に存在する汚染不純物を、フッ素を含有する酸性溶液を被膜表面に接触させ、酸性溶液を一定方向に流すことにより、被膜表面の汚染不純物を除去することにより、信頼性のあるTFTを得ることができる。なお、酸性溶液は、フッ酸とフッ化アンモニウムの混合比が体積比で1:50のバッファードフッ酸を用いる。

(もっと読む)

成膜方法、ゲート電極構造の形成方法及び処理装置

【課題】シリコン層の表面をケミカル酸化膜で保護した状態で低酸素分圧酸化を行うことにより、膜厚の面内均一性が高くて且つ欠陥の少ない極めて薄い界面酸化膜を得ることが可能な成膜方法を提供する。

【解決手段】被処理体Wのシリコン層の表面に、ゲート絶縁膜との間に介在される界面酸化層を形成する成膜方法において、シリコン層をケミカル洗浄処理することによってケミカル酸化膜を形成するケミカル酸化膜形成工程と、ケミカル酸化膜の形成された被処理体に対して酸素分圧が0.2〜2Paの範囲内の雰囲気中で熱処理を施すことにより界面酸化膜を形成する熱処理工程とを有する。これにより、シリコン層の表面をケミカル酸化膜で保護した状態で低酸素分圧酸化を行うことで、膜厚の面内均一性が高くて且つ欠陥の少ない極めて薄い界面酸化膜を得る。

(もっと読む)

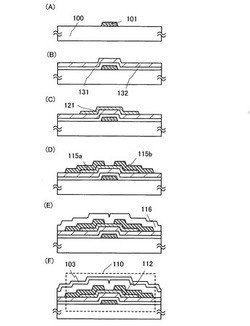

光マトリックスデバイスの製造方法

【課題】

薄膜トランジスタのソース・ドレイン間のON抵抗を低下することができる光マトリックスデバイスの製造方法を提供する。

【解決手段】

凹凸パターンが形成された転写型に真空中にて半導体膜6を形成し、半導体膜6が形成された転写型に真空中にて連続してゲート絶縁膜7を形成する。そして、基板1上に予め形成されたゲート線2上に接着用樹脂4を介して前記ゲート絶縁膜7および前記半導体膜6を転写する。そして、基板1上に転写された前記半導体膜6に水素イオンをドープする処理を行う。それにより、半導体膜6の抵抗率を低下させることができるので、薄膜トランジスタのゲートがON状態のときのソース・ドレイン間の接続抵抗を低下させることができる。

(もっと読む)

薄膜トランジスタアレイ基板、及びその製造方法、並びに液晶表示装置

【課題】液晶分子を駆動するための画素電極と共通電極が、平面視上、重畳領域を有するTFTアレイ基板において、製造工程の短縮化を実現する。

【解決手段】本発明に係るTFTアレイ基板は、ドレイン領域10Dから延在される画素電極11を備える島状の結晶性半導体層3と、結晶性半導体層3の上層に形成されたゲート絶縁膜21と、ゲート絶縁膜上21であって、チャネル領域10Cと対向配置されるゲート電極12と、ゲート電極12より上層に配置され、絶縁層25に形成されたコンタクトホールCHを介してソース領域10Sと電気的に接続されたソース電極13と、絶縁層25より上層に形成され、画素電極11と重畳する領域を有する共通電極14とを備える。

(もっと読む)

薄膜半導体装置、電気光学装置、および電子機器

【課題】各画素にN型とP型の2つの薄膜トランジスターを形成配置することによって、コンタクトホールの形成数が2つから4つに増え、薄膜トランジスターの平面的な占有面積が大きくなってしまう。

【解決手段】N型薄膜トランジスターNTのドレイン領域NDとP型薄膜トランジスターPTのドレイン領域PDとが部分的に隣接するように、また、N型薄膜トランジスターNTのソース領域NSとP型薄膜トランジスターPTのソース領域PSとが部分的に隣接するように、それぞれ配置されている。ドレイン領域NDとドレイン領域PDとの隣接部分に1つのコンタクトホール121が形成されて、ドレイン領域NDとドレイン領域PDとが、同時に信号線12と電気的に接続されている。ソース領域NSとソース領域PSとの隣接部分には、1つのコンタクトホール291が形成されて、ソース領域NSとソース領域PSとが、同時に容量電極29と接続されている。

(もっと読む)

電界効果トランジスタ

【課題】 ノーマリーオフ動作、高耐圧、大電流を実現する電界効果トランジスタを提供する。

【解決手段】 電界効果トランジスタの下面または上面にボディ電極8を設ける。下面にボディ電極8を設ける場合、p型Si基板2上にAlN層31およびGaN層32の繰り返しによるバッファ層3を介してp−GaN層4を設け、バッファ層3の最上層のAlN層31を薄くし、p型Si基板の下面にボディ電極8を形成する。上面にボディ電極8を設ける場合、サファイア基板21上にp−GaN層4を設け、ソース電極5およびドレイン電極6下の部分にAlGaN層13を設け、AlGaN層13上にボディ電極8を設ける。アバランシェにより生じる正孔20をボディ電極8より引き抜く。

(もっと読む)

有機薄膜トランジスタ

【課題】塗工や印刷等の簡便なプロセスで製造でき、再現性のよい特性が得られる有機薄膜トランジスタを提供する。

【解決手段】有機半導体層を具備する有機薄膜トランジスタであって、前記有機半導体層が下記一般式(I)で示される繰り返し単位を有する重合体を主成分とすることを特徴とする有機薄膜トランジスタ。

(式中、Ar2およびAr3は、置換もしくは無置換の芳香族炭化水素基の2価基であり、Ar1は置換もしくは無置換の1価の芳香族炭化水素基を表す。R1、R2およびR3は、それぞれ独立に、置換もしくは無置換のアルキル基、置換もしくは無置換のアルコキシ基、または置換もしくは無置換のアルキルチオ基から選択された基を表し、同一でも別異でもよく、x、yおよびzは、それぞれ0から2までの整数を表し、同一でも別異でもよく、nは1以上の整数を表わす。)

(もっと読む)

101 - 120 / 286

[ Back to top ]