Fターム[5F110HM02]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | 形状 (2,461) | 断面形状 (1,337)

Fターム[5F110HM02]の下位に属するFターム

テーパ状 (428)

Fターム[5F110HM02]に分類される特許

901 - 909 / 909

減少されたゲート高さを有するトランジスタを製造する方法

【課題】減少されたゲート高さを有する集積回路トランジスタを形成する方法およびシステムを開示すること。

【解決手段】本方法は、基板、基板の上のゲート導体(13)、およびゲート導体(13)の上の少なくとも1つの犠牲層(14〜16)を有する積層構造を形成する。このプロセスは、積層構造を基板から延びる少なくとも1つのゲート・スタックにパターン形成し、ゲート・スタックに隣接してスペーサ(60)を形成し、ゲート・スタックに隣接してソースおよびドレイン領域(71)を形成するようにスペーサで保護されていない基板の領域にドーピングし、そして、スペーサ(60)および犠牲層(14〜16)を除去する。

(もっと読む)

高解像度構造を有する有機電子部品及びその生産方法

【課題】本発明は、高解像度構造を有する有機電子部品、特に低ソースドレーン間の距離を有する有機電界効果トランジスタ(OFET)及びその生産方法に関する。

【解決手段】有機電子部品は、生産中レーザーを用いて作られた凹部及び/又は修正された区域を有し、その中には、例えば、金属の導体トラック/電極が配置される。

(もっと読む)

半導体装置及びその製造方法

基体平面に対して突出した半導体凸部と、この半導体凸部を跨ぐようにその上面から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体凸部の間に介在する絶縁膜と、ソース/ドレイン領域とを有するMIS型電界効果トランジスタを備えた半導体装置であって、1つのチップ内に、前記MIS型電界効果トランジスタとして、ゲート電極下の前記半導体凸部における基板平面に平行かつチャネル長方向に垂直な方向の幅Wが互いに異なる複数種のトランジスタを有する半導体装置。 (もっと読む)

線状素子

柔軟性、可撓性があり任意の形状に集積回路を作成できるという特徴を持つ線状MISFETでは、ソース領域とドレイン領域を並列配置する構造が使用されていた。しかし、MISFETの電気特性を決めるチャネル長が円筒形のゲート絶縁領域に沿ったソース領域とドレイン領域の距離できまるため、チャネル長の微細化や再現性向上が困難だった。 MISFETの構造を、ソース領域とドレイン領域でチャネル領域となる半導体領域を挟む構造とした。半導体領域にゲート絶縁領域を介して制御電圧を加え、ソース領域とドレイン領域間で流れる電流を制御する。チャネル長が、半導体領域の膜厚で決まるため、チャネル長の微細化や再現性向上が可能になった。 (もっと読む)

格子不整合のソースおよびドレイン領域を有する歪み半導体CMOSトランジスタを有する集積回路および製作方法

【課題】 p型電界効果トランジスタ(PFET)およびn型電界効果トランジスタ(NFET)を有する集積回路を提供することにある。

【解決手段】 第1の歪みは、NFETではなくPFETのみのソースおよびドレイン領域内に配置されたシリコン・ゲルマニウムなどの格子不整合半導体層を介してNFETではなくPFETのチャネル領域に加えられる。PFETおよびNFETを形成するプロセスが提供される。PFETのソースおよびドレイン領域になるためのエリア内にトレンチがエッチングされ、それに隣接するPFETのチャネル領域に歪みを加えるために、格子不整合シリコン・ゲルマニウム層をそこにエピタキシャル成長させる。シリコン・ゲルマニウム層の上にシリコンの層を成長させ、シリコンの層からサリサイドを形成して、低抵抗ソースおよびドレイン領域を提供することができる。

(もっと読む)

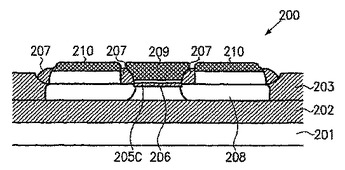

ゲートの枯渇を低減した注入ゲート電極を有する電界効果型トランジスタ、及び、このトランジスタを製造する方法

ドレイン領域及びソース領域(208)を規定する前に、注入マスク(220)を形成することにより、ゲートドーパント密度をドレインドーパント密度及びゲートドーパント密度から効果的に分離する。さらに、注入マスク(220)を除去した後に、ゲート電極(205)の横方向寸法は、十分に確立された側壁スペーサ(207)技術によって規定される。その結果、フォトリソグラフィ及び異方性エッチングに基づく従来の方法に対してデバイスの縮小に関する優位性を提供する。  (もっと読む)

(もっと読む)

半導体デバイスおよびその製造方法

集積回路での使用に適した歪み半導体デバイスおよび歪み半導体デバイスの製造方法。半導体−オン−インシュレータ基板からメサ分離構造が形成される。このメサ分離構造にゲート構造が形成される。このゲート構造は、ゲート絶縁材料に配置されたゲートと、対向する2組の側壁を有する。ゲート構造の対向する第1の組の側壁に隣接するメサ分離構造の一部に、半導体材料が選択的に成長され、ドープが行われる。ドープされた半導体材料がシリサイド化されて、絶縁材料によって保護される。ゲートがシリサイド化され、このシリサイドが、対向する第2の組の側壁を覆っており、チャネル領域に応力を付与する。  (もっと読む)

(もっと読む)

表示装置及びその作製方法

【課題】 配線抵抗による電圧降下の影響や画素への信号の書き込み不良や階調不良などを防止し、より高画質のEL表示装置や液晶表示装置を代表とする表示装置を提供することを課題とする。

【解決手段】 本発明はEL表示装置や液晶表示装置を代表とする表示装置に用いられる電極や配線として、Cuを有する配線を設ける。また、該配線のCuを主成分とする導電膜は、マスクを用いたスパッタ法により形成する。このような構成により、電圧降下や信号のなまりを低減することができる。

(もっと読む)

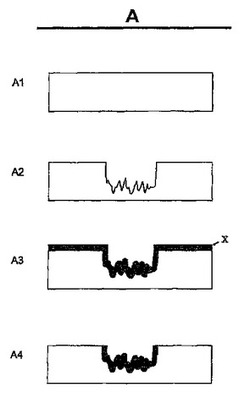

反射電極を形成する方法及び液晶表示装置

【課題】TFTと凹部又は凸部を有する反射電極とを形成する方法であって、製造工程数及び製造コストの削減が図られた方法、及びこの方法が適用された液晶表示装置を提供する。

【解決手段】 金属膜7の上に感光性膜8を形成し、この感光性膜8から残部81、82及び83を形成し、この残部81、82及び83をマスクとして金属膜7をエッチングし、この残部81、82及び83を剥離せずに感光性膜9及び反射電極膜10を形成する。

(もっと読む)

901 - 909 / 909

[ Back to top ]