Fターム[5F110PP15]の内容

Fターム[5F110PP15]に分類される特許

1 - 20 / 21

半導体装置、薄膜トランジスタ基板および表示装置

【課題】金属酸化物を用いた絶縁膜を低温プロセスで結晶化することが可能で、これによりガラス基板やプラスチック基板上に特性の向上が図られた素子を設けることが可能な半導体装置を提供する。

【解決手段】基板上に、金属酸化物を用いた絶縁膜と半導体薄膜とが積層形成された半導体装置であって、絶縁膜はゲート絶縁膜として用いられ、ゲート絶縁膜に接する側にゲート電極が積層形成され、絶縁膜および半導体薄膜は結晶化され、かつ、ゲート電極と重なる部分の結晶性が他の部分の結晶性よりも高いものである。

(もっと読む)

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

半導体装置、表示モジュール、及び電子機器

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

基板上のフィルム領域を処理して、こうした領域内及びその端部領域をほぼ均一にするレーザ結晶化プロセス及びシステム、及びこうしたフィルム領域の構造

【課題】薄膜フィルム試料を処理するシステム、並びに薄膜フィルム構造を提供する。

【解決手段】フィルム試料170の一区画の特定部分の第1部分を融解させるべく照射ビームパルスの第1パルスの第1小ビームで照射して、この第1部分が少なくとも部分的に融解して自ずと再凝固して結晶化し、それぞれの隣接する第1部分どうしの間に第1未照射部分が残る。特定部分の第1小ビームによる照射の後に、この特定部分を、この特定部分の第2部分を融解させるべく照射ビームパルスの第2パルスの第2小ビームで再び照射して、この第2部分が少なくとも部分的に融解して自ずと再凝固して結晶化し、それぞれの隣接する第2部分どうしの間に第2未照射部分が残る。再凝固して結晶化した第1部分及び前記第2部分は、フィルム試料の領域内で互いに間に入り合う。これに加えて、第1部分が第1画素に対応し、第2部分が第2画素に対応する。

(もっと読む)

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成することで、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少なくとも結晶化した領域を有する。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】バックチャネル部の表面のアルミニウム汚染に起因する漏れ電流を抑制を防止でき、高い信頼性と、高い歩留を実現できる構造の薄膜トランジスタを提供することを目的とする。

【解決手段】この発明に係る薄膜トランジスタは、シリコンを半導体層とするバックチャネル部を有するボトムゲート構造の薄膜トランジスタであって、アルミニウムを含むソース電極またはドレイン電極と、バックチャネル部の一部であって半導体層の表層を覆うサイアロン化合物の層とを有するものである。

(もっと読む)

半導体装置の作製方法

【課題】金属元素を用いた結晶化法において、ゲッタリングのために必要な不純物元素の濃度が高く、その後のアニールによる再結晶化の妨げとなり問題となっている。

【解決手段】

本発明は半導体膜に、希ガス元素を添加した不純物領域を形成し、加熱処理およびレーザアニールにより前記不純物領域に半導体膜に含まれる金属元素を偏析させるゲッタリングを行なうことを特徴としている。そして、半導体膜が形成された基板(半導体膜基板)の上方または下方からレーザ光を照射してゲート電極を加熱し、その熱によってゲート電極の一部と重なる不純物領域を加熱する。このようにして、ゲート電極の一部と重なる不純物領域の結晶性の回復および不純物元素の活性化を行なうことを可能とする。

(もっと読む)

薄膜トランジスタとその製造方法と電気光学装置と電子機器

【課題】 非晶質シリコンTFTの特性を大幅に向上させつつ、その製造プロセスにおける膜飛びを抑制する。

【解決手段】まず、基板10上にゲート電極11を形成する。次に、基板10上に、ゲート電極11を平面視で覆うゲート絶縁膜12を形成し、その上に、チャネル領域13cとソース領域13sとドレイン領域13dとを有する非晶質の半導体膜13を形成し、その上に、チャネル領域13cを平面視で覆うチャネル保護層14を形成する。次に、半導体膜13とチャネル保護層14とにレーザーを照射することにより、チャネル領域13cを微結晶化する。次に、半導体膜13上に、チャネル保護層14を平面視で覆い、ソース領域13sとドレイン領域13dとに平面視で重なる導電膜を形成する。次に、導電膜をエッチングしてソース電極16sとドレイン電極16dとを形成する。

(もっと読む)

非晶質半導体膜の結晶化方法、薄膜トランジスタ、半導体装置、及び薄膜トランジスタの製造方法

【課題】特性の優れた半導体膜を簡便に得ることができる微結晶半導体膜の結晶化方法と、これを応用した薄膜トランジスタ、半導体装置、及び薄膜トランジスタの製造方法を提供すること。

【解決手段】本発明にかかる薄膜トランジスタは、基板1上に形成されたゲート電極2と、ゲート電極2を覆うゲート絶縁膜3と、ゲート絶縁膜3を介してゲート電極2の対面に形成され、ソース領域となる第1非晶質領域41、ドレイン領域となる第2非晶質領域42、及び第1非晶質領域41と第2非晶質領域42との間に配置されたチャネル領域となる結晶性領域43を有する半導体膜4と、半導体膜4上に結晶性領域43と直接接触することなく形成され、ソース領域及びドレイン領域とそれぞれ電気的に接続されたソース電極81及びドレイン電極82と、を備えるものである。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】製造工程を簡略化しつつソース電極及びドレイン電極の導電性を向上させた薄膜トランジスタ及びその製造方法を提供する。

【解決手段】本発明の薄膜トランジスタの製造方法は、基板101上にゲート電極103を形成する工程と、ゲート電極103上にゲート絶縁層104を形成する工程と、ゲート絶縁層104上にアモルファスシリコン層105を形成する工程と、アモルファスシリコン層105上にアルミニウム層111を形成し、アルミニウム層111上にモリブデンタングステン層112を形成し、アルミニウム層111及びモリブデンタングステン層112を少なくとも含む積層体から構成されるソース電極109及びドレイン電極110を形成する工程と、ソース電極109及びドレイン電極110をマスクとしアモルファスシリコン層105にレーザを照射することでアモルファスシリコン層105の一部を結晶化させチャネル領域を形成する工程とを含む。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】薄膜トランジスタにおけるオン電流の向上とリーク電流の低減を図る。

【解決手段】微結晶シリコン領域51の両端側が非晶質シリコン領域52となっている半導体膜5bを備えるスイッチトランジスタ5において、チャネル保護膜5dが、半導体膜5bにおける微結晶シリコン領域51を覆いつつ、そのチャネル保護膜5dの両端側で、微結晶シリコン領域51側の非晶質シリコン領域52の一部を覆い、また、ソース・ドレイン領域となる不純物半導体膜5f,5gが、微結晶シリコン領域51と直接接触せず、半導体膜5bにおける非晶質シリコン領域52と接することで、ドレイン電極5hとソース電極5iとが不純物半導体膜5f,5gを介して半導体膜5bと電気的に接続することで、微結晶シリコンに起因するホールエレクトロンペアの発生を抑えて、リーク電流の低減を図った。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】オフリーク電流が低減した薄膜トランジスタを提供する。

【解決手段】本発明に係るシリコン薄膜トランジスタ10は、絶縁性基板7上に形成されたゲート電極1と、ゲート電極1を覆うように形成された絶縁膜2と、絶縁膜2上に形成された半導体層30であって、絶縁膜2を介してゲート電極1上にチャネル領域33を有する半導体層30と、チャネル領域33を挟むように、チャネル領域33の周囲に形成されたソース電極51、52およびドレイン電極61、62とを備えており、チャネル領域33は、微結晶シリコン領域32と、微結晶シリコン領域32よりも高抵抗であるアモルファスシリコン領域31とに分かれており、微結晶シリコン領域32とアモルファスシリコン領域31とがチャネル長方向に交互に並んでいる。

(もっと読む)

薄膜トランジスタおよび表示装置

【課題】サイズの大型化を抑制しつつ必要な電流を得ることの可能な薄膜トランジスタおよびこれを用いた表示装置を提供する。

【解決手段】薄膜トランジスタ1は、基板10上にゲート電極11およびゲート絶縁膜12を介してシリコン膜13を有している。シリコン膜13のゲート電極11に対応する領域には絶縁保護膜14が形成され、絶縁保護膜14の上面両端からシリコン膜13上にかけて、非晶質シリコン膜(ソース領域)15Aおよび非晶質シリコン膜(ドレイン領域)15Bが形成され、それぞれソース電極16Aおよびドレイン電極16Bにより覆われている。シリコン膜13はチャネル領域13Cを有し、このチャネル領域13Cにおいて長さ方向に沿って結晶化領域13Bおよび非結晶領域13Aが形成されている。結晶化領域13Bの幅d1が調整されることにより、必要電流が得られる。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタアレイ基板、及びそれらの製造方法、並びに表示装置

【課題】歩留まり向上が可能で、かつ品質向上につながる薄膜トランジスタ、薄膜トランジスタアレイ基板、及びそれらの製造方法、並びに表示装置を提供すること。

【解決手段】本発明に係る薄膜トランジスタの製造方法は、基板1上にゲート電極2を形成する工程と、ゲート電極2上にゲート絶縁膜3を形成する工程と、ゲート絶縁膜3上に、ゲート電極2の少なくとも一部と対向配置する半導体層10のパターン形成する工程と、半導体層10上にソース電極5、及びドレイン電極6を形成する工程と、ソース電極5、及びドレイン電極6をマスクとして、チャネル領域10Cに相当する半導体層10を所望の膜厚までエッチングする工程と、露出した半導体層10にレーザ光を照射する工程とを備える。

(もっと読む)

表示装置及び表示装置の作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する表示装置、及び該表示装置を量産高く作製する方法を提案することを課題とする。

【解決手段】チャネルストップ型の逆スタガ型薄膜トランジスタを有する表示装置において、該チャネルストップ型の逆スタガ型薄膜トランジスタは、チャネル形成領域を含む微結晶半導体膜を有し、該微結晶半導体膜のチャネル形成領域には、ソース電極及びドレイン電極と重ならない領域に選択的に一導電型を付与する不純物元素を含む不純物領域が設けられている。チャネル形成領域において該不純物元素の添加領域である不純物領域とソース領域及びドレイン領域との間には、該一導電型を付与する不純物元素の非添加領域が設けられている。

(もっと読む)

表示装置及び表示装置の作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する表示装置、及び該表示装置を量産高く作製する方法を提案することを課題とする。

【解決手段】チャネルストップ型の逆スタガ型薄膜トランジスタを有する表示装置において、該チャネルストップ型の逆スタガ型薄膜トランジスタは、チャネル形成領域を含む微結晶半導体膜を有し、該微結晶半導体膜のチャネル形成領域には、ソース電極及びドレイン電極と重ならない領域に選択的に一導電型の不純物元素を含む不純物領域が設けられている。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成することで、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置及びその作製方法を提供することを目的とする。

【解決手段】基板上に設けられたゲート電極と、ゲート電極上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられた酸化物半導体膜と、を備えるトランジスタを有し、酸化物半導体膜の少なくともチャネル形成領域となる領域に対して加熱処理が行われている。

(もっと読む)

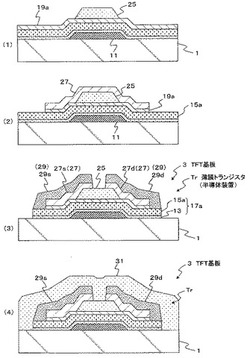

半導体装置の製造方法および半導体装置、薄膜トランジスタ基板の製造方法および薄膜トランジスタ基板、ならびに表示装置の製造方法および表示装置

【課題】金属酸化物を用いた絶縁膜を低温プロセスで結晶化することが可能で、これによりガラス基板やプラスチック基板上に特性の向上が図られた素子を設けることが可能な半導体装置の製造方法を提供する。

【解決手段】基板1上に、金属酸化膜15と非晶質シリコン膜19との積層体を成膜形成する。積層体の上部に光吸収層23を形成する。光吸収層23で吸収される波長のエネルギー線Lhを光吸収層23に対して照射し、光吸収層23で発生させた熱により非晶質シリコン膜19と金属酸化膜15とを同時に結晶化させる。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】 LSIを構成する微細な縦型電界効果型トランジスタ、特に半導体層の両側にゲート電極を有するダブルゲート縦型電界効果型トランジスタの製造方法として最適な縦型電界効果型トランジスタの製造方法を提供する。

【解決手段】 矩形断面を持つ半導体領域を跨ぐように、ゲート絶縁膜を介してゲート電極5を設け、続いてゲート電極5のうち、少なくとも前記略矩形の断面を持つ半導体領域の上端よりも低い位置を絶縁膜で覆うとともに、前記略矩形の断面を持つ半導体の側面のうちゲート電極に覆われない領域の少なくとも一部を露出させ、前記露出した前記略矩形の断面を持つ半導体の側面に、半導体を選択的に成長させ、選択成長と同時または選択成長後に選択的に成長させた前記半導体に不純物を導入することにより、選択的に成長させた前記半導体をソース/ドレイン領域もしくはソース/ドレインエクステンション領域となす

(もっと読む)

1 - 20 / 21

[ Back to top ]