Fターム[5F110PP29]の内容

Fターム[5F110PP29]に分類される特許

41 - 60 / 599

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域の側面に接した一対の第2の領域と、一対の第2

の領域の側面に接した一対の第3の領域と、を含む酸化物半導体膜と、酸化物半導体膜上

に設けられたゲート絶縁膜と、ゲート絶縁膜上に第1の領域と重畳した第1の電極と、を

有し、第1の領域は、CAAC酸化物半導体領域であり、一対の第2の領域及び一対の第

3の領域は、ドーパントを含む非晶質な酸化物半導体領域であり、一対の第3の領域のド

ーパント濃度は、一対の第2の領域のドーパント濃度より高い半導体装置である。

(もっと読む)

部材の作製方法

【課題】本発明の一態様は、スパッタ法でトランジスタ、ダイオード等の半導体用途に好

適な材料を提供することを課題の一とする。

【解決手段】下地部材上に、第1の酸化物部材を形成し、第1の加熱処理を行って表面か

ら内部に向かって結晶成長し、下地部材に少なくとも一部接する第1の酸化物結晶部材を

形成し、第1の酸化物結晶部材上に第2の酸化物部材を形成し、第2の加熱処理を行って

第1の酸化物結晶部材を種として結晶成長させて第2の酸化物結晶部材を設ける積層酸化

物材料の作製方法である。

(もっと読む)

表示装置

【課題】簡便な構成及び動作によって表示装置の消費電力を低減すること。

【解決手段】表示装置が入力デバイスを備え、該入力デバイスから出力される画像操作信号に応じて、駆動回路に対する画像信号の入力を制御する。具体的には、入力デバイスが操作されない際の画像信号の入力頻度を、入力デバイスが操作される際の画像信号の入力頻度よりも低くする。これにより、当該表示装置が使用される際の表示の劣化(表示品質の低下)を抑制することが可能となり、且つ使用されない際の消費電力を低減することが可能になる。

(もっと読む)

半導体素子の作製方法

【課題】閾値電圧が制御され、動作速度が速く、製造工程が比較的簡単であり、十分な信

頼性を有する、酸化物半導体を用いた薄膜トランジスタ、及び薄膜トランジスタの作製方

法を提供することを課題の一つとする。

【解決手段】酸化物半導体層に含まれるキャリア濃度に影響する不純物、例えば、水素原

子や、H2Oなど水素原子を含む化合物を排除すればよい。酸化物半導体層に接して未結

合手に代表される欠陥を多く含む酸化物絶縁層を形成し、当該酸化物絶縁層に不純物を拡

散させ、上記酸化物半導体層中の不純物濃度を低減すればよい。また、酸化物半導体層、

又は酸化物半導体層に接する酸化物絶縁層を、クライオポンプを用いて排気して不純物濃

度が低減された成膜室内で成膜すればよい。

(もっと読む)

半導体装置及び電子器具

【課題】 可撓性を有するアクティブマトリクス型表示装置を実現する方法を提供することを課題とする。また、異なる層に形成された配線間の寄生容量を低減する方法を提供することを課題とする。

【解決手段】 第1の基板上に形成された薄膜デバイスと第2の基板とを接着して固定した後、第1の基板を取り除いて薄膜デバイスに配線等を形成する。その後、第2の基板も取り除き、可撓性を有するアクティブマトリクス型表示装置を形成する。また、第1の基板を取り除いた後、配線を活性層のゲート電極が形成されていない側に形成することにより、寄生容量を低減することができる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体層を含むトランジスタの作製工程において、酸化シリコン膜上に、酸化物半導体が結晶状態における化学量論的組成比に対し、酸素の含有量が過剰な領域が含まれている非晶質酸化物半導体層を形成し、該非晶質酸化物半導体層上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体層の少なくとも一部を結晶化させて、表面に概略垂直なc軸を有している結晶を含む酸化物半導体層を形成する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

液晶表示装置

【課題】動作性能および信頼性の高い液晶表示装置を提供する。

【解決手段】トランジスタ上に第1の絶縁膜を有し、第1の絶縁膜上に第1及び第2の配線を有し、第1及び第2の配線上に第2の絶縁膜を有し、第2の絶縁膜上に電極を有し、電極上に第3の絶縁膜を有し、第3の絶縁膜上に画素電極を有し、画素電極は、電極と重なる第1の領域と、電極と重ならない第2の領域と、を有し、画素電極は、第1の配線に電気的に接続されており、第1の配線は、トランジスタのソース又はドレインの一方と電気的に接続されており、電極は、画素部の外側において前記第2の配線と電気的に接続されている。

(もっと読む)

半導体装置

【課題】小型化、薄型化、軽量化を実現した半導体装置の提供を課題とする。また、作製時間を短縮し、歩留まりを向上することができる半導体装置の作製方法の提供を課題とする。

【解決手段】トランジスタと、トランジスタ上に設けられた絶縁層と、絶縁層に設けられた開口部を介して、トランジスタのソース領域又はドレイン領域に電気的に接続された第1の導電層(ソース配線又はドレイン配線に相当)と、絶縁層及び第1の導電層上に設けられた第1の樹脂層と、第1の樹脂層に設けられた開口部を介して、第1の導電層に電気的に接続された導電性粒子を含む層と、第2の樹脂層及びアンテナとして機能する第2の導電層が設けられた基板とを有する。上記構成の半導体装置において、第2の導電層は、導電性粒子を含む層を介して、第1の導電層に電気的に接続されている。また、第2の樹脂層は、第1の樹脂層上に設けられている。

(もっと読む)

表示装置

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って歩留まりよく剥離することを可能とすることを目的としている。また、様々な基材に被剥離層を貼りつけ、軽量された半導体装置およびその作製方法を提供することを課題とする。特に、フレキシブルなフィルムにTFTを代表とする様々な素子を貼りつけ、軽量された半導体装置およびその作製方法を提供する。

【解決手段】基板上に第1の材料層11を設け、前記第1の材料層11に接して第2の材料層12を設け、さらに積層成膜または500℃以上の熱処理やレーザー光の照射処理を行っても、剥離前の第1の材料層が引張応力を有し、且つ第2の材料層が圧縮応力であれば、物理的手段で容易に第2の材料層12の層内または界面において、きれいに分離することができる。

(もっと読む)

半導体装置

【課題】同一の層間膜上に画素電極と、ゲート配線を形成した半導体装置において、マス

ク枚数を追加することなく、液晶の焼きつきや特性劣化を低減する。

【解決手段】ゲート配線上に絶縁膜を設けることで、ゲート配線が非選択の期間に液晶に

かかるゲート電圧の絶対値を減少させることができる。絶縁膜は遮光性樹脂膜、柱状スペ

ーサーで形成すると、マスク枚数の増加を抑えることができる。また、絶縁膜上に画素電

極を形成し、ゲート配線と画素電極が重なり合うようにすることで、画素電極の電界遮蔽

効果によって、液晶にかかるゲート電圧を減少させることができる。

(もっと読む)

記憶素子、記憶装置、信号処理回路、記憶素子の駆動方法

【課題】電源電圧の供給が停止した後もデータ保持可能な記憶素子を提供する。消費電力の低減可能な信号処理回路を提供する。

【解決手段】クロック信号に同期してデータを保持する記憶素子において、酸化物半導体層にチャネルが形成されるトランジスタ及び容量素子を用いることより、電源電圧の供給が停止した間もデータ保持ができる。ここで、電源電圧の供給を停止する前に、クロック信号のレベルを一定に保った状態で当該トランジスタをオフ状態とすることにより、データを正確に容量素子に保持させることができる。また、このような記憶素子を、CPU、メモリ、及び周辺制御装置のそれぞれに用いることによって、CPUを用いたシステム全体で、電源電圧の供給停止を可能とし、当該システム全体の消費電力を削減することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】基板上に第1の酸化絶縁膜を形成し、該第1の酸化絶縁膜上に第1の酸化物半導体膜を形成した後、加熱処理を行い、第1の酸化物半導体膜に含まれる水素を脱離させつつ、第1の酸化絶縁膜に含まれる酸素の一部を第1の酸化物半導体膜に拡散させ、水素濃度及び酸素欠陥を低減させた第2の酸化物半導体膜を形成する。次に、第2の酸化物半導体膜を選択的にエッチングして、第3の酸化物半導体膜を形成した後、第2の酸化絶縁膜を形成して、当該第2の酸化絶縁膜を選択的にエッチングして、第3の酸化物半導体膜の端部を覆う保護膜を形成する。この後、第3の酸化物半導体膜及び保護膜上に一対の電極、ゲート絶縁膜、及びゲート電極を形成する。

(もっと読む)

半導体装置

【課題】本発明は、曲面を有する基材に被剥離層を貼りつけた半導体装置およびその作製

方法を提供することを課題とする。特に、曲面を有するディスプレイ、具体的には曲面を

有する基材に貼りつけられたOLEDを有する発光装置、曲面を有する基材に貼りつけら

れた液晶表示装置の提供を課題とする。

【解決手段】本発明は、基板上に素子を含む被剥離層を形成する際、素子のチャネルとし

て機能する領域のチャネル長方向を全て同一方向に配置し、該チャネル長方向と同一方向

に走査するレーザー光の照射を行い、素子を完成させた後、さらに、前記チャネル長方向

と異なっている方向、即ちチャネル幅方向に湾曲した曲面を有する基材に貼り付けて曲面

を有するディスプレイを実現するものである。

(もっと読む)

スパッタリングターゲット、スパッタリングターゲットの作製方法および半導体装置の作製方法

【課題】酸窒化物膜を作製する成膜技術を提供する。また、その酸窒化物膜を用いて信頼性の高い半導体素子を作製する。

【解決手段】窒化インジウム、窒化ガリウム、窒化亜鉛の少なくとも1つを原料の一とし、これと、酸化インジウム、酸化ガリウム、酸化亜鉛の少なくとも1つと混合して窒素雰囲気中で焼結したインジウムとガリウムと亜鉛を有する酸窒化物よりなるスパッタリングターゲットを用いて酸窒化物膜を作製することにより、必要な濃度の窒素を含んだ酸窒化物膜が得られる。得られた酸窒化物膜はトランジスタのゲートやソース電極、ドレイン電極等に用いることができる。

(もっと読む)

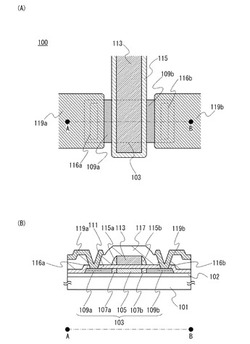

半導体装置

【課題】大面積基板など、熱収縮による影響の大きい基板に形成された半導体素子であっても、その影響を受けずに動作するような半導体素子の提供すること。また、そのような半導体素子を搭載し、薄膜半導体回路及び薄膜半導体装置を提供すること。さらに、多少のマスクずれが生じたとしても、その影響を受けずに動作するような半導体素子を提供する。

【解決手段】ドレイン領域114、117側の半導体層の低濃度不純物領域と重なるように形成した複数のゲート電極102を有し、それぞれのゲート電極102が形成するチャネル領域122、123に流れる電流の向きが一方向と一方向と反対の方向となるようにそれぞれのゲート電極102に対応するソース領域115、116とドレイン領域114、117を形成し、一方向に電流が流れるチャネル領域122と一方向と反対の方向に電流が流れるチャネル領域123の数が等しい薄膜トランジスタ。

(もっと読む)

半導体装置

【課題】本発明は、曲面を有する基材に被剥離層を貼りつけた半導体装置およびその作製方法を提供することを課題とする。特に、曲面を有するディスプレイ、具体的には曲面を有する基材に貼りつけられたOLEDを有する発光装置、曲面を有する基材に貼りつけられた液晶表示装置の提供を課題とする。

【解決手段】本発明は、基板上に素子を含む被剥離層を形成する際、素子のチャネルとして機能する領域のチャネル長方向を全て同一方向に配置し、該チャネル長方向と同一方向に走査するレーザー光の照射を行い、素子を完成させた後、さらに、前記チャネル長方向と異なっている方向、即ちチャネル幅方向に湾曲した曲面を有する基材に貼り付けて曲面を有するディスプレイを実現するものである。

(もっと読む)

整流回路及びこれを用いた半導体装置

【課題】整流素子として用いるトランジスタの閾値電圧による出力電圧の降下が抑制された整流回路を提供する。または、入力される交流電圧の振幅が大きく変動する場合であっても、出力電圧の変動が抑制された整流回路を提供する。

【解決手段】トランジスタのゲート電極を、容量素子を介して該トランジスタの第2の電極の後段に接続し、ゲート電極の電位を第2の電極の電位に比べて高く、且つその差が閾値電圧以上となるように保って整流素子として用いればよい。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】現在、良質な膜を得るために、下地膜から非晶質シリコン膜までの形成プロセスは、各々の成膜室にて行われている。これらの成膜条件をそのまま用いて同一成膜室にて下地膜から非晶質シリコン膜までを連続形成すると、結晶化工程で十分に結晶化されない。

【解決手段】水素希釈したシランガスを用いて非晶質シリコン膜を形成することにより、下地膜から非晶質シリコン膜までを同一成膜室内で連続形成しても、結晶化工程で十分に結晶化可能となる。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置に於けるLDD構造とGOLD構造の形成は、従来、ゲート電極をマスクにセルフアラインで形成しているが、ゲート電極が2層構造となる場合が多く、成膜工程とエッチング工程が複雑になる。またドライエッチング等のプロセスのみでLDD構造及びGOLD構造の形成を行っている為、トランジスタ構造が全て同一構造となり、回路毎にLDD構造とGOLD構造及びシングルドレイン構造を別々に形成することが困難である。

【解決手段】 回折格子パターン或いは半透膜から成る光強度低減機能を有する補助パターンを設置したフォトマスク或いはレチクルをゲート電極形成用フォトリソグラフィ工程に適用することにより、ドライエッチング及びイオン注入工程を通し、回路毎にGOLD構造及びLDD構造及びシングルドレイン構造のトランジスタを簡単に形成することができることを特徴としている。

(もっと読む)

41 - 60 / 599

[ Back to top ]