Fターム[5F110PP29]の内容

Fターム[5F110PP29]に分類される特許

141 - 160 / 599

半導体装置及び半導体装置の作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】金属薄膜の一部または全部を酸化させた第1の層と酸化物半導体層の積層を用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、その絶縁層の形成時に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。

(もっと読む)

半導体製造方法、半導体製造装置、半導体装置および表示装置

【課題】均一性の極めて高いアニール処理結果を実現しつつ、その場合であっても生産性が損なわれてしまうことなく高スループット化を実現できるようにする。

【解決手段】基板上に少なくとも非晶質シリコン膜14と光吸収層16とが積層されてなる多層構造体に対して、前記光吸収層16の側から光を照射して当該光による局所加熱を行い、前記非晶質シリコン膜14を微結晶シリコン膜または多結晶シリコン膜に改質するアニール処理工程を備え、前記アニール処理工程では、前記局所加熱にあたり同一走査ライン上に複数の光ビームを配置するとともに、前記光吸収層16の熱伝導率をk、密度をρ、比熱をc、走査すべきライン長/走査速度をtpとした場合に、前記複数の光ビームを少なくとも間隔L=2×{k・tp/(ρ・c)}1/2だけ隔てて配置する。

(もっと読む)

半導体装置の作製方法

【課題】 信頼性の高いTFT構造を用いた半導体装置を実現する。

【解決手段】 TFTに利用する絶縁膜、例えばゲート絶縁膜、保護膜、下地膜、層間絶縁膜等として、ボロンを含む窒化酸化珪素膜(SiNX BY OZ )をスパッタ法で形成する。その結果、この膜の内部応力は、代表的には−5×1010dyn/cm2 〜5×1010dyn/cm2 、好ましくは−1010dyn/cm2 〜1010dyn/cm2 となり、高い熱伝導性を有するため、TFTのオン動作時に発生する熱による劣化を防ぐことが可能となった。

(もっと読む)

半導体装置

【課題】半導体装置の表示領域と駆動回路に設けられたTFTの構造を機能に応じて適切なものとするとき、pチャネル型TFTにおいて、チャネル形成領域と、不純物領域との接合に欠陥が形成され、オフ電流が増加することを防止する。

【解決手段】表示領域に第1のnチャネル型TFTが配置され、駆動回路に第2のnチャネル型TFT及びpチャネル型TFTが配置された半導体装置であって、pチャネル型TFTはチャネル形成領域と、これに隣接した不純物領域を有し、不純物領域にはnチャネル型TFTのために添加された不純物元素を含ませない。そのために、pチャネル型TFTのチャネル長はnチャネル型TFTのチャネル長より短くなる。

(もっと読む)

半導体素子基板の製造方法及び半導体素子基板並びに表示装置

【課題】同一基板上に、結晶粒の平均粒径が互いに異なり、各々優れたキャリア移動度を有する2種類の結晶質半導体膜を形成し、それら2種類の結晶質半導体膜を用いて異なる電気特性が要求される各半導体素子に所望の電気特性を得る。

【解決手段】基板11上に非晶質半導体膜24を成膜する非晶質膜成膜工程と、非晶質半導体膜24の一部を溶融固化して結晶化することで第1結晶質半導体膜24Aを形成する第1結晶化工程と、残部の非晶質半導体膜24を固相成長させることで第1結晶質半導体膜24Aよりも結晶粒の平均粒径が大きい第2結晶質半導体膜24Bを形成する第2結晶化工程と、第1結晶質半導体膜24Aの結晶粒の平均粒径が第2結晶質半導体膜24Bの結晶粒の平均粒径よりも小さい状態を維持しながら第1及び第2結晶質半導体膜24Bを溶融固化することで再結晶化する再結晶化工程とを含む。

(もっと読む)

ポリシリコン薄膜とその製造方法およびそれを用いた太陽電池とTFT、TFTアレイ、表示デバイスとそれらの製造方法

【課題】

反応性の単分子膜で被覆したシリコンナノ微粒子を用いたシリコンペーストを選択的に塗布し、レーザー照射することにより、単分子膜を分解除去し、微粒子から再結晶化されたポリシリコン薄膜を用いてTFTを形成することを特徴とする。

【課題を解決するための手段】

表面に共有結合した第1の反応性官能基を含む有機膜で被われたシリコン微粒子と、表面に共有結合した第2の反応性官能基を含む有機膜で被われたシリコン微粒子を有機溶媒中で混合して第1のシリコン微粒子ペーストを作成する工程と、

前記シリコン微粒子ペーストを基板表面に塗布する工程と、

硬化する工程と、

真空中または不活性ガス雰囲気中でレーザー照射してポリシリコン化する工程により、n(またはp)型のポリシリコン薄膜を製造する。

(もっと読む)

発光装置の作製方法

【課題】基板に対する剥離・転写の工程を簡略化した方法を提供する。

【解決手段】基板上に金属膜を形成し、加熱処理を行うことで、金属膜上に形成された酸化金属膜と、半導体膜の結晶化を同時に行うことができ、工程が簡略化された剥離・転写の方法である。金属膜にはタングステン膜などを用い、均一な剥離・転写を行うことができる。半導体膜に電気的に接続される電極上に発光層を形成することで発光装置の作製方法を提供することができる。

(もっと読む)

表示デバイスおよびその製法

【課題】アルミニウム合金膜と透明電極が直接コンタクトすることを可能とし、バリアメタルの省略を可能にするアルミニウム合金膜を用いた表示デバイスとその製造技術を提供する。

【解決手段】基板上に配置された薄膜トランジスタと、透明電極によって形成された透明導電膜、および、これら薄膜トランジスタと透明導電膜を電気的に接続するアルミニウム合金膜を有し、該アルミニウム合金膜と前記透明導電膜の界面には該アルミニウム合金の酸化皮膜が形成されており、該酸化皮膜の膜厚が1〜10nmで、該酸化皮膜中の酸素含有量が44原子%以下である表示デバイスとその製法を開示する。

(もっと読む)

薄膜トランジスタ及び表示装置の作製方法

【課題】マスク数の少ない薄膜トランジスタの作製方法を提供する。

【解決手段】第1の導電膜102と、絶縁膜104と、半導体膜106と、不純物半導体膜108と、第2の導電膜110とを積層し、この上に多階調マスクを用いて凹部を有するレジストマスク112を形成し、第1のエッチングを行って薄膜積層体を形成し、第1の導電膜102がエッチングされた膜113に対してサイドエッチングを伴う第2のエッチングを行ってゲート電極層116Aを形成し、その後ソース電極及びドレイン電極等を形成することで、薄膜トランジスタを作製する。半導体膜としては結晶性半導体膜106を用いる。

(もっと読む)

不揮発性半導体記憶装置およびその作製方法

【課題】フローティングゲート電極を備えた不揮発性メモリ素子の駆動電圧を高くすることなく、不揮発性メモリ素子、および厚いゲート絶縁膜を備えた高耐圧型トランジスタを同一基板上に形成する。

【解決手段】不揮発性メモリ素子の島状半導体領域とフローティングゲート電極間、および、トランジスタの島状半導体領域とゲート電極間には、第1の絶縁膜と第2の絶縁膜の積層膜が形成されている。第1の絶縁膜はフローティングゲート電極と重なる部分が除去されており、島状半導体領域とフローティングゲート電極間の絶縁膜が、トランジスタのゲート絶縁膜よりも薄くされている。トランジスタはフローティングゲート電極と同じ層に形成されている導電膜と、コントロールゲート電極と同じ層に形成されている導電膜とを有し、これら2つの導電膜は電気的に接続され、トランジスタのゲート電極として機能する。

(もっと読む)

半導体表示装置の作製方法

【課題】高精彩・高解像度・高画質・低消費電力の小型半導体表示装置を提供すること。

【解決手段】本発明の半導体表示装置は、画素マトリクス回路、データ線駆動回路、および走査線駆動回路を有しており、これらの構成要素が多結晶TFTによって同一基板上に形成される。また、その製造方法における、触媒元素を用いた結晶性の助長化プロセス、および触媒元素のゲッタリングプロセスによって、小型にもかかわらず、高精細・高解像度・高画質の半導体表示装置が提供される。

(もっと読む)

結晶性半導体膜の製造方法、半導体装置の製造方法、及び電子機器

【課題】(110)面の配向度が向上した他結晶シリコン膜を、ニッケル等を添加することなく得る。

【解決手段】基板1上に堆積された非晶質半導体膜3の被照射領域10にレーザー4を照射して、被照射領域10の一部を溶融領域20とした後、溶融領域20の中心方向へ向けて溶融状態にある非晶質半導体膜3の再結晶化させる第1工程と、被照射領域10を短軸方向に移動させる第2工程と、を交互に繰り返して行う結晶性半導体膜32の製造方法であって、第1工程は溶融された非晶質半導体膜3が両端部より結晶成長が進行して交わる前に固化した非多結晶領域36が該照射領域10の長軸方向に間欠的に存在するようにレーザー4を照射する工程で、第2工程はN回目の第1工程で形成された非多結晶領域36がN+1回目の第1工程で形成される溶融領域22に含まれるように被照射領域10を移動させる工程である、ことを特徴とする結晶性半導体膜32の製造方法。

(もっと読む)

保護回路、半導体装置、光電変換装置および電子機器

【課題】ESD対策をした保護回路および半導体装置を提供する。

【解決手段】集積回路と電気的に接続された信号線と、信号線と第1の電源線との間に設けられた第1のダイオード、及び第1のダイオードと並列に設けられた第2のダイオードと、第1の電源線と第2の電源線との間に設けられた第3のダイオードとを有し、第1のダイオードは、トランジスタをダイオード接続することによって形成されたダイオードであり、第2のダイオードはPIN接合又はPN接合を有するダイオードである保護回路。上記保護回路は、特に薄膜トランジスタを用いて作製される半導体装置に用いられることで効果を発揮する。

(もっと読む)

アモルファス膜の結晶化方法および装置

【課題】順次側面結晶化において形成される突起によるムラの発生を防止する。

【解決手段】レーザ光によって前記膜を溶融させない非完全溶融エネルギー領域を点在または、波形で振幅方向で間隔を置いて並列させ、該非完全溶融エネルギー領域間をレーザ光によって膜が溶融する溶融エネルギー領域にして、レーザ光を前記膜に照射して、膜の溶融部分を固相部分から順次側面結晶化し、さらに、前記固相部分が溶融部分となるように位置を変えて、前記非完全溶融エネルギー領域を点在させるとともに該非完全溶融エネルギー領域間を前記溶融エネルギー領域にして、前記レーザ光を前記膜に照射して順次側面結晶化する。非完全溶融エネルギー領域と前記溶融エネルギー領域とを有するレーザパターンでシリコン膜10に照射して結晶化する。

(もっと読む)

半導体製造方法と装置

【課題】部分的に絶縁膜が形成されているシリコン基板上を単結晶で覆うことができる半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】部分的に絶縁膜が形成されたSi基板10上に、a−Si膜14を成膜する(図1(b))。このSi基板10を熱処理すると、基板のSi結晶を種としてa−Siが固相Epi化される(図1(c))。基板の厚さ方向に対して充分にEpi結晶化された範囲を保護するようにレジスト膜18を形成し(図1(d))、エッチング処理を行い(図1(e))、その後、アッシング処理によってレジスト膜18を剥離し、このSi基板10上に再度a−Si膜を成膜する(図1(f))。再度、上記熱処理を行うことで、a−Siが固相Epi化される(図1(g))。

(もっと読む)

フラットパネルディスプレイ半導体の製造方法

【課題】a−Siプロセスと、ポリ−Siプロセスとを組み合わせることが可能なプロセスを提供することである。

【解決手段】プロセス800は、アモルファスシリコン又はアモルファスシリコンに適合可能なプロセスを用いて、ディスプレイパネル用のポリ−最終構造を形成する(ブロック810)。ポリ−最終構造は、チャネルシリコン前駆体を有する。次に、プロセス800は、ポリシリコン固有のプロセスを用いて、ポリ−最終構造からディスプレイパネルを形成する(ブロック820)。

(もっと読む)

半導体装置の作製方法

【課題】半導体装置の作製工程において、高調波のCWレーザを半導体膜上に相対的に走査させながら照射すると、走査方向に延びた長い結晶粒がいくつも形成される。このようにして形成された半導体膜は前記走査方向においては実質的に単結晶に近い特性のものとなるが、高調波のCWレーザの出力が小さくアニールの効率が悪い。

【解決手段】第2高調波に変換されたCWレーザと同時に基本波のCWレーザを半導体膜の同一部分に照射することで、出力の補助を行う。通常、基本波は1μmあたりの波長域に入り、この波長域では半導体膜に対する吸収が低い。しかしながら、可視光線以下の高調波を基本波と同時に半導体膜に照射すると、高調波により溶かされた半導体膜に基本波はよく吸収されるため、アニールの効率が著しく上がる。

(もっと読む)

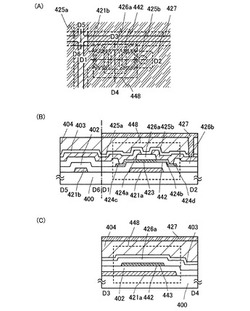

表示装置

【課題】オフリーク電流を低減させた薄膜トランジスタを備える表示装置の提供。

【解決手段】表示部が形成される基板上に薄膜トランジスタが形成されている表示装置であって、

前記薄膜トランジスタは、ゲート電極と、前記ゲート電極を被って形成されたゲート絶縁膜と、前記ゲート絶縁膜の上面に、平面的に観て前記ゲート電極からはみ出すことなく、前記ゲート電極に重畳して形成された島状の半導体層と、前記半導体層を被って形成された絶縁膜と、前記絶縁膜に形成された一対のスルーホールのそれぞれを通して前記半導体層と電気的に接続された一対の電極とを備え、

前記半導体層は、結晶性半導体層と非晶質半導体層の順次積層体からなり、前記電極のそれぞれは、不純物がドープされた半導体層と金属層の順次積層体からなっている。

(もっと読む)

半導体薄膜の製造方法、半導体薄膜、及び薄膜半導体装置

【課題】大きな結晶粒径の結晶粒径で、且つ、3次元的に結晶方位を制御された結晶粒で構成された半導体薄膜を製造し、この半導体薄膜を用いた半導体薄膜によって、優れたキャリア移動度を得る。

【解決手段】半導体薄膜の製造方法は、基板上に非晶質膜を形成する非晶質膜形成工程と、前記非晶質膜形成工程で形成した非晶質膜の少なくとも一部を結晶化させて、膜面に平行な特定の結晶面を持つ第1の多結晶膜を形成する第1結晶化工程と、前記第1結晶化工程で形成した第1の多結晶膜に1方向からイオン注入を行うことにより、3次元的に方位制御された所定の結晶方位を有する結晶粒を残す一方、それ以外の結晶粒を非晶質化させるイオン注入工程と、前記イオン注入工程で残った3次元的に方位制御された所定の結晶方位を有する結晶粒をシ−ドとして非晶質領域を結晶化させることにより第2の多結晶膜を形成する第2結晶化工程と、を備える。

(もっと読む)

半導体装置

【課題】メモリ回路において、トランジスタの特性に依存することなく情報を保持できる時間のバラツキを是正する半導体装置を提供することである。

【解決手段】トランジスタの漏洩電流に対して別の電流経路を追加する。別の電流経路に流れる電流をトランジスタの漏洩電流に比べて大きくすることでトランジスタの特性に依存することなく情報を保持できる時間のバラツキを是正させる。構成としては、トランジスタに漏洩電流を流させないように容量と並列に素子を追加し、別の電流経路を設ける。

(もっと読む)

141 - 160 / 599

[ Back to top ]