Fターム[5F110PP31]の内容

Fターム[5F110PP31]の下位に属するFターム

Fターム[5F110PP31]に分類される特許

81 - 91 / 91

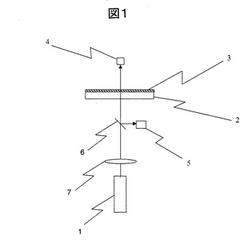

薄膜の膜厚測定方法、多結晶半導体薄膜の形成方法、半導体デバイスの製造方法、およびその製造装置、並びに画像表示装置の製造方法

【課題】 薄膜の膜厚を1分間に1万点以上の測定を基板全面にわたって行う検査を可能とする。

【解決手段】 透明基板2上に形成された薄膜3に対してレーザ光を照射し、基板の測定領域全体に渡って基板内の多数の同一ポイントでの透過強度を透過光強度モニタ4、反射光強度を反射光強度モニタ5で測定する。反射率をRとし透過率をTとしてA=1−(R+T)の値からA値と膜厚の関係から膜厚を測定し評価する。

(もっと読む)

電気光学装置

【課題】電気光学装置に用いるインバータ回路に関する。

【解決手段】インバータのNチャネル型薄膜トランジスタは、チャネル領域と、複数のN型の不純物領域が設けられた半導体層と、前記半導体層上に設けられたゲイト絶縁膜と、前記ゲイト絶縁膜上に設けられ、かつ前記N型の不純物の少なくとも1つと重なっているゲイト電極とを有する。

またインバータ回路のPチャネル型薄膜トランジスタは、チャネル領域と、複数のP型の不純物領域が設けられた半導体層と、前記半導体層上に設けられたゲイト絶縁膜と、前記ゲイト絶縁膜上に設けられたゲイト電極と、を有する。

(もっと読む)

半導体装置の作製方法

【課題】水分や酸素の透過による劣化を抑えることが可能な半導体装置、例えば、プラスチック基板上に形成された有機発光素子を有する発光装置、プラスチック基板を用いた液晶表示装置の提供を課題とする。

【解決手段】本発明は、ガラス基板または石英基板上に形成した素子(TFTや、有機化合物を含む発光素子や、液晶を有する素子や、メモリー素子や、薄膜ダイオードや、シリコンのPIN接合からなる光電変換素子や、シリコン抵抗素子など)を含む被剥離層12を基板から剥離した後、熱伝導性の高いプラスチック基板10に転写する。

(もっと読む)

半導体装置およびその製造方法

【課題】薄膜トランジスタの結晶質半導体層における活性領域に含まれる触媒元素の濃度を十分に低減させ、そのような装置を、工程数を増やす事なく、かつ低コストに製造する事を提供する。

【解決手段】薄膜トランジスタ10は、チャネル領域7、ソースおよびドレイン領域9を含む結晶質領域を有する半導体層13と、半導体層13の少なくともチャネル領域7、ソースおよびドレイン領域9の上に形成されたゲート絶縁膜3と、ゲート絶縁膜3を介してチャネル領域7に対向するように形成されたゲート電極5とを有し、半導体層13は、ソースおよびドレイン領域9よりも高い濃度で触媒元素を含むゲッタリング領域11をさらに有し、ゲッタリング領域11の上のゲート絶縁膜3は、ゲート絶縁膜3のうち少なくともゲート電極5と半導体層13との間に位置する部分よりも薄い。

(もっと読む)

半導体装置およびその作製方法

【課題】レーザビームが照射された領域全体に占める微結晶が形成される領域の割合を減らし、半導体膜に対して良好にレーザ照射を行うことができるレーザ照射装置を提供すること、およびレーザ照射方法を提供すること。

【解決手段】レーザ発振器101から出射したレーザ光104をスリット102を通過させることによって強度の弱い部分を遮断した後にミラー103で偏向させ、このレーザ光を凸型シリンドリカルレンズ105,106または凸型球面レンズを用いて任意の大きさにビームの整形をした後に照射面に照射する。

(もっと読む)

光変調素子、結晶化装置、結晶化方法、薄膜半導体基板の製造装置、薄膜半導体基板の製造方法、薄膜半導体装置、薄膜半導体装置の製造方法および表示装置

【課題】半導体膜から粒径の大きな結晶相の半導体を得る工程において、以降の工程で、アライメントマークとして利用可能なマーク構造を、同一の露光工程において半導体膜に形成する。

【解決手段】この発明は、光を変調して結晶化のための光強度分布を形成する光強度変調構造SPと、光強度変調構造と一体にまたは独立に設けられ、光を変調して所定形状のパターンを含む光強度分布を形成するとともに結晶化領域の予め定められた位置を示すマーク形成構造MKと、を有することを特徴とする光変調素子3に関する。この光変調素子によれば、絶縁基板上に所定厚さに堆積された半導体膜の任意の位置に、結晶核を形成し、その結晶核から所定の方向に結晶を成長させるとともに、半導体膜の任意の位置にアライメントマークAMを、同一工程で形成できる。

(もっと読む)

アクティブマトリクス基板、電気光学装置、電子デバイス及びアクティブマトリクス基板の製造方法

【課題】 高速駆動が可能な駆動回路とオフ電流の低い負荷回路とを備えたアクティブマトリクス基板の形成を低温プロセスによって実現する技術等を提供する。

【解決手段】 駆動回路を構成するTFTの半導体膜として略単結晶状態の半導体膜を形成する一方、画素回路を構成するTFTの半導体膜として微結晶状態の半導体膜を形成する。具体的には、駆動回路を構成するTFTが形成される領域には、該TFTの半導体膜が結晶化する際の起点となるべき微細孔14を設ける一方、画素回路を構成するTFTが形成される領域には、該TFTが結晶化する際の起点となるべき微細孔を設けない。

(もっと読む)

アクティブマトリクス基板、電気光学装置、電子デバイス及びアクティブマトリクス基板の製造方法

【課題】 高速駆動が可能な駆動回路とオフ電流の低い負荷回路とを備えたアクティブマトリクス基板の形成を低温プロセスによって実現する技術等を提供する。

【解決手段】 駆動回路を構成するTFTの半導体膜として略単結晶状態の活性半導体膜を形成する一方、画素回路を構成するTFTの半導体膜として微結晶状態の活性半導体膜を形成する。具体的には、駆動回路を構成するTFTが形成される領域には、結晶化の際に該活性半導体膜を局所的に加熱する局所加熱機構を設ける一方、画素回路を構成するTFTが形成される領域には、該局所加熱機構を設けない。

(もっと読む)

多結晶シリコンの製造方法及びそれを利用する半導体素子の製造方法

【課題】 良質のpoly−Siの製造及びそれを利用する半導体素子の製造方法を提供する。

【解決手段】 基板1に形成されたa−Si膜3に中性イオンを注入した後、熱処理による多結晶化を行うpoly−Si(多結晶シリコン)、多結晶シリコン層を含んだ半導体素子、及び多結晶シリコン活性層上に形成されたゲート絶縁層上に形成されるゲートを備えたTFTの製造方法であって、熱処理時に高エネルギーであるa−Siを多結晶化でき、一方では、熱に弱いプラスチック等にも良質のpoly−Siを形成でき、シリコン及びガラスのように熱に強い基板、またはプラスチックのように熱に弱い基板に良質の多結晶を形成できる。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】薄膜トランジスタ及びその製造方法を提供する。

【解決手段】薄膜トランジスタは基板10と、該基板上に形成され、チャンネル層14にシード(seed)及び結晶粒境界(Grain Boundary)が存在しない半導体層パターン11と、該半導体層パターン上に形成されたゲート絶縁膜15及び該ゲート絶縁膜上に形成されたゲート電極16とを含むことを特徴とする。結晶化触媒の均一な低濃度制御及び結晶化位置を調節することによって、薄膜トランジスタのチャンネル層内にシード及び結晶粒境界が存在しないようにしたり、結晶粒境界が一つ存在するように調節して素子特性及び均一度が良い薄膜トランジスタ及びその製造方法。

(もっと読む)

薄膜トランジスタの製造方法

【課題】 薄膜トランジスタの製造方法に関し、LDD領域の抵抗を許容レベルにまで下げるとともにTFTしきい値電圧のシフトを防ぐことを目的とする。

【解決手段】 絶縁性基板上に多結晶Siを形成する工程と、該多結晶Si上にゲート絶縁膜を形成する工程と、該ゲート絶縁膜上に下層ゲート電極と該下層ゲート電極より幅の狭い上層ゲート電極から成る2層ゲート電極を形成する工程と、該2層ゲート電極をマスクにして3属あるいは5属元素から成る不純物をイオン注入する工程と、熱処理する工程と、該2層ゲート電極をマスクにして水素をイオン注入する工程を含むように構成する。

(もっと読む)

81 - 91 / 91

[ Back to top ]