Fターム[5F140AA24]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | リーク、漏れ電流の防止 (995)

Fターム[5F140AA24]に分類される特許

201 - 220 / 995

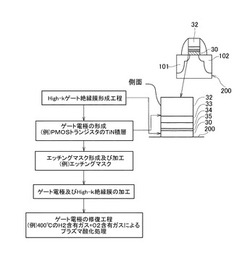

半導体デバイスの製造方法及び基板処理装置

【課題】金属製のゲート電極(メタル電極)のダメージを熱酸化により修復する際の高誘電率ゲート絶縁膜の結晶化を抑制する。

【解決手段】エッチングにより側壁が露出した高誘電率ゲート絶縁膜とメタル電極とを有する基板を処理室内に搬入する工程と、処理室内で、基板を高誘電率ゲート絶縁膜が結晶化しない温度に加熱した状態で、基板に対してプラズマで励起した水素含有ガスと酸素含有ガスとを供給して酸化処理を施す工程と、処理後の基板を処理室内から搬出する工程と、を有し、酸化処理を施す工程では、水素含有ガスの活性化時期と酸素含有ガスの活性化時期とが互いに一致するよう、処理室内への水素含有ガスの供給を開始した後、所定時間経過してから処理室内への酸素含有ガスの供給を開始する。

(もっと読む)

MIS型半導体装置及びその製造方法

【課題】半導体集積回路のトランジスタのゲート絶縁膜を、安定な高誘電率絶縁膜で構成した、リーク電流が小さくしかも駆動力の大きい、MIS型半導体装置を提供する。また、閾値電圧のバラツキの小さい、量産可能で安価な高誘電率ゲート絶縁膜の製造方法を提供する。

【解決手段】アルミニウム酸化物層と、ジルコニウムまたはハフニウムのシリコン酸化物層とを積層した積層ゲート絶縁膜を用いたMIS型半導体装置。ジルコニウムまたはハフニウムのシリコン酸化物層を、導電チャネル側に設置する。

(もっと読む)

半導体装置およびその製造方法

【課題】低オン抵抗かつ高耐圧で高速スイッチング可能な半導体装置をキャリアのライフタイムコントロールの為の格子欠陥を形成していない半導体基板で実現する。

【解決手段】P型Siからなる基板1の表面部に形成されたN型不純物層であるリサーフ領域2と、P型不純物層であるベース領域3と、高濃度のN型不純物層であるエミッタ/ソース領域8と、リサーフ領域2内に形成された低濃度のP型不純物層であるコレクタ領域4と、コレクタ領域4に隣接して形成され別断面に位置する高濃度のN型不純物層であるドレイン領域と、高濃度のP型不純物層であるベース接続領域10と、ゲート絶縁膜6と、ゲート電極7とからなる横型ハイブリットIGBTにおいて、コレクタ領域4が別断面に位置するドレイン領域よりも浅く形成されている。

(もっと読む)

半導体装置の製造方法

【課題】高い比誘電率が確保されており且つ熱的に安定なゲート絶縁膜を用いた半導体装置を実現できるようにする。

【解決手段】基板20上に、水素を含むHfO2 膜22Aを形成した後、HfO2 膜22Aに対して熱処理を行なうことにより、基板20側からシリコンをHfO2 膜22A中に拡散させてシリコン含有HfO2 膜22を形成する。その後、シリコン含有HfO2 膜22の上にゲート電極となるポリシリコン膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の製造方法に関し、シリサイドを構成する金属のサイドウォールの直下への潜り込みの影響を低減する。

【解決手段】 シリコン基板上にゲート電極を形成する工程と、ゲート電極の側壁に、第1絶縁膜による第1サイドウォールと、第1サイドウォール上にあって、第1絶縁膜とはエッチング特性の異なる第2絶縁膜による第2サイドウォールを形成する工程と、シリコン基板および第2サイドウォールを含む表面に金属をスパッタリングにより堆積させ、金属の一部をシリコン基板に侵入させる工程と、シリコン基板上に堆積した金属を除去する工程と、金属の除去工程の後に熱処理を行って、スパッタリングによってシリコン基板に侵入した金属とシリコン基板中のシリコン原子とを反応させてシリサイド層を形成する工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース・ドレイン領域にエピタキシャル結晶を含み、エピタキシャル結晶上の金属シリサイドに起因する接合リークの発生を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置1は、ファセット面13fを有するエピタキシャル結晶層13を有するMISFET10と、MISFET10を他の素子から電気的に分離し、上層3aのゲート電極12側の端部の水平方向の位置が下層3bのそれよりもゲート電極12に近く、上層3aの一部がファセット面13fに接する素子分離絶縁膜3と、エピタキシャル結晶層13の上面、およびファセット面13fの上層3aとの接触部よりも上側の領域に形成されたシリサイド層18と、を有する。

(もっと読む)

シャロートレンチアイソレーションプロセス

【課題】トレンチ構造の歪み導入要素によりに歪み導入されたチャネルを持つMOSトランジスタのリーク電流を改善する。

【解決手段】MOSトランジスタ106のチャネル領域108に、第1トレンチ構造55a、第2トレンチ構造55bによる歪み導入要素だけでなく、別の歪み導入要素として、MOSトランジスタ106表面上にコンフォーマルに設けられた窒化シリコンキャップ層130を設ける。別の態様では、チャネル領域108内の歪みは、ガス種、例えば水素、酸素、ヘリウムまたは別の希ガスをゲート110またはチャネル領域108の下の領域内に注入することによって導入される。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチゲート構造を有するトランジスタにおいて、サブスレッショルド特性を良好にする。

【解決手段】半導体装置100は、第1導電型のソース領域112およびドレイン領域113、これらの間に第2導電型のチャネル領域108が形成された基板102と、チャネル領域108において、ゲート幅方向に断続的に深さが変化するように形成されたトレンチ162を埋め込むように形成されたゲート電極122とを有するトランジスタを含む。チャネル領域108において、基板102表面およびトレンチ162の底部には、それぞれ第2の高濃度領域132および第1の高濃度領域130が形成されており、第2導電型の不純物濃度がトレンチ162側方における第2導電型の不純物濃度よりも高くなっている。また、第1の高濃度領域130の第2導電型の不純物濃度が第2の高濃度領域132の第2導電型の不純物濃度以上である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】LDMOSFETを有する半導体装置では、ソース電極が裏面にあることから、表面のソース・コンタクト領域と裏面のソース電極間の電気抵抗を低減するため、上面からP型エピタキシャル層を貫通してP+型基板内に伸びるボロンを高濃度にドープしたポリ・シリコン埋め込みプラグが設けられている。このポリ・シリコン埋め込みプラグの周辺のシリコン単結晶領域に転位が発生しており、これにより、リーク不良が誘発されていることが明らかとなった。

【解決手段】本願発明は、相互に不純物濃度の異なる第1及び第2の半導体層の境界面を貫通するシリコン系プラグを有する半導体装置であって、このプラグの少なくとも内部は多結晶領域であり、この多結晶領域表面の内、先の境界面の両側近傍は、固相エピタキシャル領域で覆われている。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を備えたCMISFETの性能を向上させる。

【解決手段】nチャネル型MISFETQnは、半導体基板1のp型ウエルPWの表面上に、ゲート絶縁膜として機能するHf含有絶縁膜3aを介して形成されたゲート電極GE1を有し、pチャネル型MISFETQpは、n型ウエルNWの表面上に、ゲート絶縁膜として機能するHf含有絶縁膜3bを介して形成されたゲート電極GE2を有している。ゲート電極GE1,GE2は、金属膜7とその上のシリコン膜8との積層構造を有している。Hf含有絶縁膜3aは、Hfと希土類元素とSiとOとNとからなる絶縁材料膜またはHfと希土類元素とSiとOとからなる絶縁材料膜であり、Hf含有絶縁膜3bは、HfとAlとOとNとからなる絶縁材料膜またはHfとAlとOとからなる絶縁材料膜である。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】酸化処理前における基板表面の初期酸化を抑えることができるとともに、自然酸化膜を除去できるようにする。

【解決手段】基板を処理室内に搬入する工程と、処理室内に酸素含有ガスと水素含有ガスとを供給して前記基板を処理する工程と、処理後の基板を処理室内より搬出する工程とを有し、処理工程では、処理室内の圧力を大気圧未満の圧力として処理室内に水素含有ガスを先行して導入し、続いて水素含有ガスの導入を維持した状態で酸素含有ガスを導入し、その後、水素含有ガスの導入を維持した状態で酸素含有ガスの導入を停止する。

(もっと読む)

電磁気素子用絶縁膜及び電界効果素子

【課題】リーク電流を増大させることなく薄膜化が可能であり、素子を微細化することができ、しかも、界面準位に起因する動作の不安定化を生じるおそれが少ない電磁気素子用絶縁膜、及び、このような電磁気素子用絶縁膜を用いた電界効果素子を提供すること。

【解決手段】12(CaxSr1-x)O・7Al2O3(0≦x≦1)で表される組成を有し、アモルファス構造を備えた電磁気素子用絶縁膜。半導体Aと、半導体A上に形成されたソース電極S及びドレイン電極Dと、ソース電極S−ドレイン電極D間の通電方向に対して垂直方向に電界を印加するためのゲート電極Gと、半導体Aとゲート電極Gとの間に形成されたゲート絶縁膜Bとを備えた電界効果素子10。ゲート絶縁膜Bは、本発明に係る電磁気素子用絶縁膜からなる。

(もっと読む)

半導体装置の製造方法

【課題】より高温の活性化FLAを行ってもウェハが割れることなく、SDエクステンション抵抗を下げることができる半導体装置の製造方法を提供する。

【解決手段】ウェハをウェハ表面温度1100℃以上に0.1〜10ミリ秒で加熱するための高強度のフラッシュランプアニールを照射する際、その直前のウェハ表面温度を800〜1000℃と高温にする。ウェハの予備加熱を、波形を調整したフラッシュで行うことにより不純物の拡散を抑制する。この手法により、アモルファス層を形成していないウェハ表面を効果的に活性化できるため、欠陥が少なく、かつ浅く低抵抗な接合が形成できる。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】良質な半導体−酸化物界面を有する電界効果トランジスタおよびその製造方法を提供する。

【解決手段】電界効果トランジスタ100は、半導体基板101と、半導体基板101上に形成されたチャネル層102と、チャネル層102上に形成された電子供給層103と、電子供給層103内に形成され、Ptを含む半導体層106と、半導体層106上に形成され、ゲート絶縁膜として機能するペロブスカイト型酸化物層107と、ペロブスカイト型酸化物層107上に形成されたゲート電極108とを備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】突出部の側面が凹凸状とされ、前記側面を覆うようにゲート酸化膜を形成したときに、実効的なチャネル長が増加して、ピラー型MOSトランジスタの電流駆動能力が低下するという課題があった。

【解決手段】基板と、前記基板の一面から垂直方向に突出された突出部7とを備え、突出部7の先端側の上部拡散層と、基端側の下部拡散層と、側面7cを覆うゲート絶縁膜14と、ゲート絶縁膜14を覆うゲート電極15と、を有し、チャネルが前記垂直方向となるピラー型MOSトランジスタ51を具備し、突出部7が平面視八角形状であり、突出部7の側面7cが{100}面からなる4つの主表面8a、8b、8c、8dと、{110}面および{111}面からなり、前記主表面8a、8b、8c、8dよりも面積が小さい4つの副表面9a、9b、9c、9dとからなる半導体装置101を用いることにより、上記課題を解決できる。

(もっと読む)

電界効果トランジスタ

【課題】電流コラプス現象およびゲートリーク電流を抑制することが可能な電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタ1は、基板10と、チャネル層11と、キャリア供給層12と、ソース電極21と、ドレイン電極22と、ゲート電極23と、ソース電極21とドレイン電極22との間でキャリア供給層12に積層されて電流コラプス現象を抑制する第1絶縁層31と、ドレイン電極22に対向する第1絶縁層31の端とドレイン電極22との間に形成された開口部40と、開口部40に露出したキャリア供給層12に積層された第2絶縁層32とを備える。

(もっと読む)

傾斜三元または四元マルチゲートトランジスタ

【課題】 フィン電界効果トランジスタ(FinFET)とその形成方法を提供する。

【解決手段】 半導体基板、前記半導体基板上の絶縁領域、及び前記半導体基板上に位置し、前記絶縁領域間の間隙に少なくとも一部を有し、第1III-V族化合物半導体材料を含むエピタキシー領域を含み、前記エピタキシー領域は、そこと前記半導体基板が第1格子不整合を有する下部分、及び前記下部分上に位置し、そこと前記半導体基板が前記第1格子不整合と異なる第2格子不整合を有する上部分を更に含む集積回路構造。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極中の不純物がゲート絶縁膜を突き抜けてチャネル領域に拡

散するのを抑制し、ソース・ドレイン領域の不純物イオンが部分的にチャネル領

域方向に異常拡散するのを防ぐ。

【解決手段】ゲート絶縁膜3上に、ポリシリコン膜4を被着してゲート電極5

パターンにパターンニングした後、ソース・ドレイン領域9を形成する前に、窒

素を含む雰囲気中で窒化処理を行って、ゲート電極5端部付近のゲート絶縁膜3

中に新たに窒素を導入する。または、ゲート電極5のパターンニング後、ソース

・ドレイン領域9を形成する前に、酸化処理を行うことによってゲート電極5の

パターンニングの際に生じるダメージや汚染の一部を酸化膜中に取り込んで基板

から除去する。その後、窒化処理を行うことにより、酸化処理によってゲート電

極5端部付近に形成され、ダメージを含む酸化膜に積極的に窒素を導入する。

(もっと読む)

GaN系半導体素子およびその製造方法

【課題】SiO2からなるゲート絶縁膜を常圧CVDによって形成することで、十分なノーマリオフ特性が得られるGaN系半導体素子およびその製造方法を提供する。

【解決手段】基板11上にバッファ層13を介して積層されたp型のGaN系化合物半導体からなるチャネル層14とゲート電極Gとの間にゲート絶縁膜17が形成されたGaN系半導体素子1において、ゲート絶縁膜17が、常圧CVD法により成膜されたSiO2膜である。常圧CVD法により成膜されたSiO2膜は、Si−H結合や未結合手の発生が抑制された高品質のSiO2膜である。このようなSiO2膜により、GaN系半導体素子のしきい値の制御に及ぼす悪影響も抑制されるので、十分なノーマリオフ特性が得られる。

(もっと読む)

半導体装置及びその製造方法

【課題】EOTの増大及びキャリア移動度の低下を抑制しつつ、半導体基板表面に形成されている酸化膜と高誘電率絶縁膜との界面に、しきい値電圧を低減する電気双極子を形成可能な金属を添加する。

【解決手段】半導体基板100上にゲート絶縁膜140を介してゲート電極150が形成されている。ゲート絶縁膜140は、酸素含有絶縁膜101と、第1の金属を含む高誘電率絶縁膜102とを有する。高誘電率絶縁膜102は、第1の金属とは異なる第2の金属をさらに含む。高誘電率絶縁膜102における第2の金属の組成比が最大になる位置は、高誘電率絶縁膜102と酸素含有絶縁膜101との界面及び高誘電率絶縁膜102とゲート電極150との界面のそれぞれから離れている。

(もっと読む)

201 - 220 / 995

[ Back to top ]