Fターム[5F140AA24]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | リーク、漏れ電流の防止 (995)

Fターム[5F140AA24]に分類される特許

161 - 180 / 995

半導体装置及びその製造方法

【課題】駆動電流が大きくリーク電流の少ない低消費電力のMISトランジスタを有する半導体装置及びその製造方法を提供する。

【解決手段】チャネル領域を有する半導体基板と、チャネル領域上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、半導体基板内にチャネル領域を挟むように配置されたソース拡散層及びドレイン拡散層と、ソース拡散層側の半導体基板内に形成された第1のポケット不純物層と、ドレイン拡散層側の半導体基板内に形成された第2のポケット不純物層とを有し、第1のポケット不純物層は、ソース拡散層のエクステンション不純物層の濃度ピーク位置よりも深い位置に濃度ピークを有しており、第2のポケット不純物層は、ドレイン拡散層のエクステンション不純物層の濃度ピーク位置よりも浅い位置に濃度ピークを有している。

(もっと読む)

半導体装置、および、その製造方法

【課題】半導体素子の特性を向上させると共に、半導体素子の微細化を容易に実現する。

【解決手段】半導体素子101にてゲート電極111gが設けられる部分の表面を凹凸面に形成する。ここでは、凹凸面のうち凸部CVでは、一対のソース・ドレイン領域112s,112dの表面と同一の面を覆うようにゲート絶縁膜111zを形成し、そのゲート絶縁膜111zの上面にゲート電極111gを設ける。これに対して、凹部TRでは、一対のソース・ドレイン領域112s,112dの表面から内部へ向けて設けられた溝Mの面を覆うようにゲート絶縁膜111zを形成し、その溝Mの内部を埋め込むようにゲート電極111gを設ける。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】エピタキシャル成長を行わなくても素子形成が行え、かつ、バンチングが発生することを防止できるようにする。

【解決手段】エピタキシャル成長を行わず、素子を構成する各領域をイオン注入のみによって形成すると共に、SiC基板1としてオフ角を有しないオン基板を用いる。これにより、イオン注入領域を活性化するための熱処理によってバンチングが発生しないようにできる。したがって、エピタキシャル成長を行わなくても素子形成が行え、かつ、バンチングが発生することを防止できるSiC半導体装置とすることができる。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】耐放射線性を有する絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】一部がチャネル領域をなすp型の半導体層11と、半導体層11の上部に活性領域21Bを定義する素子分離絶縁膜21と、チャネル領域にキャリア注入口を介してキャリアを注入するn型の第1主電極領域12と、チャネル領域から、キャリアを排出するキャリア排出口を有するn型の第2主電極領域13と、活性領域21Bの上に設けられたゲート絶縁膜22と、ゲート絶縁膜22の上に設けられ、第1主電極領域12と第2主電極領域13との間を流れるキャリアの流路に直交する主制御部、主制御部に交わる2本のガード部241,242を有してπ字型をなすゲート電極24と、第2主電極領域13のゲート幅方向の両端側に設けられたp型のリーク阻止領域61,62とを備える。

(もっと読む)

半導体装置およびその製造方法

【目的】コンタクト領域を確保し、ドレイン接合容量とリーク電流を減少させることができる半導体装置およびその製造方法を提供する。

【解決手段】ゲート電極5上のシリコン酸化膜6をマスクにドレイン領域7に斜めトレンチ10を形成して、ドレイン領域7の幅をコンタクト領域を形成できる最小幅にすることで、ドレイン接合容量とリーク電流を減少させる。

(もっと読む)

半導体集積回路装置

【課題】近年のCMOS型LSIの設計においてはリーク電力の削減が非常に大きな課題となっている。リーク電力を削減する手段としてはトランジスタの閾値電圧を複数使用し、速度の必要な場所には閾値電圧の低いトランジスタを、不要な場所には閾値電圧の高いトランジスタを使用する方法が広く用いられている。しかしながら先端プロセスほど閾値電圧制御だけではリーク電力が十分に抑制できず、様々なリーク電力削減手法が必要となってきている。

【解決手段】本願の一つの発明は、CMOSまたはCMIS型LSIにおいて、一部の論理ゲートを構成するPチャネルFETおよびNチャネルFETの両側のゲート電極形状を近接効果を利用して平面的に湾曲させることによって、実効的なゲート長を長くするものである。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタを備えた半導体装置において、トランジスタのGIDLを抑制する。

【解決手段】縦型トランジスタを備えた半導体装置に関する。縦型トランジスタは、半導体領域と、半導体領域上に設けられた柱状領域と、柱状領域の側面を覆うように設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極と、柱状領域の上部に設けられた第1の不純物拡散領域と、半導体領域内に柱状領域を囲むように設けられた第2の不純物拡散領域と、を有する。第1の不純物拡散領域は、柱状領域の側面と離間するように設けられている。

(もっと読む)

トランジスタの製造方法

【課題】ゲートとチャンネル部との接触面を増大させ電流の損失を減らし、チャンネルを形成する半導体層の格子特性を変化させ電子移動度を向上させることができるトランジスタの製造方法を提供すること、及び、ゲートと接触する面積が増大され、半導体層の格子特性も向上されてチャンネル部内の電子の流れを改善し、電力消耗も減らすことができるトランジスタの製造方法を提供すること、を目的とする。

【解決手段】半導体基板上に第1半導体層及び第1半導体層と異なる格子定数と結晶構造を有する第2半導体層を順次形成する段階と、第2半導体層及び第1半導体層をエッチングして格子定数の差によって第1半導体層の結晶構造が変形された変形結晶構造を有し、直線状の第1半導体パターンを形成する段階と、第1半導体パターン上に第1半導体層と同一な結晶構造を有する第3半導体層を形成する段階とを含む。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法のうちの一部は、大部分が既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法のうちの一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより一層正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

半導体素子及びトランジスタ

【課題】ゲートとチャンネル部との接触面を増大させ電流の損失を減らし、チャンネルを形成する半導体層の格子特性を変化させ電子移動度を向上させることができる半導体素子及びトランジスタを提供すること、及び、ゲートと接触する面積が増大され、半導体層の格子特性も向上されてチャンネル部内の電子の流れを改善し、電力消耗も減らすことができる半導体素子及びトランジスタを提供すること、を目的とする。

【解決手段】半導体基板上に形成されて第1半導体パターンを含む3次元直線状の第1構造物と、第一構造物の中心部を貫通するように配置され、第1半導体パターンと異なる結晶構造を有する第2半導体パターンを含む第2構造物と、第1構造物に対して直交する方向に延長して3面で第2構造物の一部を囲むゲートを含むトランジスタとする。

(もっと読む)

III族窒化物系電界効果トランジスタおよびその製造方法

【課題】オン抵抗が低いIII族窒化物系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】本発明のIII族窒化物系電界効果トランジスタは、下地半導体層上に第1窒化物半導体層および第2窒化物半導体層が順次積層された窒化物半導体積層体と、窒化物半導体積層体の上面に接する、ソース電極およびドレイン電極と、ソース電極およびドレイン電極の間の窒化物半導体積層体における、第1窒化物半導体層の一部および第2窒化物半導体層が形成されていない領域であるリセス領域と、リセス領域上に形成された窒化物半導体膜と、リセス領域の内壁面、および第2窒化物半導体層の上面に形成された絶縁膜と、絶縁膜上に形成されたゲート電極とを有し、第2窒化物半導体層は、第1窒化物半導体層に比べて広い禁制帯幅を有し、窒化物半導体膜の上面は、第1窒化物半導体層の上面よりも低いことを特徴とする。

(もっと読む)

半導体ヘテロ電界効果トランジスタ

【課題】ピエゾ電界により発生するシートキャリアの利用とチャネル部におけるピエゾ電界により深いディプレッション形成の抑制とを提供できる半導体ヘテロ電界効果トランジスタを提供する。

【解決手段】第1及び第3の領域23a、23cの主面24a、24cの法線ベクトルNV1、NV3は、該III族窒化物半導体のc軸Cxに直交する面に対して有限な角度で傾斜する。第2の領域23bの主面24bの法線ベクトルNV2は、該III族窒化物半導体のc軸Cxに直交する面に沿って延在する。第2の領域23bにおけるチャネル層25の第2の領域25bのピエゾ分極PZC2は、III族窒化物半導体領域23からバリア層27への方向に向いている。第1及び第3の領域23a、23cにおけるチャネル層25の第1及び第3の領域25a、25cのピエゾ分極PZC1、PZC3は、バリア層27からIII族窒化物半導体領域23への方向に向いている。

(もっと読む)

高電子移動度トランジスタの構造、その構造を含んだデバイス及びその製造方法

【課題】MMICのSPDTスイッチなど、半導体デバイスとして用いるのに適したMOS−PHEMTの構造及びその製造方法を開示する。

【解決手段】MOS−PHEMT構造は、Al2O3、HfO2、La2O3及びZrO2からなる群から選ばれる材料からなるゲート誘電体層107を有することを特徴とし、これにより、このMOS−PHEMTの構造を含む、高周波スイッチデバイスなどの半導体構造が、直流電流の損失及び挿入損失の低下を防ぎ、隔絶性を向上させることができる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極周辺の寄生容量を低減させることのできる半導体装置の製造方法を提供する。

【解決手段】半導体基板上にゲート絶縁膜を形成する。ゲート絶縁膜上に、その上部に絶縁膜を有するゲート電極を形成する。ゲート電極を形成した後、半導体基板とゲート電極を覆う第1シリコン酸化膜を形成する。第1シリコン酸化膜を形成した後、第1シリコン酸化膜を覆う第1シリコン窒化膜を形成する。第1シリコン窒化膜を形成した後、第1シリコン窒化膜を覆う第2シリコン酸化膜を形成する。第2シリコン酸化膜を形成した後、第2シリコン酸化膜をエッチングして、第2シリコン酸化膜をゲート電極の側壁部に残す。第2シリコン酸化膜をゲート電極の側壁部に残す工程の後、半導体基板に不純物拡散層を形成する。不純物拡散層を形成した後、第2シリコン酸化膜を除去する。第2シリコン酸化膜を除去した後、半導体基板を覆う第2シリコン窒化膜を形成する。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

電子デバイスにおける電力消費を低減するシステム及び方法が開示される。この構造及び方法は、大部分が、バルクCMOSのプロセスフロー及び製造技術を再利用することによって実現され得る。この構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することを可能にするとともに、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有し、それにより、電力制御の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

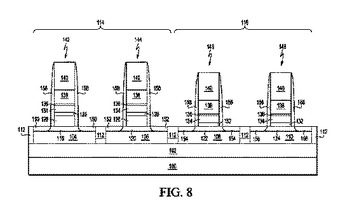

酸素拡散バリア層を有する半導体デバイスおよびそれを製造するための方法

方法および装置はトランジスタを製造するために提供される。トランジスタが、半導体材料104、106、108、110上に配置されたゲートスタック142、144、146を備える。ゲートスタックが、半導体材料上に堆積される酸化物層126、堆積された酸化物層上に配置された酸素拡散バリア層128、酸素拡散バリア層上に配置された高誘電率の誘電体層134、および高誘電率の誘電体層上に配置された酸素ゲッター導電性層138を備える。酸素拡散バリア層が、堆積された酸化物層から酸素ゲッター導電性層への酸素の拡散を防止する。  (もっと読む)

(もっと読む)

半導体装置とその製造方法

【課題】SiGe層を用いてPチャネル型トランジスタのチャネル形成領域に圧縮応力を印加すると共に、リーク電流を低減する。

【解決手段】半導体装置120は、半導体基板100の表面部に形成されたソース領域及びドレイン領域122と、これらに挟まれたチャネル形成領域上にゲート絶縁膜101を介して形成されたゲート電極102とを含むPチャネル型トランジスタを備える。ゲート電極102の両側それぞれにおいて半導体基板100にリセスが形成され、リセスに、SiGeからなる第1エピタキシャル層111と、その上に形成され且つSiからなる第2エピタキシャル層112と、その上に形成され且つSiGeからなり、チャネル形成領域を挟む第3エピタキシャル層113とを備える。ソース領域及びドレイン領域122は、第3エピタキシャル層113中に形成され、且つ、それぞれの接合深さがいずれも第3エピタキシャル層133の深さよりも浅い。

(もっと読む)

導電表面チャネル伸長部分とゲート制御チャネル側壁を有する薄体MOSFET

【課題】 導電表面チャネル伸長部分とゲート制御チャネル側壁を有する薄体MOSFETを提供する。

【解決手段】 導電表面チャネル伸長部分とゲート制御チャネル側壁を有する薄体MOSFETを提供する。一実施例は、半導体基板と、半導体基板の上面に配置されたチャネル層と、ゲート電極とチャネル層間を介するゲート誘電層と、チャネル層上に配置され、ゲート電極とオーミックコンタクト間を介する誘電伸長層とを備えたMOSFETである。ゲート誘電層は第一材料からなり、第一材料は、チャネル層に対する低欠陥の界面を形成する。一方、誘電伸長部分は、第一材料と異なる第二材料からなり、第二材料は、チャネル層に対する導電表面チャネルを形成する。

(もっと読む)

成膜方法及び処理システム

【課題】スループットを高く維持しつつリーク電流を抑制してリーク特性も高く維持することが可能な成膜方法を提供する。

【解決手段】被処理体の表面とゲート電極との間に介在されるゲート絶縁層を形成する成膜方法において、シリコンを含む界面膜を所定の温度で形成する界面膜形成工程S1と、被処理体を冷却する冷却工程S2と、冷却された被処理体に対して界面膜形成工程の所定の温度より低い温度でゲート絶縁膜を形成するゲート絶縁膜形成工程S3とを有する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極に対する不純物の突き抜けを抑止する。

【課題を解決するための手段】半導体装置の製造方法は、基板上方に成膜した多結晶シリコンをエッチングして基板の第1領域上方に第1ゲート電極を形成し、基板の第2領域上方に第2ゲート電極を形成し、第1領域及び第1ゲート電極を覆う第1パターンを形成し、第2ゲート電極及び第1パターンをマスクにして第2領域に第1不純物を第1ドーズ量で注入して第2領域に第1エクステンション領域を形成し、第1ゲート電極、第1領域及び第2ゲート電極の上面を露出させた第2パターンを形成し、第1エクステンション領域を覆い、第1ゲート電極、第2ゲート電極及び第2パターンをマスクにして第1領域に第2不純物を第1ドーズ量よりも多いドーズ量で注入して第1領域に第2エクステンション領域を形成するとともに、第1ゲート電極及び第2ゲート電極の少なくとも上部をアモルファス化する。

(もっと読む)

161 - 180 / 995

[ Back to top ]