Fターム[5F140AA24]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | リーク、漏れ電流の防止 (995)

Fターム[5F140AA24]に分類される特許

141 - 160 / 995

ダイヤモンド半導体素子及びその製造方法

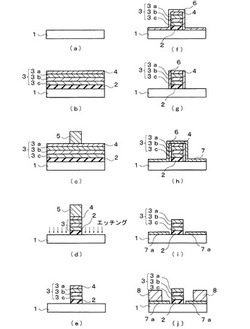

【課題】耐電圧、耐熱性、耐放射線性、及び高速性が優れ、かつ、チャネル領域を短くでき、素子の応答性が高いダイヤモンド半導体素子を高精度で製造できる半導体素子の製造方法を提供する。

【解決手段】第1のダイヤモンド半導体領域1の表面上に、絶縁膜2と多層金属電極層3と犠牲層4とを積層し、犠牲層4上に、局所的にレジスト5をパターン形成する。多層金属電極層3の最上層は、Pt又はPt合金により形成する。そして、レジスト5をマスクとして第1の犠牲層、多層金属電極層及び絶縁膜をエッチングした後、レジスト5を除去して、第1のダイヤモンド半導体領域1上に絶縁膜2と金属電極層3と第1の犠牲層4との積層体をパターン形成する。その後、第1のダイヤモンド半導体領域1上に、不純物の高濃度ドープ層7を形成する。その後、犠牲層4をエッチング除去し、高濃度ドープ層7上に金属電極8を形成する。

(もっと読む)

半導体装置

【課題】シリサイドプロセス前にイオン注入を行う半導体装置であって、より確実にMISFETにおけるリーク電流の抑制が図れるものを実現する。

【解決手段】マスク層RMによりPチャネル型MISFETを覆いつつ、Nチャネル型MISFETのN型ソース領域およびN型ドレイン領域に、イオン(F,Si,C,Ge,Ne,Ar,Krのうち少なくとも一種類を含む)を注入する。その後、Nチャネル型MISFETおよびPチャネル型MISFETの各ゲート電極、ソース領域およびドレイン領域にシリサイド化(Ni,Ti,Co,Pd,Pt,Erのうち少なくとも一種類を含む)を行う。これにより、Pチャネル型MISFETにおいてドレイン−ボディ間オフリーク電流を劣化させること無く、Nチャネル型MISFETにおいてドレイン−ボディ間オフリーク電流(基板リーク電流)の抑制が図れる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の不純物分布のバラツキを抑え、STIエッジ部分への電界集中をより効果的に制御でき、実効チャネル幅が狭くなることを抑制できる半導体装置およびその製造方法を提供する。

【解決手段】P型のシリコン基板10の一主面11に、トレンチ22と絶縁物24とを有する素子分離領域25と、素子分離領域25に囲まれた素子領域12であって、シリコン基板10の側面上部17が、トレンチ25に露出した素子領域12を形成し、ゲート絶縁膜40をシリコン基板10の上面14から側面上部17に延在して形成し、N+型ポリシリコン32とN+型ポリシリコン32の両側のP+型ポリシリコン34と、P+型ポリシリコン34の下側の側面上部17に沿って設けられたN+型ポリシリコン36とを有するゲート電極30を形成する。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】メモリセルMCは、半導体基板1の主面上のゲート絶縁膜5を介して設けられたコントロールゲート電極CGと、コントロールゲート電極CGの側面および半導体基板1の主面に沿って設けられたONO膜9と、ONO膜9を介してコントロールゲート電極CGの側面および半導体基板1の主面上に設けられたメモリゲート電極MGとを有する。コントロールゲート電極CGおよびメモリゲート電極MGの上部には、シリサイド膜15およびシリサイド膜15の表面の酸化によって形成された絶縁膜51が設けられている。

(もっと読む)

電界効果型トランジスタ

【課題】従来の電界効果型トランジスタでは、ソース領域およびドレイン領域に形成する高濃度不純物のイオン注入工程により半導体基板表面がアモルファス化されるため、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、活性化熱処理により結晶欠陥を誘発し、電界効果型トランジスタの信頼性を低下させる問題があった。

【解決手段】本発明の電界効果型トランジスタは、ソース領域およびドレイン領域を構成する部分の上部に高濃度不純物を含有する導電性膜を設ける。高濃度不純物のイオン注入を行う必要がないことから、この領域の半導体基板表面がアモルファス化することがない。これにより、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、再結晶化による結晶欠陥の発生を防ぐことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】バリアメタルの膜厚を抑制しながらメタルゲートの拡散性材料が高誘電率誘電体に拡散することを防ぐ。

【解決手段】半導体装置がゲート積層体構造を含む。ゲート積層体構造は、半導体基板5の上に形成された界面層4と、界面層4の上に形成された高誘電率誘電体3と、拡散性材料と不純物金属を含み、高誘電率誘電体の上方に形成されたシリサイドゲート1と、拡散性材料に対するバリア効果を持ち、高誘電率誘電体3とシリサイドゲート1の間に形成されたバリアメタル2とを備えている。不純物金属は、シリサイドゲート1の拡散性材料が高誘電率誘電体に導入されることを防ぐことができるような、拡散性材料に対するバリア効果を有している。

(もっと読む)

III族窒化物系へテロ電界効果トランジスタ

【課題】オン動作時には電子移動の抵抗が低く、かつオフ動作時にはゲート電極と2次元電子ガスとのゲートリーク電流が発生しにくいIII族窒化物系へテロ電界効果トランジスタを提供する。

【解決手段】本発明のIII族窒化物系へテロ電界効果トランジスタは、基板と、該基板の上に設けられるキャリア走行層と、該キャリア走行層上に、ヘテロ界面を形成するように設けられる障壁層と、該障壁層上の一部からキャリア走行層の内部まで掘り込まれたリセス構造と、該リセス構造上に設けられる絶縁層と、該絶縁層上に設けられるゲート電極とを含み、キャリア走行層および障壁層はいずれも、III族窒化物半導体からなり、絶縁層は、リセス構造の側面上に形成される側面絶縁層と、リセス構造の底面上に形成される底面絶縁層とからなり、側面絶縁層の厚みは、前記底面絶縁層の厚みよりも厚いことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】パワーMOSトランジスタのサイズの縮小を図り、ソース・ドレイン間絶縁破壊電圧の低下を防止する。

【解決手段】P+型コンタクト層17をN+型ソース層18の底面の直下のP型ベース層13内に埋め込んで形成する。これによりP型ベース層13の表面にN+型ソース層18と並列にP+型コンタクト層17を形成する必要がなくなりN+型ソース層18の幅を狭くできる。また、N+型ソース層18の底面の直下のP型ベース層13内にP+型コンタクト層17を形成するため、従来に比して、P+型コンタクト層17のN+ソース層18に対する面積占有率を大きくできる。この結果、NPN寄生トランジスタがオンすることを妨げる事ができる。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に応力を印加しつつ、基板やソース/ドレイン領域においてリーク電流の発生が効果的に抑制された半導体装置を提供する。

【解決手段】半導体装置は、第1導電型の不純物を含み、素子形成領域170を有する半導体基板101と、素子形成領域170上にゲート絶縁膜132を挟んで形成されたゲート電極125と、ゲート電極125の両側方に形成され、第2導電型の不純物を含むソース/ドレイン領域150とを備える。素子形成領域170のうちゲート電極の両側方に位置する領域には、半導体基板101の主面に対して傾いた半導体単結晶のファセット面を露出させる側壁を有し、コーナー部が丸められたリセス130が形成されており、ソース/ドレイン領域150は、リセス130に埋め込まれたシリコン混晶で構成されている。

(もっと読む)

状態密度が設計された電界効果トランジスタ

【課題】nチャネルおよびp型チャネルトランジスタに用いられる層構造を提供する。

【解決手段】nチャネルトランジスタを製作するのに用いる層構造を含む。層構造は、伝導帯底EC1を有する第1の半導体層、離散正孔準位H0を有する第2の半導体層、第1と第2の半導体層との間に配置された広バンドギャップ半導体バリア層、第1の半導体層の上方に配置されたゲート誘電体層、およびゲート誘電体層の上方に配置されたゲート金属層を含み、離散正孔準位H0は、伝導帯底EC1の下方に位置され、ゲート金属層にゼロバイアスが供給される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】IGBTのESD耐性を高くしつつ、IGBTのバイポーラトランジスタを確実に動作させる。

【解決手段】シンカー層115は第1導電型ウェル102に接しており、かつ第1導電型コレクタ層108及び第2導電型ドリフト層104から離れている。シンカー層115の表層には、第2導電型拡散層(第2の第2導電型高濃度拡散層)116が形成されている。第2導電型拡散層116はシンカー層115より不純物濃度が高い。第2導電型拡散層116と第1導電型コレクタ層108は、素子分離絶縁膜16を介して互いに分離している。

(もっと読む)

半導体集積回路装置の製造方法

【課題】低抵抗で、かつ接合リーク電流の少ないCoシリサイド層を形成することのできるサリサイドプロセスを提供する。

【解決手段】Co純度が99.99%以上で、FeおよびNiの含有量が10ppm以下、より好ましくはCo純度が99.999%の高純度Coターゲットを用いたスパッタリング法によってウエハの主面上に堆積したCo膜をシリサイド化することにより、MOSFETのゲート電極(8n、8p)、ソース、ドレイン(p+型半導体領域13、n+型半導体領域14)の表面に低抵抗で接合リーク電流の少ないCoSi2層(16b)を形成する。

(もっと読む)

半導体装置およびその作製法

【課題】チャネル層半導体として用いるInN系半導体において、高濃度の残留背景電子が存在していても、ピンチオフ特性が得られ、InN系半導体の優れた電子輸送特性(高い電子移動度および高い飽和電子速度)が活用可能となる、窒化物半導体を用いた導体装置およびその作製法を提供すること。

【解決手段】ソース電極1にオーミック接触する障壁層半導体とオーミック領域チャネル層半導体とから形成されるソース側へテロ接合構造、および、ドレイン電極3にオーミック接触する障壁層半導体とオーミック領域チャネル層半導体とから形成されるドレイン側へテロ接合構造が形成され、それぞれのへテロ接合構造が、InN系チャネル層半導体(#)と接し、それぞれのへテロ接合構造において、ヘテロ接合界面近傍のみに伝導電子が局在し、ヘテロ接合界面の垂直方向位置が、InN系チャネル層半導体(#)の層内位置に存在することを特徴とする半導体装置を構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】シリサイド層とシリコンの界面抵抗を低く保ちつつ、シリサイド層からの金属元素の拡散を抑制し、リーク電流および寄生抵抗を小さくする。

【解決手段】半導体装置100は、基板1(半導体層)と、基板1に接して形成され、基板1とは逆導電型の半導体電極10と、半導体電極10上に半導体電極10に接して形成されたシリサイド層14と、ゲッタリング層12内部において、基板1と半導体電極10との接合およびシリサイド層14からそれぞれ離れて形成され、シリサイド層14に含まれる金属元素をゲッタリングするゲッタリング層12と、を含む。

(もっと読む)

電界効果型トランジスタ、半導体メモリ、表示素子、画像表示装置及びシステム

【課題】比誘電率が高くリーク電流の少ない絶縁膜を提供する。

【解決手段】基板と、前記基板上に形成されたソース電極、ドレイン電極、及びゲート電極と、前記ゲート電極に所定の電圧を印加することによりソース電極とドレイン電極との間にチャネルが形成される半導体層を有し、前記ゲート電極と前記半導体層の間にゲート絶縁層と、を備え、前記ゲート絶縁層は、アルカリ土類金属の中から選ばれた1または2種類以上の元素と、Ga、Sc、Y、及びCeを除くランタノイドの中から選ばれた1または2種類以上の元素とを含むアモルファス複合金属酸化物絶縁膜により形成されていることを特徴とする電界効果型トランジスタを提供することにより上記課題を解決する。

(もっと読む)

半導体装置の製造方法、基板処理方法及び基板処理装置

【課題】 金属膜の酸化に起因する特性劣化を最小限に抑えることができる半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】 処理容器内に基板を搬入する工程と、処理容器内に処理ガスを供給し排気して化学的蒸着法により基板上に金属膜を形成する工程と、処理容器内にアルミニウム原子を含む原料ガスと窒素原子を含むガスとを供給し排気して化学的蒸着法により金属膜上に窒化アルミニウム膜を形成する工程と、金属膜および窒化アルミニウム膜形成後の基板を処理容器内から搬出する工程と、を有し、金属膜を形成する工程と窒化アルミニウム膜を形成する工程は、処理容器内を非酸素雰囲気に保った状態で連続的に行われる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】製造コストが低減し、電界効果トランジスタの短チャネル効果が抑制された半導体装置を提供する。

【解決手段】第1導電型のソース領域と、第1導電型のドレイン領域と、が表面に選択的に形成された第2導電型のウェル領域と、前記ソース領域と前記ドレイン領域との間の電流経路を制御する制御電極と、前記ソース領域に接続された第1の主電極と、前記ドレイン領域に接続された第2の主電極と、を備え、前記ソース領域の最も曲率が高い部分または前記ドレイン領域の最も曲率が高い部分と同じ深さの前記ウェル領域の位置を基準した場合、前記ウェル領域の深さ方向の前記第2導電型の不純物濃度分布のプロファイルは、前記基準からプラスマイナス0.15ミクロンの範囲に不純物濃度分布のピークを有することを特徴とする半導体装置が提供される。

(もっと読む)

誘電体膜の製造方法

【課題】比誘電率の低下を軽減しつつリーク電流値を低減し、スパッタ率の低下による堆積速度の減少を抑制し、かつ、面内均一性に優れた誘電体膜の製造方法を提供すること。

【解決手段】本発明の一実施形態に係る誘電体膜の製造方法は、基板上に、AlとSiとOを主成分とする金属酸化物である誘電体膜を形成する誘電体膜の製造方法であって、Al元素とSi元素のモル比率Si/(Si+Al)が0<(B/(A+B))≦0.1であり、非晶質構造を有する金属酸化物を形成する工程と、該非晶質構造を有する金属酸化物に1000℃以上のアニール処理を施し、結晶相を含む金属酸化物を形成する工程と、を備える。

(もっと読む)

液晶パネル用基板、液晶パネル、電子機器及び投射型表示装置

【課題】半導体を基板とする液晶パネルは、ウェル領域があるため、漏れ光がトランジスタ部分のみでなくそこから離れた半導体基板を通過しただけで光リーク電流が流れることがある。この光リーク電流が、ガラス基板上にスイッチング素子としてのTFTを配置した液晶パネルに比べて多くなるという欠点がある。

【解決手段】反射電極となる画素電極(14)と、画素電極への電圧印加を制御するスイッチング素子とを有する画素単位が基板上にマトリックス状に配置されてなる液晶パネル用基板において、両素電極とスイッチング素子の端子電極を構成する導電層(6a)との間に、両者を接続するためのコンタクトホールを形成し、このコンタクトホールの形成箇所を囲む開口を有し、隣接する複数の画素電極の間の領域には開口を有さない遮光層を、画素電極と導電層との間に設けることにより、画素電極どうしの隙間から漏込む光による弊害を防ぐ。

(もっと読む)

エピタキシャルソース/ドレインが自己整合したマルチゲート半導体デバイス

低寄生抵抗であるチャネル歪みされたマルチゲートトランジスタとその製造方法に係る。ゲートを連結したチャネル側壁の高さがHsiである半導体フィンのチャネル領域の上にゲートスタックを形成されてよく、ゲートスタックに隣接する半導体フィンのソース/ドレイン領域内に、エッチングレートを制御するドーパントを注入してよい。ドーピングされたフィン領域をエッチングして、半導体フィンの、略Hsiに等しい厚みを除去して、ゲートスタックの一部の下にある半導体基板の部分を露呈させるソース/ドレイン延長キャビティを形成してよい。露呈した半導体基板の上に材料を成長させて、再成長したソース/ドレイン・フィン領域を形成して、ソース/ドレイン延長キャビティを充填して、ゲートスタックからの長さを、チャネルの長さに実質的に平行な方向に離れる方向に延ばしてよい。 (もっと読む)

141 - 160 / 995

[ Back to top ]