Fターム[5F140AA24]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | リーク、漏れ電流の防止 (995)

Fターム[5F140AA24]に分類される特許

101 - 120 / 995

半導体装置

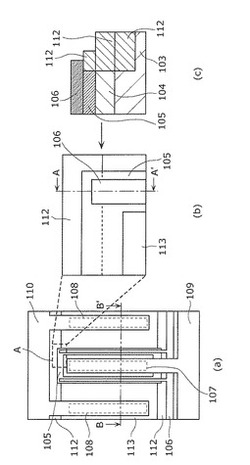

【課題】オフ時のリーク電流を低減し、パワースイッチング素子に適用可能なノーマリーオフ型の半導体装置を提供する。

【解決手段】基板101と、基板101の上に形成されたアンドープGaN層103と、アンドープGaN層103の上に形成されたアンドープAlGaN層104と、アンドープGaN層103又はアンドープAlGaN層104の上に形成されたソース電極107及びドレイン電極108と、アンドープAlGaN層104の上に形成され、ソース電極107とドレイン電極108との間に配置されたp型GaN層105と、p型GaN層105の上に形成されたゲート電極106とを備え、アンドープGaN層103は、チャネルを含む活性領域113と、チャネルを含まない不活性領域112とを有し、p型GaN層105は、ソース電極107を囲むように配置されている。

(もっと読む)

半導体装置及びその製造方法

【課題】金属電極と該金属電極の上に形成されたシリコン電極とを有するゲート電極を備えた電界効果型トランジスタを実現する際に、金属電極とシリコン電極との界面に生じる界面抵抗を低減できるようにする。

【解決手段】半導体装置は、半導体基板100における第1の活性領域103aに形成されたP型の電界効果型トランジスタを備えている。第1の電界効果型トランジスタは、第1の活性領域103aの上に形成された第1のゲート絶縁膜106aと、第1のゲート絶縁膜106aの上に形成された第1のゲート電極115aとを有している。第1のゲート電極115aは、第1のゲート絶縁膜106aの上に形成された第1の金属電極107aと、該第1の金属電極107aの上に形成された第1の界面層110aと、該第1の界面層110aの上に形成された第1のシリコン電極111aとを有している。

(もっと読む)

窒化物半導体MOSFET及びその製造方法

【課題】 本発明は上述の問題点を解決するためのもので、本発明の目的は、ソースとドレインに低い電子障壁を誘導するためにショットキー接触を有するITO透明電極を蒸着する窒化物半導体MOSFET及びその製造方法を提供することにある。

【解決手段】 窒化物半導体MOSFET及びその製造方法が提供される。本窒化物半導体MOSFETの製造方法は、単結晶シリコン基板上に有機金属化学蒸着器(MOCVD)を用いて緩衝層を蒸着し、緩衝層の上に窒化物半導体薄膜を形成し、窒化物半導体薄膜に硫化アンモニウムを処理し、硫化アンモニウムを処理した後、窒化物半導体薄膜の上にITOを用いて電極を形成し、電極を覆い、前記窒化物半導体薄膜の上にゲート誘電体を形成し、ゲート誘電体の上にITOを蒸着してゲート電極を形成する。これにより、窒化物半導体がエンハンスメントモードで動作することにより、漏れ電流及び出力消耗を減少させることができ、センサと集積化を簡単に実現することができる。

(もっと読む)

半導体積層体とこれを含むHFETおよびそれらの製造方法

【課題】半導体積層体に含まれるチャネル層下の化合物半導体層を不純物ドーピングでp型化することなく、その半導体積層体を含むHFETのリーク電流の低減や耐電圧の向上などを可能とする。

【解決手段】半導体積層体は、基板(11)上において順次堆積された第1、第2および第3の化合物半導体層(13、14、15)を少なくとも含み、その第1化合物半導体層(13)の少なくとも部分的層(16)は非晶質に改質されており、第2化合物半導体層(14)は第1化合物半導体層(13)に比べて小さなバンドギャップを有して光吸収層として作用し得る。

(もっと読む)

半導体装置の製造方法

【課題】製造工程を簡略化することの可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板11上に、ダミーゲート電極及びダミーコンタクトプラグの側面を覆う層間絶縁膜16を形成後、ダミーゲート電極、ダミーコンタクトプラグを選択的に除去して、ゲート電極形成用溝17及びコンタクト孔18を同時に形成し、次いで、ゲート電極形成用溝17内、コンタクト孔18内、及び層間絶縁膜16の上面を覆う高誘電率絶縁膜42を成膜し、次いで、斜めイオン注入法により、ゲート電極形成用溝17の下部17Aに形成された高誘電率絶縁膜42にイオン注入しないように、高誘電率絶縁膜42を介して、半導体基板に不純物拡散領域15を形成し、次いで、イオン注入された高誘電率絶縁膜42を選択的に除去することで、ゲート電極形成用溝の下部にゲート絶縁膜を形成し、かつコンタクト孔から不純物拡散領域15の上面を露出させる。

(もっと読む)

半導体デバイス及びその製造方法

【課題】ゲート電極と上部導電層とのショートを防止した安定動作可能な縦型MOSトランジスタを有する半導体デバイスを提供する。

【解決手段】縦型MOSトランジスタを構成する半導体ピラー5Aは、第1の幅を有する上部5Aaと第2の幅を有する下部5Abを有し、上部5Aa側面は第2の絶縁膜6aと第3の絶縁膜6bで覆われ、下部5Abは側面から第2の絶縁膜6aまでゲート絶縁膜である第1の絶縁膜11Aで覆われており、ゲート電極13Aが第2及び第3の絶縁膜6により上部導電層18と絶縁されている。

(もっと読む)

半導体装置およびその製造方法

【課題】SiC結晶面に低温の化学的酸化の技術を適用して、SiC結晶の方位Si面及び同方位C面へ酸化膜(化学的酸化膜)を形成する。

【解決手段】 数百℃に加熱したSiC結晶基板を気相硝酸雰囲気に曝して、同結晶の方位Si面及び方位C面に夫々酸化膜を直接形成する酸化処理過程で、気相硝酸は、例えば、高濃度硝酸から沸騰加熱して生成して、硝酸の濃度を安定に維持して、約4時間の処理を行うことにより、n型4H−SiC結晶の方位C面(000-1)の表面に炭素化合物を含まない,極めて良質なSiO2/SiC構造が創製された。

(もっと読む)

窒化物系化合物半導体および窒化物系化合物半導体素子

【課題】長期信頼性が高い窒化物系化合物半導体および窒化物系化合物半導体素子を提供すること。

【解決手段】アルミニウム原子、ガリウム原子、インジウム原子およびボロン原子から選択される1以上のIII族原子と、窒素原子とを含む窒化物系化合物半導体であって、添加物としてリチウム、銅、銀、または金を含む。好ましくは、前記添加物のドープ濃度は、ガリウム格子間原子の濃度と同程度である。好ましくは、前記添加物のドープ濃度は、5×1016cm−3〜5×1018cm−3である。

(もっと読む)

窒化物系化合物半導体および窒化物系化合物半導体素子

【課題】長期信頼性が高い窒化物系化合物半導体および窒化物系化合物半導体素子を提供すること。

【解決手段】アルミニウム原子、ガリウム原子、インジウム原子およびボロン原子から選択される1以上のIII族原子と、窒素原子とを含む窒化物系化合物半導体であって、添加物としてドープした金属原子とガリウム格子間原子とが複合体を形成している。好ましくは、前記添加物は鉄またはニッケルである。好ましくは、前記添加物のドープ濃度は、前記ガリウム格子間原子の濃度と同程度である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】リークパスを確実に防止することができる、半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置は、ゲート絶縁膜を介して半導体基板上に設けられたゲート電極と、前記ゲート電極の側部に設けられた側壁絶縁膜と、前記半導体基板内における前記ゲート絶縁膜を挟むような位置に形成され、前記側壁絶縁膜により覆われた被覆領域と前記側壁絶縁膜により覆われていない露出領域とを有する、ソース又はドレイン領域と、前記ゲート電極及び前記側壁絶縁膜を覆うように形成された、エッチングストッパ膜と、前記半導体基板上に、前記エッチングストッパ膜を埋め込むように設けられた、層間絶縁膜と、前記層間絶縁膜を貫通するように設けられ、前記露出領域に接続される、第1セルコンタクトプラグとを具備する。前記エッチングストッパ膜は、前記被覆領域と前記露出領域との境界部分が完全に覆われるように、前記露出領域の一部を覆っている。

(もっと読む)

Zr−Ge−Ti−OまたはHf−Ge−Ti−Oの誘電材料を備えた物質とその製造方法

【課題】 フィルム、またはRがZrとHfから選択されたR−Ge−Ti−Oを備えた誘電材料とその製造方法を提供する。

【解決手段】 本発明は、RがZrとHfから選択される、R−Ge−Ti−Oのフィルムを備えた誘電材料に関し、また、その製造方法に関連する。誘電材料は、公式Rx−Gey−Tiz−Owを有することが好ましく、ここで、.05≧x≦1、.05≦y≦1、0.1≧z≦1、1≧w≦2、x+y+z≡1であり、さらに好ましくは、0.15≧x≦0.7、.05≧y≦0.3、0.25≧z≦0.7、1.95≧w≦2.05であり、x+y+z≡1である。本発明は、ダイナミック・ランダム・アクセス・メモリ(DRAM)装置のコンデンサを備えたシリコンチップ集積回路装置での使用に特に有用である。

(もっと読む)

半導体装置、半導体集積回路装置、SRAM、Dt−MOSトランジスタの製造方法

【課題】Dt−MOSトランジスタよりなる半導体装置の素子寸法を縮小する。

【解決手段】シリコン基板21と、素子分離領域21Iと、前記素子分離領域により画成された、第1の導電型を有する第1のウェルよりなる素子領域21DNWと前記第1の導電型と逆の第2の導電型のコンタクト領域21P+1と、ゲート絶縁膜を介して、前記素子領域上から、前記素子分離領域のうち前記素子領域と前記コンタクト領域との間に延在するゲート電極と、第2の導電型のソース拡散領域と、第2の導電型のドレイン拡散領域と、前記ソース拡散領域の下端部に接して形成された第1の絶縁領域と、前記ドレイン拡散領域の下端部に接して形成された第2の絶縁領域と、前記ゲート電極と前記コンタクト領域とを電気的に接続するビアプラグと、を含み、前記第1のウェルは前記素子分離領域部分の下の前記シリコン基板を介して前記コンタクト領域に電気的に接続されていること。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に応力を印加するシリコン混晶層を活性領域に設けた半導体装置において、電流駆動能力の向上とリーク電流の低下と図れるようにする。

【解決手段】半導体装置は、シリコンからなる半導体基板10に形成され、周囲を素子分離領域11により囲まれてなる第2の活性領域10bと、該第2の活性領域10b及び素子分離領域11の上に、ゲート絶縁膜13を介在させて形成されたゲート電極14とを有している。第2の活性領域10bには、ゲート電極14の両側方の領域が掘り込まれてなるリセス領域19cにp型シリコン混晶層21が形成されており、該p型シリコン混晶層21における素子分離領域11と接触する接触位置の上端21bは、第2の活性領域10bの上面におけるゲート絶縁膜13の下側部分よりも低い。

(もっと読む)

半導体装置

【課題】半導体基板へのリーク電流が少ないMOS構造をダイオードとして用いる半導体装置を提供する。

【解決手段】電界効果トランジスタと、抵抗素子20と、を備える。前記抵抗素子は、前記電界効果トランジスタのバックゲート電極24と一方のソース・ドレイン領域16との接続点23と、前記電界効果トランジスタのゲート電極19との間に接続されている。そして、前記電界効果トランジスタの他方のソース・ドレイン領域15と前記ゲート電極19との間に電圧が印加される。

(もっと読む)

半導体素子、及び半導体装置

【課題】半導体素子の微細化に伴うゲート電極サイズの微細化においても、ゲート電極とチャネル形成領域間のリーク電流が抑制された半導体素子を提供することを課題の一とする。また、小型かつ高性能な半導体装置を提供することを課題の一とする

【解決手段】チャネル形成領域として機能する半導体層上に、ゲート絶縁膜として比誘電率が10以上の酸化ガリウムを含む絶縁膜を形成し、前記酸化ガリウム上にゲート電極が形成された構造を有する半導体素子を作製することにより、課題の一を解決する。また、前記半導体素子を用いて半導体装置を作製することにより、課題の一を解決する。

(もっと読む)

炭化珪素半導体装置の製造方法および炭化珪素半導体装置の製造装置

【課題】特性を向上できるSiC半導体装置の製造方法およびSiC半導体装置の製造装置を提供する。

【解決手段】SiC半導体装置の製造方法は、SiC半導体の第1の表面に第1の酸化膜を形成する工程(ステップS4)と、第1の酸化膜を除去する工程(ステップS5)と、SiC半導体において第1の酸化膜が除去されることにより露出した第2の表面に、SiC半導体装置を構成する第2の酸化膜を形成する工程(ステップS6)とを備える。第1の酸化膜を除去する工程(ステップS4)と、第2の酸化膜を形成する工程(ステップS6)との間において、SiC半導体は大気が遮断された雰囲気内に配置される。

(もっと読む)

半導体装置の製造方法

【課題】高誘電率絶縁膜を含むゲート絶縁膜を備えた電界効果型トランジスタにおいてゲート絶縁膜におけるゲート電極の端部下に位置する部分の厚膜化を試みると、高誘電率絶縁膜が結晶化し、ゲートトンネルリーク電流の発生を抑制出来ない場合があった。

【解決手段】半導体装置では、半導体基板1上にはゲート絶縁膜2が形成され、ゲート絶縁膜2上にはゲート電極3が形成されている。ゲート絶縁膜2では、ゲート絶縁膜2におけるゲート電極3の両端部下に位置する厚膜部分2aの膜厚は、ゲート絶縁膜2におけるゲート電極3の中央部下に位置する中央部分2bの膜厚よりも厚い。

(もっと読む)

半導体基板および半導体装置

【課題】高いしきい値電圧と低いリーク電流のノーマリーオフの半導体素子を提供する。

【解決手段】基板2の上に少なくともAlを含むIII族窒化物からなる下地層(バッファー層)3を設けた上で、III族窒化物、好ましくはGaNからなる第1の半導体層(チャネル層)4と、少なくともAlを含むIII族窒化物、好ましくはAlxGa1−xNであってx≧0.2である第2の半導体層(電子供給層)6が積層されてなる半導体層群からなるHEMT構造の半導体素子の上に、Al2O3−Ga2O3の混晶からなる絶縁膜7を形成し、その上にゲート電極9を形成した。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

半導体装置とその製造方法

【課題】良好な特性を有し且つ微細化を実現した半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、平面状シリコン層212上の柱状シリコン層208、柱状シリコン層208の底部領域に形成された第1のn+型シリコン層113、柱状シリコン層208の上部領域に形成された第2のn+型シリコン層144、第1及び第2のn+型シリコン層113,144の間のチャネル領域の周囲に形成されたゲート絶縁膜140、ゲート絶縁膜140の周囲に形成され第1の金属シリコン化合物層159aを有するゲート電極210、ゲート電極210と平面状シリコン層212の間に形成された絶縁膜129a、柱状シリコン層208の上部側壁に形成された絶縁膜サイドウォール223、平面状シリコン層212に形成された第2の金属シリコン化合物層160、及び第2のn+型シリコン層144上に形成されたコンタクト216を備える。

(もっと読む)

101 - 120 / 995

[ Back to top ]