Fターム[5F140AB05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 複合(回路要素) (3,149) | 三次元素子(SOIトランジスタとの組み合せ) (20)

Fターム[5F140AB05]に分類される特許

1 - 20 / 20

半導体装置、および、その製造方法

【課題】製造効率の向上、コストダウン、信頼性の向上を実現する。

【解決手段】第1導電型の第1電界効果トランジスタを第1基板に設ける。そして、第1導電型と異なる第2導電型の第2電界効果トランジスタを第2基板に設ける。そして、第1基板と第2基板とのそれぞれを対面させて貼り合わせる。そして、第1電界効果トランジスタと第2電界効果トランジスタとの間を電気的に接続させる。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】3次元形の半導体素子において、オン抵抗をより効果的に低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、ドレイン層と、ドレイン層内に選択的に設けられたドリフト領域と、ドリフト領域内に選択的に設けられたベース領域と、ベース領域内に選択的に設けられたソース領域と、ソース領域又はドレイン層の少なくとも一方の内部に、ソース領域又はドレイン層の少なくとも一方に選択的に設けられた第1,第2の金属層と、ドレイン層の表面に対して略平行な方向に、ソース領域の一部から、ソース領域の少なくとも一部に隣接するベース領域を貫通して、ドリフト領域の一部にまで到達するトレンチ状のゲート電極と、第1の金属層に接続されたソース電極と、ドレイン層又は第2の金属層に接続されたドレイン電極と、を備える。

(もっと読む)

電界効果トランジスタを備える半導体素子及びその製造方法

【課題】電界効果トランジスタを備える半導体素子及びその製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板上に形成され、第1活性領域の上面及び向き合う側面を経て伸張する第1ゲート電極を有する第1導電型の第1FET素子と、前記第1FET素子上に形成された層間絶縁膜と、前記層間絶縁膜上に形成され、第2活性領域の上面及び向き合う側面を経て伸張する第2ゲート電極を有する第2導電型の第2FET素子と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】 側壁部及び上部の平面部を持つ立体凹凸部分を形成した三次元デバイスとしての半導体装置において側壁部及び上部の平面部へ均一に高濃度の不純物を低エネルギードーピングできる方法を提供する。

【解決手段】 シリコン基板1の表面上に加工によりシリコンFin部11を形成した後、該シリコンFin部の側壁及び上部の平面部へドナーもしくはアクセプターとなる不純物原子を含む不純物薄膜を、堆積膜として上部の平面部には厚く、側壁には薄く堆積する工程と、前記シリコンFin部における前記堆積膜の斜め上方から斜め方向のイオン注入と反対側の斜め上方から斜め方向のイオン注入を行なうとともに、該イオン注入によって、前記不純物原子を堆積膜内部からシリコン基板の前記シリコンFin部の側壁内部及び上部の平面部内にリコイルして導入させる工程と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生抵抗の低下を図る。

【解決手段】半導体装置は、半導体基板10と、前記半導体基板上のソース/ドレイン領域に形成された第1半導体層11と、前記第1半導体層上に形成された第1部分12aと、前記ソース/ドレイン領域の間に位置するチャネル領域に形成された第2部分12bとを有する第2半導体層12と、前記第2半導体層の前記第1部分上に形成された第3半導体層13と、前記第2半導体層の前記第2部分の周囲に絶縁膜21を介して形成されたゲート電極22と、前記第1半導体層、前記第2半導体層の第1部分および前記第3半導体層内に形成されたコンタクトプラグ31と、を具備し、前記第2半導体層内における前記コンタクトプラグの径は、前記第1半導体層及び前記第3半導体層内における前記コンタクトプラグの径より小さい。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極7作製後にチャネル部12を作製する縦型MISFETの製造方法において、ゲート絶縁膜10に損傷を与えたり移動度を劣化させたりすることなく、孔底面に形成された絶縁膜や、自然酸化膜を除去する。

【解決手段】単結晶半導体基板1または単結晶半導体層に形成された不純物領域8の上に、第一絶縁層4、5と、ゲート電極層7と、第二絶縁層5、4と、をこの順に積層した積層体を形成し、前記積層体に不純物領域8が露出する孔を形成し、少なくとも前記孔の側壁に露出しているゲート電極層7、および、前記孔の底面に露出している不純物領域8の上に絶縁膜10を形成し、ゲート電極層7の露出部分の上に形成された絶縁膜10の上に半導体膜を重ねて形成し、不純物領域8の上に形成された絶縁膜を除去し、孔の底面に露出している不純物領域8に接し、孔底面から孔の開口部までつながる半導体部を形成する半導体装置の製造方法を提供する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】高集積であり且つビット線を埋め込む必要のない3次元トランジスタを有する半導体記憶装置を提供する。

【解決手段】ゲートトレンチを介して両側に位置する第1及び第2の拡散層とゲートトレンチの底面に形成された第3の拡散層とを有する活性領域と、第1及び第2の拡散層にそれぞれ接続された第1及び第2の記憶素子と、第3の拡散層に接続されたビット線と、ゲート絶縁膜を介してゲートトレンチの第1の側面を覆い、第1の拡散層と第3の拡散層との間にチャネルを形成する第1のゲート電極と、ゲート絶縁膜を介してゲートトレンチの第2の側面を覆い、第2の拡散層と第3の拡散層との間にチャネルを形成する第2のゲート電極とを備える。本発明によれば、ゲートトレンチの両側面にそれぞれ別のトランジスタが形成されることから、従来の2倍の集積度が得られる。

(もっと読む)

半導体装置およびその製造方法

【課題】3Dピラー型SGTを複数並列に接続する際に、配線層を設ける必要のない半導体装置を提供する。

【解決手段】3Dピラー型SGTの上部主電極領域が選択エピタキシャル成長半導体層を含み、少なくとも2つの隣接する3Dピラー型SGTを、各々の選択エピタキシャル成長半導体層を接触させて並列接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体素子とコンタクトプラグとが高精度で位置合わせされた半導体装置の製造方法を提供する。

【解決手段】半導体基板のエッチング速度が絶縁層2のエッチング速度よりも速くなるように、裏面側から、半導体基板内の突起状領域に対応する位置の異方性エッチングを行い、第1構造体が露出するまで開口2を設ける。

(もっと読む)

半導体素子

【課題】インバータ回路など、電気接続された2つの半導体スイッチによるスイッチング動作を行なうための電気回路において、寄生インダクタンスおよびオン抵抗を抑制することができる構造の半導体素子を提供すること。

【解決手段】この半導体素子は、基板1と、基板1の一方側に形成される半導体積層構造部2とを備える。半導体積層構造部2は、n型層5、このn型層5の一方側(下面側)に積層されたp型層4、およびこのp型層4に積層されたn型層3からなる縦型npn構造の第1半導体積層構造8と、n型層5をこの第1半導体積層構造8と共有し、n型層5、このn型層5の他方側(上面側)に積層されたp型層6、およびこのp型層6に積層されたn型層7からなる縦型npn構造の第2半導体積層構造9とを備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】オン抵抗が低く基板の表面積に対して集積率の高い半導体装置を提供すること。

【解決手段】半導体装置100は、半導体基板上に設けられた素子形成領域101に、第1のトレンチ112、第2のトレンチ113、第3のトレンチ114が設けられている。第1のトレンチ112および第2のトレンチ113の内部には金属が堆積されており、それぞれドレイン電極102およびソース電極103が形成されている。第3のトレンチ114の内部には、ゲート絶縁膜105を介してポリシリコンが堆積されており、ゲート電極104が形成されている。

(もっと読む)

半導体素子及びその製造方法

【課題】本発明はフィントランジスタを含む半導体素子及びその製造方法に関する。

【解決手段】半導体素子は、素子分離構造を備えた半導体基板に画成されたフィン型活性領域と、フィン型活性領域の上部に形成されたリセスと、フィン型活性領域の上部に形成され、前記リセスを埋め込むシリコンゲルマニウム層を含むゲート電極とを含む。

(もっと読む)

積層型半導体集積装置

【課題】素子形成された複数の半導体層を積層し、集積可能な素子数を飛躍的に高めることができる積層型半導体集積装置を提供する。

【解決手段】本発明に係る積層型半導体集積装置は、基板上に直接、または緩衝層を介して積層されたGaN層と、前記GaN層の表面近傍に形成された複数のトランジスタと、前記トランジスタの表面及び側面を被覆する酸化膜または窒化膜と、前記酸化膜または窒化膜を含む前記GaN層上に、ELOによって積層されたAlGaN層と、を集積すべきトランジスタの数量に応じて繰り返し積層して形成される。

(もっと読む)

端面センサデバイスの製造方法

【課題】形状に限定されることなく、柔軟性ないし可撓性を有し、任意の形状の各種装置を作成することが可能な端面センサデバイス及びその製造方法を提供すること。

【解決手段】線状体の端面に、対象からの情報を受容して他の情報として出力する受容部が形成されていることを特徴とする端面センサデバイス。線状体2001は、中止部に中心電極2007を有し、その外周は絶縁膜2008で覆われている。上記線状体2001を用意し、その端面にn型半導体層2004を形成する。次いで、n型半導体層2004上にp型半導体層2003を形成する。これにより、線状体2001の端面にpn接合の受容部(光センサ)が形成される。

(もっと読む)

低次元構造体のカプセル化、転移方法

【課題】グループ内の低次元構造体の数、グループのアスペクト比を、より正確にコントロールすることができる。

【解決手段】低次元構造体(1)の第1のグループ(3a)と低次元構造体(1)の第2のグループ(3b)とを第1の基板に形成する工程を含む低次元構造体のカプセル化方法。低次元構造体(1)の第1のグループ(3a)と低次元構造体(1)の第2のグループ(3b)とはマトリックス(5)に別々にカプセル化される。カプセル化後、低次元構造体(1)の第1のグループ(3a)と低次元構造体(1)の第2のグループ(3b)とを分離してもよい。各グループは、その後、例えば第2の基板(7)に移動するなどの処理が行われる。グループ内の低次元構造体の数、グループのアスペクト比は、低次元構造体が形成される際に決定され、パターニング法を使って決定されていた従来の方法に比べて、より正確にコントロールすることができる。

(もっと読む)

半導体装置

【課題】ゲート長の微細化に対応し、完全空乏化素子として動作させることができ、ジュール熱に起因した発熱や基板浮遊効果が低減できる半導体装置を提供する。

【解決手段】p型半導体基板11上に形成された基板突起部31Aと、突起部31A上にゲート絶縁膜13を介して形成されたゲート電極14と、ゲート電極14を挟むように突起部31Aに形成されたソース領域15及びドレイン領域16と、基板突起部31Aを挟む半導体基板11上に形成された素子分離絶縁膜12と、素子分離絶縁膜12下の半導体基板11内に形成された第1、第2不純物領域17とを有する。第1及び第2不純物領域17同士が基板突起部31A下の半導体基板11内で接続され、ゲート電極14がその側面上に形成されている基板突起部31Aの高さ及び幅方向の長さは、ソース領域15及びドレイン領域16が形成される基板突起部31Aの高さ及び幅方向の長さよりそれぞれ短い。

(もっと読む)

半導体素子及びその製造方法

【課題】改善されたリセスチャンネルトランジスタを備えた半導体素子及びその製造方法に関するものである。

【解決手段】本発明は、半導体素子及びその製造方法に関し、特に3次元リセスチャンネル構造を埋め込む下部ゲート電極を第1下部ゲート導電層、リセスチャンネル構造の埋込み時に発生するシームとその移動を防止する支持層及び第2下部ゲート導電層の積層構造で形成するように半導体素子を設計することで、3次元リセスチャンネル構造のトポロジー特性により、リセスチャンネル構造内に生成するシームと後続する熱処理工程によるシームの移動現象を最小化し、素子の動作特性を向上させることのできる技術である。

(もっと読む)

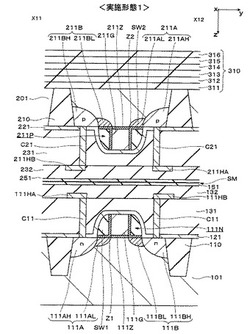

半導体装置

【課題】島状半導体層の側壁に形成される三次元構造のトランジスタの優れた特性を生かしつつ、インバータ、NAND、NOR、AND、OR、あるいはそれらの組み合わせを含む論理回路が構成された半導体装置を提供する。

【解決手段】表面に1以上の島状半導体層を有する半導体基板と、各島状半導体層の側壁部に形成されトランジスタもしくは抵抗体として動作する1以上の素子と、1以上の島状半導体層に形成された複数の前記素子が組み合わされて論理回路を構成するように前記素子を互いに接続する導電部とを備えることを特徴とする半導体装置。

(もっと読む)

複数のチャネルデバイス構造を備えたマルチ動作モードトランジスタ

それぞれ異なる動作特性を有する複数のチャネル(15)が用いられたマルチ動作モードトランジスタが提供される。複数のチャネル(15)は独立に調整可能なしきい値電圧を有する。しきい値電圧を独立に調整することにおいて、少なくとも1つの以下のもの、つまり、異なるチャネル(15)にそれぞれ異なるドーピング濃度、チャネル(15)を分離している異なるゲート誘電体(14a〜14c)にそれぞれ異なるゲート誘電体厚、および、異なるチャネル(15)に異なるそれぞれのシリコンチャネル厚、が供給される。  (もっと読む)

(もっと読む)

完全に量子井戸が空乏化した低出力のマルチチャネルCMOSFET

マルチチャネル半導体デバイスは、完全に、または部分的に量子井戸が空乏化(排除)(depleted)されており、CMOSFETのようなULSIデバイスにおいて特に役立つ。マルチチャネル領域(15)は、最上部のチャネル領域上に、例えばゲート絶縁膜(14c)により分離されるゲート電極が形成された状態で、基板(12)上に形成される。マルチチャネル領域(15)およびゲート電極(16)の垂直方向の積み重なりが、デバイスによって占有されるシリコン領域を増加させることなく、半導体デバイス中の駆動電流を増加させることができる。  (もっと読む)

(もっと読む)

1 - 20 / 20

[ Back to top ]