Fターム[5F140BC05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | チャネルの製造 (2,860) | 不純物の導入方法 (1,179)

Fターム[5F140BC05]の下位に属するFターム

イオン注入 (1,080)

固相拡散 (17)

補償拡散、カウンタードープ (29)

外方拡散の利用 (2)

Fターム[5F140BC05]に分類される特許

1 - 20 / 51

炭素ベース材料上の向上した結合界面を有する半導体構造体、その形成方法、及び、電子デバイス

【課題】 高密度で、構造部寸法がより小さく、より正確な形状の半導体構造体及び電子デバイスを提供する。

【解決手段】 炭素ベース材料の上面上に配置された少なくとも一層の界面誘電体材料を含む、半導体構造体及び電子デバイスが提供される。少なくとも一層の界面誘電体材料は、炭素ベース材料のものと同じである、典型的には六方晶短距離結晶結合構造を有し、従って、少なくとも一層の界面誘電体材料が、炭素ベース材料の電子構造を変えることはない。炭素ベース材料のものと同じ短距離結晶結合構造を有する少なくとも一層の界面誘電体材料の存在により、炭素ベース材料と、誘電体材料、導電性材料、又は誘電体材料及び導電性材料の組み合わせを含む、上にある任意の材料層との間の界面結合が改善される。その結果、改善された界面結合が、炭素ベース材料を含むデバイスの形成を容易にする。

(もっと読む)

ゲルマニウムベースの量子井戸デバイス

量子井戸トランジスタは、ゲルマニウムの量子井戸チャネル領域を有する。シリコンを含有したエッチング停止領域が、チャネル近くへのゲート誘電体の配置を容易にする。III−V族材料のバリア層がチャネルに歪みを付与する。チャネル領域の上及び下の傾斜シリコンゲルマニウム層によって性能が向上される。複数のゲート誘電体材料によって、high−k値のゲート誘電体の使用が可能になる。  (もっと読む)

(もっと読む)

CMOS用歪トランジスタの集積化

【課題】n型MOSデバイス(NMOS)の電子の移動度の向上、およびp型MOSデバイス(PMOS)のホールの移動度の向上した半導体装置および製造方法の提供。

【解決手段】(1)選択的に蒸着されたシリコン材料が、第1の領域における傾斜シリコンゲルマニウム基板材料の格子面間隔より小さい、シリコン材料の格子面間隔によって引き起こされる引っ張り歪を経験するべく、傾斜シリコンゲルマニウム基板の第1の領域上に選択的に蒸着されたシリコン材料のNMOSチャンネル、および(2)選択的に蒸着されたシリコンゲルマニウム材料が、第2の領域における傾斜シリコンゲルマニウム基板の格子面間隔よりも大きい、選択的に蒸着されたシリコンゲルマニウム材料の格子面間隔によって引き起こされる圧縮歪を経験すべく、基板の第2の領域上に選択的に蒸着されたシリコンゲルマニウム材料のPMOSチャンネルを有する。

(もっと読む)

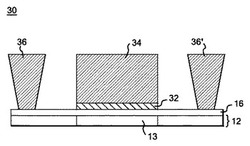

FinFETとトライゲートデバイス用のラップアラウンド型コンタクト

サブストレートとサブストレートの上に形成された半導体ボディを有する半導体デバイスである。半導体ボディはソース領域とドレイン領域を有している。ソース領域、ドレイン領域、またはその組み合わせは、第一の側面、第二の側面、及び上面を有している。第一の側面は第二の側面と向かい合っており、上面は底面と向かい合っている。ソース領域、ドレイン領域、またはその組み合わせは、実質的に全ての第一の側面の上に、実質的に全ての第二の側面の上に、そして上面の上に、形成されたメタル層を有している。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】Geを含む半導体で構成されるチャネル領域を有するP型FETにおいて、逆短チャネル特性の発生を抑制しつつ、短チャネル特性を改善する。

【解決手段】半導体装置は、半導体基板100上に形成されたP型FETを備えている。P型FETは、半導体基板100上に形成され、Geを含有する第1の半導体層103と、第1の半導体層103上に形成され、第1の半導体層103よりも低濃度のGeを含有する第2の半導体層104と、第2の半導体層104上にゲート絶縁膜107aを間に挟んで形成されたゲート電極110aと、第2の半導体層104のうちゲート電極110aの両側方に位置する部分に形成されたp型エクステンション領域111aと、第1の半導体層103内に設けられ、且つp型エクステンション領域111aの下に形成されたn型不純物領域152とを有している。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法のうちの一部は、大部分が既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法のうちの一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより一層正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

MIS型半導体装置及びその製造方法

【課題】半導体集積回路のトランジスタのゲート絶縁膜を、安定な高誘電率絶縁膜で構成した、リーク電流が小さくしかも駆動力の大きい、MIS型半導体装置を提供する。また、閾値電圧のバラツキの小さい、量産可能で安価な高誘電率ゲート絶縁膜の製造方法を提供する。

【解決手段】アルミニウム酸化物層と、ジルコニウムまたはハフニウムのシリコン酸化物層とを積層した積層ゲート絶縁膜を用いたMIS型半導体装置。ジルコニウムまたはハフニウムのシリコン酸化物層を、導電チャネル側に設置する。

(もっと読む)

半導体装置およびその製造方法

【課題】製造が容易で、短チャネル効果を抑制したままで、オフ電流を増加することなく、オン電流を増大させることが可能な半導体装置(縦型SGT)を提供する。

【解決手段】中空筒状に形成された半導体のボディ部4と、ボディ部4の下部に形成され、ソースおよびドレイン領域の一方となる第1の領域3と、ボディ部4の上部に形成され、ソースおよびドレイン領域の他方となる第2の領域5と、ボディ部4の前記ソース領域と前記ドレイン領域に挟まれた領域に形成されたチャネル領域4aと、チャネル領域4aの内周面および外周面をゲート絶縁膜を介して覆うように形成されたゲート電極7と、第1の領域に接するようにボディ部4の下方に形成され、第1の領域と同じ導電型の半導体層からなる第3の領域3aとを、備えたことを特徴とする半導体装置を採用する。

(もっと読む)

半導体装置

【課題】浅い不純物領域を有する半導体装置を提供する。

【解決手段】チャネル形成領域を含む半導体ならびにチャネル形成領域の上のフローティングゲート762およびコントロールゲート763によるゲート電極部752,753を含む半導体装置であって、ゲート電極部752,753の一方の側の半導体には、フローティングゲート762とオーバーラップする第1の不純物領域755が形成されており、フローティングゲート762の他方の側の半導体には、レーザドーピング処理により、深さが0.1μm以下で、且つフローティングゲート762とオーバーラップが無い第2の不純物領域757、758が形成されており、チャネル形成領域の長さは0.3μm以下である。

(もっと読む)

半導体装置

【課題】高い動作性能と高い信頼性とを同時に実現しうる新しい構造の半導体装置を提供する。

【解決手段】結晶性半導体で構成されるソース領域101、ドレイン領域103に挟まれた活性領域102において、局所的にゲルマニウムを添加することでSixGe1−x領域105を形成する。このSixGe1−x領域105とゲルマニウムが添加されなかったSi領域106とのバンド構造の差を利用して、ドレイン側からソース側に向かって広がる空乏層を効果的に抑止する。

(もっと読む)

画定された不純物勾配を有するひずみ材料層を使用する半導体構造、およびその構造を製作するための方法。

【課題】不純物の無い区域を有するひずみ材料層を含む半導体構造とデバイス、及びそれを製作するための方法を提供する。

【解決手段】ひずみ材料層104の特定の領域108は、半導体の隣接する部分から相互拡散することができる不純物を無い状態にしておく。不純物がひずみ材料層104の特定の領域108に存在する場合、デバイス性能の低下となる。説明された特徴を有する、又は説明されたステップに従って製作される半導体構造100とデバイス(例えば、電界効果トランジスタ、即ち「FET」)を使用することにより、デバイスの動作が向上する。

(もっと読む)

炭化ケイ素半導体装置およびその製造方法

【課題】チャネル移動度のような電気的特性の優れた炭化ケイ素半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1は、面方位{0001}に対しオフ角が50°以上65°以下である、炭化ケイ素からなる基板2と、半導体層(図1のp型層4)と絶縁膜(図1の酸化膜8)とを備える。半導体層(p型層4)は基板2上に形成され、炭化ケイ素からなる。絶縁膜(酸化膜8)は、半導体層(p型層4)の表面に接触するように形成されている。半導体層と絶縁膜との界面(チャネル領域と酸化膜8との界面)から10nm以内の領域における窒素原子濃度の最大値が1×1021cm-3以上である。

(もっと読む)

半導体装置

【課題】 不純物チャネル層から下方向への不純物拡散を防止することにより、接合容量や接合リークを抑えたトランジスタを提供する。

【解決手段】 半導体基板1と、前記半導体基板上に形成された第一の不純物拡散抑制層3と、前記第一の不純物拡散抑制層3上に形成された不純物チャネル層5と、前記不純物チャネル層5上に形成された第二の不純物拡散抑制層4とを備えることにより不純物チャネル層5から下方向への不純物拡散を防止した急峻な不純物濃度勾配を有するチャネル構造を形成することができ、具体的にはシリコン基板1の不純物濃度を1×1017cm−3以下にすることによってより効果的に接合容量や接合リークを抑えたトランジスタを形成することができる。

(もっと読む)

半導体素子

【課題】インバータ回路など、電気接続された2つの半導体スイッチによるスイッチング動作を行なうための電気回路において、寄生インダクタンスおよびオン抵抗を抑制することができる構造の半導体素子を提供すること。

【解決手段】この半導体素子は、基板1と、基板1の一方側に形成される半導体積層構造部2とを備える。半導体積層構造部2は、n型層5、このn型層5の一方側(下面側)に積層されたp型層4、およびこのp型層4に積層されたn型層3からなる縦型npn構造の第1半導体積層構造8と、n型層5をこの第1半導体積層構造8と共有し、n型層5、このn型層5の他方側(上面側)に積層されたp型層6、およびこのp型層6に積層されたn型層7からなる縦型npn構造の第2半導体積層構造9とを備える。

(もっと読む)

半導体装置

【課題】チャネル領域における高いキャリア移動度を有する半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上に形成され、内部におけるキャリアの移動度がSi結晶よりも大きい第1の結晶からなる半導体層と、前記半導体層上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記半導体層を挟んで形成され、前記半導体層に前記半導体層内のキャリアの移動度が上昇する方向に歪みを与える第2の結晶を含み、前記半導体層に接する深さの浅い領域であるソース・ドレインエクステンション領域を有するソース・ドレイン領域と、を有する。

(もっと読む)

トレンチゲート型トランジスタ及びその製造方法

【課題】トレンチゲート型トランジスタにおいて、ゲートリーク電流の発生を防止すると共に、ゲート容量を低減する。

【解決手段】N−型半導体層12にトレンチ14を形成する。トレンチ14において、N−型半導体層12のうちトランジスタの活性化領域となる領域には薄いシリコン酸化膜15Bが形成される。一方、活性化領域とならない領域にはシリコン酸化膜15Bよりも厚いシリコン酸化膜15Aが形成される。さらに、トレンチ14内から外に延びる引き出し部16Sがシリコン酸化膜15Aと接するゲート電極16を形成する。これにより、ゲート電極16の引き出し部16Sにおいてゲート電極16とN−型半導体層12の角部12Cとの距離が長く確保されるため、ゲートリーク電流の発生が防止されると共に、ゲート容量を低減することができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】超短チャネル長化でき、Si層厚一定によって閾値を変化させずにON電流を増加でき、さらにバックゲートにより閾値も動的に変更できる縦型トランジスタ構造を備えた半導体装置および半導体装置の製造方法を提供することを目的とする。

【解決手段】基板2上に、中心軸Mが基板2面と垂直方向に形成されてなる筒型の基柱3と、基柱3の上部と下部に、中心軸Mを中心とする同心形状に形成された第1導電型からなるソース・ドレイン拡散層4a,4bと、ソース・ドレイン拡散層4a,4bに挟まれた基柱3の中間部に形成された第1導電型からなるボディ層と、基柱3の側面にゲート絶縁膜6を介して形成されたフロントゲート電極7とを備えたことを特徴とする。また、第2導電型からなるバックゲート電極8が、基柱3の内側に上部から下部まで貫通する柱状に形成されてなることとする。

(もっと読む)

窒化物半導体素子および窒化物半導体素子の製造方法

【課題】チャネルが形成される部分における分極電荷の発生を抑えると共に、ブレークダウンの発生を抑制できる、窒化物半導体素子およびその製造方法を提供すること。

【解決手段】電界効果トランジスタは、n型GaN層3、p型GaN層4およびn型GaN層5が積層された窒化物半導体積層構造部2を備えている。窒化物半導体積層構造部2には、ドレイントレンチ6が形成されることにより、メサ積層部8が形成されている。メサ積層部8の壁面9は、n型GaN層5の頂面5aとの境界付近に位置する上側端部11と、n型GaN層3の上面3aとの境界付近に位置する下側端部12と、上側端部11と下側端部12との間に位置する中央部10とを有している。より具体的には、壁面9は、全体として傾斜角度の異なる複数の平面形状の傾斜部分17〜27を有している。そして、この壁面9には、ゲート絶縁膜15を挟んで、ゲート電極16が対向配置されている。

(もっと読む)

MOSFETの製造方法

【課題】 チャネルドープを行うことなく閾値電圧を調整可能なMOSFETの製造方法を提供する。

【解決手段】 本発明はMOSFETの製造方法として具現化される。その製造方法は、ソース領域と、ドレイン領域と、ソース領域とドレイン領域を結ぶチャネル領域を有する半導体基板を用意する工程と、チャネル領域の表面にゲート絶縁膜を形成する工程と、反応性スパッタリング法によってゲート絶縁膜上に金属化合物材料からなるゲート電極を形成する工程を備えている。本発明の製造方法では、反応性スパッタリング法で用いる希ガスと反応性ガスの流量比率を、目標とするMOSFETの閾値電圧に応じて調整する。

(もっと読む)

半導体装置

【課題】スイッチングノイズとスイッチング損失を抑制した、小型で安価なMOS型トランジスタを提供する。

【解決手段】ストライプ状のソース領域S1、チャネル形成領域C2およびゲート電極G1が、半導体基板の一方の面側に、互いに略並行に配置されてなる平面ゲート構造のMOS型トランジスタ101であって、複数個のソースコンタクトScが、ソース領域S1のストライプに沿って、等間隔に並んで配置され、並んで配置された所定数個の連続するソースコンタクトScで、単位セルU1が構成され、MOS型トランジスタ101が、単位セルU1の集合体で構成されてなり、単位セルU1において、MOS型トランジスタ101の閾値電圧が、ストライプに沿って連続的に変化するように設定されてなるMOS型トランジスタ101とする。

(もっと読む)

1 - 20 / 51

[ Back to top ]