Fターム[5F140BD14]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜 (8,730) | 材料 (6,782) | 少なくとも一部に空間を有するもの (12)

Fターム[5F140BD14]に分類される特許

1 - 12 / 12

電界効果トランジスタ

【課題】急峻なS値特性を有するとともに、ソース/ドレイン領域が同じ導電型となる対称構造を有する電界効果トランジスタを提供する。

【解決手段】本実施形態による電界効果トランジスタは、半導体層と、前記半導体層に離間して設けられたソース領域およびドレイン領域と、前記ソース領域と前記ドレイン領域との間の前記半導体層上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ソース領域および前記ドレイン領域側の前記ゲート電極の少なくとも一方の側面に設けられた高誘電体のゲート側壁と、を備え、前記ソース領域および前記ドレイン領域は前記ゲート電極の対応する側面から離れている。

(もっと読む)

多孔性絶縁体及び電界効果トランジスタ

【課題】例えば、チタン酸ストロンチウムを活性層とした電界効果トランジスタのゲート絶縁体としても使用することのできる、新規な絶縁体を提供することを目的とする。

【解決手段】絶縁性を示す材質中に直径5〜100nmである空孔を複数有し、全体の体積に対する前記空孔の占める体積の割合である空孔率が20体積%以上であり、前記空孔には水分が含まれ、前記空孔の体積に対する前記水分の占める体積の割合である水分占有率が23〜100体積%である多孔性絶縁体を使用する。

(もっと読む)

可動ゲート型電界効果トランジスタ

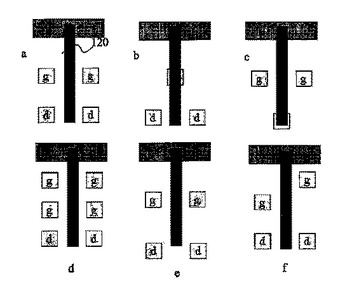

【課題】可動ゲート電極の変位を制御可能な可動ゲート型電界効果トランジスタを提供する。

【解決手段】ソース電極17とドレイン電極18との上に導電シールド電極20が配置される可動ゲート型電界効果トランジスタ1とした。そして導電シールド電極20の電位を固定することとした。導電シールド電極20が配置されることにより、可動ゲート15とドレイン電極18またはソース電極17との間に発生する静電力を抑制することができる。

(もっと読む)

半導体センサおよびその製造方法

【課題】プロセスの簡略化および静電引力の対策をともに行って、安価でありかつ高性能な半導体センサおよびその製造方法を提供する。

【解決手段】半導体基板11の長方形状のソース部・ドレイン部の中央を分断するように溝部17を設け、この溝部17の両側の側壁17a,17bに第1,第2の半導体層13,14を形成するという簡易プロセスで製造可能な構造を採用した。この構造では第1,第2の半導体層13,14が底面方向に薄く、可動ゲート電極15の底面方向の厚みも減らして溝部17の底面方向隙間17fを確保し、可動ゲート電極15に対する底面方向への静電引力の影響を受けにくくしている。また、可動ゲート電極15に対する側壁間方向の静電引力も相殺している。従って可動ゲート電極15への不要な力を除去して感度を向上させる。

(もっと読む)

半導体センサ

【課題】プロセスの簡略化および静電引力の対策をともに行って、安価でありかつ高性能な半導体センサおよびその製造方法を提供する。

【解決手段】半導体基板11の三層の半導体層の中央を分断する溝を設けて第1,第2の半導体層13,14を形成するという簡易プロセスで製造可能な構造を採用した。さらに空間部17の底方向隙間17fを確保し、可動ゲート電極15に対する底方向への静電引力の影響を受けにくくしている。また、可動ゲート電極15に対する側壁間方向の静電引力も相殺している。従って、可動ゲート電極15への不要な力を除去して感度を向上させる。

(もっと読む)

可動ゲート型電界効果トランジスタの製造方法

【課題】ダメージを生じさせることなく、安価かつ短時間に犠牲層を除去する犠牲層プロセスを採用し、量産性を向上させる可動ゲート型電界効果トランジスタの製造方法を提供する。

【解決手段】第1犠牲層15と、第2犠牲層16と、を有する複合犠牲層の上に可動ゲートが形成される可動ゲート形成工程と、第2犠牲層16がエッチング除去される第2犠牲層除去工程と、第1犠牲層15がエッチング除去される第1犠牲層除去工程と、を備える可動ゲート型電界効果トランジスタの製造方法とした。

(もっと読む)

電界効果トランジスタ

【課題】ゲート絶縁膜に起因するゲート絶縁破壊やホットキャリヤによる特性劣化を防止した絶縁ゲート型電界効果トランジスタを提供する。

【解決手段】ゲート電極が半導体基板表面と絶縁された電界効果トランジスタにおいて、少なくともゲート電極面と対向する半導体基板表面との間にゲート空隙が存在し、そのゲート空隙が気体で満たされている構成である。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率ゲート絶縁膜を使用したMISFETにおいて高誘電率ゲート絶縁膜を劣化させることなくMISFETの特性を向上させる。

【解決手段】基板1の活性領域上に高誘電率ゲート絶縁膜4Aを介してゲート電極5が形成されている。ゲート電極5の側面には、高誘電率を有する絶縁性サイドウォール7が形成されている。

(もっと読む)

半導体装置

【課題】電流駆動力の揺らぎが抑制されたショットキー型MOSFETを提供する。

【解決手段】半導体層と、前記半導体基板上に対向して形成された、金属または金属珪化物よりなる1対のソース領域およびドレイン領域と、少なくとも前記ソース領域およびドレイン領域の間の前記半導体層上に形成された第一の絶縁膜と、前記第一の絶縁膜上に形成され、且つ前記第一の絶縁膜よりも誘電率が高い第二の絶縁膜と、前記第二の絶縁膜上に形成されたゲート電極とを含み、前記ソース領域と前記ドレイン領域との対向方向に測った前記第二の絶縁膜の長さが、前記ソース領域と前記ドレイン領域との前記対向方向に測った前記ゲート電極の長さよりも短い事を特徴とする。

(もっと読む)

半導体装置

【課題】 ショットキー型電界効果トランジスターに於いて、殊にソース領域近傍のチャネル領域に対するゲート電極の制御性を高めて、素子の電流駆動能力の向上を図る。

【解決手段】 ゲート絶縁膜を異なる誘電率を持つ膜の積層とすることで、誘電率の高い材料のみで形成した場合と比べてゲート絶縁膜の幾何学的な意味の厚さを薄く形成することを可能とし、ゲート電極から出た電気力線のゲート絶縁膜の側面から外への漏れに起因する、殊にソース領域近傍のチャネル領域の電位に対するゲート電極の制御性の低下を抑制する事が可能となる。また、誘電率の高い材料よりなるゲート側壁絶縁膜12を設ける事に依り、異なる誘電率を持つ物質の界面に於ける電気力線の屈折に依って、ゲート電極から出た電気力線をソース領域近傍のチャネル領域に集める事が可能となり、ソース領域とチャネル領域との間に形成されるショットキー障壁を薄くし、その抵抗を低減する。

(もっと読む)

変形可能なゲートをもつMOSトランジスタ

【課題】本発明の目的は、ゲートの動きをより精細に検出できる変形可能なゲートをもつMOSトランジスタを提供することである。

【解決手段】半導体基板に形成された変形可能なゲートをもつMOSトランジスタは、ソースからドレインへの第一の方向及びその第一の方向に対して垂直な第二の方向へ向かって伸びるチャネルエリアにより分けられたソース及びドレインエリアと、チャネルエリアの両側の基板の上に設けられたベアリングポイントの間で第二の方向へ向かって伸びるチャネルエリアの少なくとも上部に設けられた導電ゲートの梁とを含み、そのチャネルエリアでは、チャネルエリアの表面がくぼんでおり、前記梁がチャネルエリアに対して最大のたわみを有するとき、ゲートの梁の形と同様の形をチャネルエリアの表面が有する。

(もっと読む)

ソース、ドレイン、及びゲートを有する電気機械的ナノチューブトンネル装置

本発明は、長手方向及び横方向の延長部を有するナノチューブと、ナノチューブの少なくとも第1部分を支持する構造と、その横方向の延長部によって定義されている第1方向においてナノチューブに対して力を作用させる第1手段と、を有するナノチューブ装置(100)に関するものである。ナノチューブの少なくとも第2部分は、力が一定のレベルを超過した際に、ナノチューブの第2部分がその横方向の延長部の方向において曲がり、これによって第1電気回路を閉じるように、構造の支持部を超えて突出している。好適には、力をナノチューブに対して作用させる第1手段は、電気的な手段であり、この力は、電圧をこの手段に印加することによって生成される。本装置は、ソース及びドレイン電極の両方において量子力学トンネル現象を実現する。  (もっと読む)

(もっと読む)

1 - 12 / 12

[ Back to top ]