Fターム[5F140BF21]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 3層 (490)

Fターム[5F140BF21]に分類される特許

481 - 490 / 490

トランジスタ形成方法

金属酸化膜トランジスタなどの半導体デバイスを基板上に形成する際に材料を堆積するための方法が提供される。一実施形態では、本発明は概して、第1の導電性を有する基板上にゲート誘電体を形成するステップと、該ゲート誘電体上にゲート電極を形成するステップと、該ゲート電極の横方向に対向する側壁に沿って第1の対の側壁スペーサを形成するステップと、該電極の対向する側に1対のソース/ドレイン領域限定部をエッチングするステップと、該ソース/ドレイン領域限定部にシリコンゲルマニウム材料を選択的に堆積するステップと、該堆積されたシリコンゲルマニウム材料にドーパントを注入して、第2の導電性を有するソース/ドレイン領域を形成するステップと、を含む基板を処理する方法を提供する。 (もっと読む)

半導体装置

【課題】 酸化膜と窒化膜の多層膜よりなるサイドウォールを有する半導体装置において、サイドウォールを構成する酸化膜がコンタクトエッチングの際にエッチングされてゲート電極の側面が露出するのを防ぐことができる半導体装置を得る。

【解決手段】 半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極上に形成された第1の窒化膜と、ゲート電極及び第1の窒化膜の側面に順番に形成された第1の酸化膜、第2の窒化膜、第2の酸化膜及び第3の窒化膜からなるサイドウォールとを有し、第1の窒化膜は、上部の外径が下部の外径よりも小さく、第1の酸化膜のゲート電極の側面にある部分は、上面から見て第2の窒化膜で覆われ、第2の酸化膜のゲート電極の側面にある部分は、上面から見て第3の窒化膜で覆われている。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】 本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】 半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

ニッケルゲルマノシリサイド化したゲートを組み込んだMOSFETおよびこれらのMOSFETを形成する方法

MOSFETのゲートまたはMOSFETのソースまたはドレイン領域は、シリコンゲルマニウムまたは多結晶シリコンゲルマニウムを含む。好ましくはニッケルシリサイドのモノシリサイドフェーズを含むニッケルゲルマノシリサイド(62、64)を形成すべく、ニッケルでのシリサイデーションを実行する。

ニッケルモノシリサイドによって呈される優れたシート抵抗を実質的に保持する一方、シリサイド中にゲルマニウムを含むことは、モノシリサイドフェーズが形成され得るより温度領域をより広くする。その結果、ニッケルゲルマノシリサイドは、後続のプロセスの間、ニッケルモノシリサイドよりも、より高い温度に耐えることができる。しかしながら、ニッケルモノシリサイドとほぼ同一のシート抵抗および他の有益な特性を提供する。  (もっと読む)

(もっと読む)

シリサイド層を有する半導体素子の製造方法

半導体素子を形成する方法では、半導体基板を設け、絶縁層を半導体基板の上に形成し、導電層を絶縁層の上に形成し、第1金属シリサイド層を導電層の上に形成し、導電層をパターニングして、制御電極の一部分であるパターニング済み第1層を形成し、第1金属シリサイド層をパターニングしてパターニング済み第1金属シリサイド層を制御電極の上に形成してパターニング済み第1金属シリサイド層が制御電極の上に残るようにし、そして第2金属シリサイド層をパターニング済み金属シリサイド層の上に形成し、第2金属シリサイド層は第1金属シリサイド層の膜厚よりも厚い膜厚を有する。  (もっと読む)

(もっと読む)

切り欠き制御電極及び当該電極の構造を有する半導体素子の製造方法

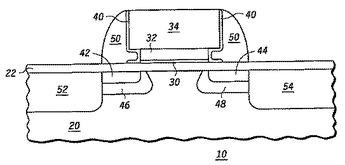

半導体素子(10)を形成する方法では、一の表面を有する基板(20)を設け、絶縁層(22)を基板(20)の表面の上に形成し、第1パターニング済み導電層(30)を絶縁層(22)の上に形成し、第2パターニング済み導電層(32)を第1パターニング済み導電層(30)の上に形成し、パターニング済み非絶縁層(34)を第2パターニング済み導電層(32)の上に形成し、そして第1及び第2パターニング済み導電層(30,32)の一部分を選択的に除去して、半導体素子(10)の切り欠き制御電極を形成する。  (もっと読む)

(もっと読む)

シリコン領域に形成されたニッケル/コバルトシリサイド領域を有する半導体デバイス

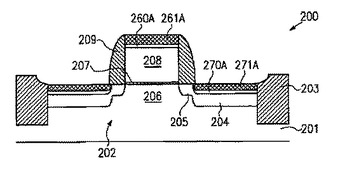

電界効果トランジスタのゲート電極などの、シリコン含有領域に、埋め込まれたニッケルシリサイド層(260A)、続いてコバルトシリサイド層(261A)を形成することによって、縮小されたシリコン回路構造のシート抵抗及び接触抵抗を過度に損なうことなく、デバイスを更に縮小することができるように、両シリサイドの優れた特性が組み合わせられる。  (もっと読む)

(もっと読む)

酸化物−窒化物スタックゲート誘電体

半導体構造体を作製する方法は、基板上に酸化物層を形成する段階と、酸化物層上に窒化ケイ素層を形成する段階と、各層をNO中でアニールする段階と、各層をアンモニア中でアニールする段階とを含む。酸化物層と窒化ケイ素層とを併せた等価酸化膜厚は、最大25オングストロームである。 (もっと読む)

集積回路のトランジスタにおける金属ゲート構造および形成方法(高性能デバイスの金属置換ゲートのための構造および方法)

【課題】 高性能デバイスの金属置換ゲートのための構造および形成方法を提供する。

【解決手段】 まず、半導体基板(240)上に設けたエッチ・ストップ層(250)上に、犠牲ゲート構造(260)を形成する。犠牲ゲート構造(300)の側壁上に、1対のスペーサ(400)を設ける。次いで、犠牲ゲート構造(300)を除去して、開口(600)を形成する。続けて、スペーサ(400)間の開口(600)内に、タングステン等の金属の第1の層(700)、窒化チタン等の拡散バリア層(800)、およびタングステン等の金属の第2の層(900)を含む金属ゲート(1000)を形成する。

(もっと読む)

低GIDLMOSFET構造および製造方法

【課題】 従来のMOSFETデバイスに比べてGIDL電流が小さい低GIDL電流MOSFETデバイス構造を提供する。

【解決手段】 MOSFETデバイス構造は、縁部がソース/ドレイン拡散にわずかに重なる場合(82)がある中央ゲート導体と、薄い絶縁性の拡散バリア層によって中央ゲート導体から分離した側方ウイング・ゲート導体とを含む。また、側方ウイング・ゲート導体の左右の横方向の縁部が、前記ソース拡散領域および前記ドレイン拡散領域の一方に重なる場合(80)も含まれる。

(もっと読む)

481 - 490 / 490

[ Back to top ]