Fターム[5F140BG60]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | その他 (17)

Fターム[5F140BG60]に分類される特許

1 - 17 / 17

半導体装置

【課題】動作特性の劣化を抑えつつ、それぞれ適切な閾値電圧を設定された、メタルゲート電極を用いたn型およびp型のMISFETを混載する半導体装置を提供する。

【解決手段】半導体基板上に第1のゲート絶縁膜を介して形成された、第1の金属層および前記第1の金属層上の第1の導電層を含む第1のゲート電極を含むn型トランジスタと、半導体基板上に第2のゲート絶縁膜を介して形成された、前記第1の金属層よりも厚さが厚く、前記第1の金属層と構成元素の同一な材料からなる第2の金属層、および前記第2の金属層上の第2の導電層を含む第2のゲート電極を含むp型トランジスタと、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに異なる金属膜厚からなるゲート電極を有するn型及びp型MISトランジスタを備えた半導体装置において、ゲートリークによる劣化を抑制する。

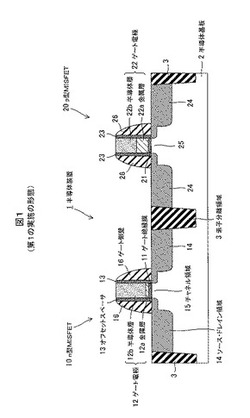

【解決手段】半導体装置は、第1のMISトランジスタと第2のMISトランジスタとを備える。第1のMISトランジスタは、第1の活性領域12a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成された第1の金属膜14a、及び、第1の金属膜14a上に形成された第1のシリコン膜17aを含む第1のゲート電極24Aとを備える。第2のMISトランジスタは、第2の活性領域12b上に形成された第2のゲート絶縁膜13bと、第2のゲート絶縁膜上に形成された第1の金属膜14b、第1の金属膜14b上に形成された第2の金属膜15b、及び、第2の金属膜15bの上に形成された第2のシリコン膜17bを含む第2のゲート電極24Bとを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】金属ゲートを形成した後に形成される絶縁膜中の水素の影響を抑制して、しきい値電圧Vthを所望の値(例えば0.3V)以下にすることを可能にする。

【解決手段】半導体基板11上に第1絶縁膜41が形成され、第1絶縁膜41に溝部42が形成され、溝部42の第1絶縁膜41側の半導体基板11上にサイドウォールスペーサ31が形成され、溝部42内にゲート絶縁膜21を介してゲート電極22が形成され、ゲート電極22の両側の半導体基板11にエクステンション領域23,24を介してソース・ドレイン領域25,26が形成され、第1絶縁膜41上にゲート電極22上を被覆する第2絶縁膜43を有し、サイドウォールスペーサ31は水素の通過を阻止する絶縁膜からなり、ゲート電極22上に水素の通過を阻止する水素バリア膜33が形成され、水素バリア膜33はゲート電極22上の周囲でサイドウォールスペーサ31と接続されている。

(もっと読む)

半導体材料及び金属材料を含む化合物のゲルマニウム酸化物層を介した基板内における選択的形成

【課題】基板がシリコン基板の場合に全体的にシリサイド化されるゲート(即ち、金属シリサイドから形成されるゲート)を得ることが可能な技術を提供する。

【解決手段】金属材料及び半導体材料からなる化合物から形成される領域16が、基板の表面の所定の部分にわたって3nm乃至5nmの厚さを有するゲルマニウム酸化物層を予め形成するとともに、表面1aの残りの部分にシリコン酸化物層12を予め形成することによって、半導体材料から形成される基板1に選択的に製作される。酸化物層上には金属層14が堆積される。金属材料は、その酸化物がゲルマニウム酸化物よりも熱力学的に安定し且つシリコン酸化物よりも熱力学的に安定しないように選択される。その後、熱アニーリングが行われることにより、前記金属材料によるゲルマニウム酸化物の還元が得られた後、基板1の表面1aの前記部分の高さで化合物が形成される。その後、金属層14が除去される。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極周辺の基板に生じるエッチングによる基板掘れを低減又は解消し、短チャネル効果を抑制しうる半導体装置の製造方法を提供することにある。

【解決手段】シリコン基板10上にゲート絶縁膜12を介してゲート電極14を形成する工程と、シリコン基板10上及びゲート電極14上に、シリコン基板10及びゲート電極14を覆うように、引張応力を有する引張応力膜22を形成する工程と、引張応力膜22を除去する工程と、引張応力膜22が除去されたゲート電極14をマスクとして不純物をシリコン基板10内に導入し、ゲート電極14の両側のシリコン基板10内に不純物層24を形成する工程とを有している。

(もっと読む)

半導体素子の製造方法

【課題】半導体素子の製造方法を提供する。

【解決手段】基板上に導電膜パターンを形成する。前記基板表面及び前記導電膜パターンの表面上に酸化膜を形成する。不純物の拡散に要求されるエネルギーが上昇するように前記酸化膜を表面処理して拡散防止膜を形成する。その後、前記拡散防止膜を通じて前記導電膜パターン両側の基板及び前記導電膜パターンに前記不純物を注入して、前記基板に不純物領域を形成する。前記方法によって形成される半導体素子は、導電膜パターン及び基板にドープされている不純物の拡散が減少して高性能を有する。

(もっと読む)

半導体装置の製造方法

【課題】NMOSFETおよびPMOSFETに適した組成のフルシリサイド相を、少ない工程数で、容易に得ることが可能な製造方法を提供すること。

【解決手段】基板1上に、ゲート絶縁膜2を介して前記NMOSFET用第1ゲート電極、およびPMOSFET用第2ゲート電極を形成する工程と、前記ゲート電極を覆う層間膜8を形成する工程と、前記層間膜8を平坦化し、前記第1、第2ゲート電極のシリコン層3を露出する工程と、前記第2ゲート電極の上部を選択的に除去する工程と、前記第2のゲート電極および第1のゲート電極のシリコン層3上に金属膜11を形成し、シリサイド化熱処理を行う工程と、熱処理工程後に未反応の金属膜を除去する工程と、を含み、第2のゲート電極上部を選択的に除去する工程の前に、前記第1および第2のゲート電極の各シリコン層3に、シリサイド相の組成制御のための不純物を同時に導入する工程を含む半導体装置の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】サリサイド構造を有する半導体装置において、接合リーク特性を劣化させずにゲート細線抵抗を向上することができる半導体装置を得ること。

【解決手段】シリコン基板1上にゲート絶縁膜12を介して形成されたポリシリコン膜14およびシリサイド膜15からなるゲート電極13と、ゲート電極13の下部のチャネル領域を挟んで形成された所定の導電型の不純物イオンが拡散された拡散層17、および拡散層17の表面に形成されるシリサイド膜18からなるソース/ドレイン領域と、を有する半導体装置において、ゲート電極13のシリサイド膜15の膜厚が、拡散層17上のシリサイド膜18の膜厚よりも厚い。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】リソグラフィ工程を追加することなく、様々な線幅およびレイアウトで配置された電極を、均一な組成でフルシリサイド化させることが可能な製造方法を提供する。

【解決手段】シリコン基板1上にポリシリコンからなるゲート電極5をパターン形成する。シリコン基板1上を絶縁膜11で覆った状態で、絶縁膜11から露出させたゲート電極5を覆ように第1金属材料を主成分とする第1金属膜31を成膜する。熱処理によってゲート電極5の表面層のみを第1金属膜と反応させる第1回目のシリサイド化を行い上層シリサイド膜33を形成する。次いで第1金属膜を除去する。上層シリサイド膜33を覆う状態で、第1金属材料よりも拡散速度の速い第2金属材料を主成分とする第2金属膜35を成膜する。上層シリサイド膜33で表面が覆われたゲート電極5の全層を熱処理によって第2金属膜と反応させる第2回目のシリサイド化を行い、ゲート電極5をフルシリサイド化させる。

(もっと読む)

MOSFETゲート電極のランディング・パッドのための構造および方法

マイクロエレクトロニクス・トランジスタおよび製作方法の性能および製造可能性を強化するための新たな技術を提供する。

【課題】

【解決手段】トランジスタ装置およびそれを形成する方法であって、基板と、基板上の第1のゲート電極と、基板上の第2のゲート電極と、第2のゲート電極に重なり合うフランジ付き端部の対を備えるランディング・パッドとを備え、第2のゲート電極の構造は、ランディング・パッドの構造と不連続である。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル長さ方向が<100>結晶軸方向に設置されたn型MISトランジスタを有する半導体装置において、電流特性の向上を効果的に実現する。

【解決手段】(100)結晶面を主面とするシリコン半導体基板の表面領域に、MISトランジスタを構成するための活性領域1と、活性領域1を囲む素子分離領域2とが形成されている。活性領域1の上には、ゲート絶縁膜7およびゲート電極3が形成されている。活性領域1およびゲート電極3の上には、引っ張り応力を有する応力制御膜5が形成されている。応力制御膜5のうちチャネル領域8からゲート幅方向の両側方に位置する部分は、応力制御膜加工領域6となっている。応力制御加工領域6とは、応力制御膜5が非設置の領域、または応力制御膜5が他の領域よりも薄い膜厚で形成されている領域のことをいう。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体プロセスの微細化に伴い、信頼性の高い微細なゲート電極の形成がより困難なものとなっている。

【解決手段】ゲート電極105の上面に加え、ゲート電極105の側面に対しても金属シリサイド110を形成することで、ゲート電極105を所望の太さの幅に拡大しなくても、信頼性の高いゲート電極105を形成することができる。

(もっと読む)

ゲートに近接したコンタクト・ホールを有する半導体トランジスタ

【課題】 デバイス密度を増加させるために、S/Dコンタクト・ホールが、トランジスタ構造体のゲートに近接して形成されるが、ゲートから電気的に絶縁された、トランジスタ構造体(及びその製造方法)を提供すること。

【解決手段】 構造体、及びその製造方法である。この構造体は、(a)第1のS/D領域と第2のS/D領域との間に配置されたチャネル領域と、(b)チャネル領域上のゲート誘電体領域と、(c)ゲート誘電体領域上にあり、かつ、ゲート誘電体領域によりチャネル領域から電気的に絶縁されたゲート領域と、(d)ゲート領域上の保護アンブレラ領域であって、保護アンブレラ領域は第1の誘電体材料を含み、ゲート領域が完全に保護アンブレラ領域の影の中にある、保護アンブレラ領域と、(e)(i)第2のS/D領域の真上にあり、これと電気的に接続され、かつ、(ii)保護アンブレラ領域のエッジと位置合わせされた充填されたコンタクト・ホールであって、コンタクト・ホールは、第1の誘電体材料とは異なる第2の誘電体材料を含む層間誘電体(ILD)層によってゲート領域から物理的に分離された充填されたコンタクト・ホールと、を含む。

(もっと読む)

ゲート電極構造及び製造方法

電界効果トランジスタ内に用いられるゲート電極構造及び集積回路及び製造方法が開示される。その方法と構造によって仕事関数と閾値調整が改善される。 (もっと読む)

半導体装置およびその製造方法

【課題】 p型チャネルを有する半導体装置において、前記p型チャネル領域に一軸性圧縮応力をSiGe混晶層より印加して、前記チャネル領域におけるホール移動度を向上させる。

【解決手段】 シリコン基板中、ソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層によりエピタキシャルに充填する際に、前記トレンチの側壁面を複数のファセットにより画成し、さらにSiGe混晶層中のGe原子濃度を20%を超えて増大させる。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されたゲート電極をCo膜を用いてシリサイド化する場合であっても、ゲート電極の抵抗のばらつきを抑制しうる半導体装置及びその製造方法を提供する。

【解決手段】ゲート長Lgが50nm以下のゲート電極30上に、Co膜72を形成する工程と、熱処理を行うことにより、Co膜72とゲート電極30とを反応させ、ゲート電極30の上部にCoSi膜76aを形成する第1の熱処理工程と、Co膜72のうちの未反応の部分を選択的にエッチング除去する工程と、熱処理を行うことにより、CoSi膜76aとゲート電極30とを反応させ、ゲート電極30の上部にCoSi2膜42aを形成する第2の熱処理工程とを有し、第1の熱処理工程では、CoSi膜76aの幅wに対するCoSi膜76aの高さhの比h/wが0.7以下となるように、CoSi膜76aを形成する。

(もっと読む)

キャリア移動度を増加させた電界効果トランジスタ

ある例示的な実施形態によれば、基板(104)上に位置するFETは、基板(104)中に位置するチャネル(112)を含んでいる。このFETはさらに、チャネル(112)上に位置する第1ゲート絶縁層(116)を含んでいる。この第1ゲート絶縁層(116)は、第1熱膨張係数を有している。FETはさらに、第1ゲート絶縁層(116)上に位置する第1ゲート電極(114)を含んでいる。この第1ゲート電極(114)は、FET中のキャリア移動度を増加させるように、第1熱膨張係数と異なる第2熱膨張係数を有している。この第2熱膨張係数は、例えば第1熱膨張係数よりも大きくされている。キャリア移動度の増加は、例えばチャネル(112)中に生成された引っ張り歪みにより引き起こされる。  (もっと読む)

(もっと読む)

1 - 17 / 17

[ Back to top ]