Fターム[5F140CA07]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 配線 (1,162) | 配線−電極、電極−電極間の絶縁構造 (47)

Fターム[5F140CA07]の下位に属するFターム

側壁による絶縁 (30)

Fターム[5F140CA07]に分類される特許

1 - 17 / 17

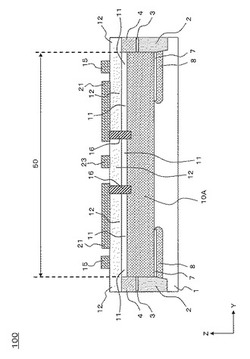

半導体装置およびその製造方法

【課題】トランジスタ間接続配線が吊りワード線と短絡してしまうのを回避すること。

【解決手段】第1の方向(X)に複数本並べて配置された活性領域(50)の各々は、第1の方向(X)と直交する第2の方向(Y)に離間して配置された2つの縦型トランジスタ(51)と、この2つの縦型トランジスタ(51)の間に位置するピラー(1a)と、から成る。半導体装置(100)は、複数本の活性領域(50)の中央の位置で、第1の方向(X)へ延在して配置された吊りワード線(23)と、2つの縦型トランジスタ(51)間を接続するために、第2の方向(Y)に延在し、かつ吊りワード線(23)を迂回するように構成されたトランジスタ間接続配線(21、10A、16)と、を備える。

(もっと読む)

半導体装置

【課題】デジタル回路と高周波回路とを混載した半導体装置において、デジタル回路の微細化を進めつつ、高周波回路の配線間容量を小さくする。

【解決手段】高周波回路100の第1トランジスタ120,140の第1ゲート電極124,144から第1コンタクト162,166までの距離aは、デジタル回路200の第2トランジスタ220,240の第2ゲート電極224,244から第2コンタクト262,266までの距離bより大きい。第1コンタクト162,166は第1トランジスタ120,140のドレイン126,146に接続しており、第2コンタクト262,266は第2トランジスタ220,240のドレイン226,246に接続している。

(もっと読む)

電界効果トランジスタ

【課題】従来の光学素子に電界効果トランジスタを適用するとき、PN接合部の光リークを抑えるために、トランジスタの周囲に遮光領域を設定する必要が有り、回路面積が大きくなるという課題があった。また、反射光に対して遮光性が十分でないという問題があった。

【解決手段】本発明の電界効果トランジスタは、ゲート電極上に、PN接合部に平面的に重なるように遮光部材を有する。この遮光部材により、PN接合部を遮光することができる。また、電界効果トランジスタ面積が増大しないため、回路の面積を小さく設定できる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート酸化膜の信頼性を阻害せずに、ゲート電極の低抵抗化を実現可能な半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、炭化珪素からなり、表面にエピタキシャル結晶成長層2が形成された半導体基板1と、エピタキシャル結晶成長層2上部に選択的に形成されたウェル領域3とを備える。そして、ウェル領域3上部に選択的に形成されたソース領域4と、ソース領域4とエピタキシャル結晶成長層2とに挟まれたウェル領域3の表面を覆うゲート絶縁膜6上に形成されたゲート電極7とを備える。ゲート電極7は、珪素層7aと、炭化珪素層7bとの積層構造からなり、ゲート電極7上部に形成されたシリサイド層7cをさらに備える。

(もっと読む)

半導体装置およびその製造方法

【課題】LDMOSFETの出力電力および負荷効率を向上させる。

【解決手段】相対的に上層のソース配線である配線29Aは、RFパワーモジュールの電流容量を満たすために厚い膜厚で形成し、1層目のソース配線である配線24Aは、配線29Aの膜厚の半分以下の膜厚で形成し、相対的に膜厚の厚い配線29Aではゲート電極7上を覆わずに、相対的に膜厚の薄い配線24Aでゲート電極7上を覆ってゲート電極7とドレイン配線との間をシールドする構造としてソース、ドレイン間の寄生容量(Cds)を低減する。

(もっと読む)

リセスチャネル構造を有するトランジスタを含む半導体装置およびその製造方法

【課題】特性異常の発生を低減することのできるリセスチャネル構造を有するトランジスタを含む半導体装置およびその製造方法を提供すること。

【解決手段】半導体シリコン基板の活性領域に設けられた第一のリセスおよび素子分離領域に設けられた第二のリセスと、リセスチャネル構造を有するトランジスタと、を少なくとも有する半導体装置であって、

前記トランジスタは、前記第一のリセス内部に設けられたゲート電極を有し、

前記ゲート電極は、前記第一のリセス内部に設けられた部分に加えて、前記第二のリセス内部に設けられた部分を有し、

前記第一のリセス内部に設けられた前記ゲート電極の部分と、前記第二のリセス内部に設けられた前記ゲート電極の部分とは、前記活性領域と前記素子分離領域との境界面と同一の面で互いに電気的に接続されていることを特徴とする半導体装置およびその製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生容量が低減され、優れた高周波特性を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板と、ゲート絶縁膜と、ゲート電極と、ドレイン領域およびソース領域と、基板上に形成された第1の層間絶縁膜と、第1の層間絶縁膜の上または上方に形成された第2の層間絶縁膜とを備えている。ドレイン領域はゲート電極とゲート長方向に離れて形成されている。第1の層間絶縁膜上には、ゲート電極とドレイン領域との間に設けられたフィールドプレートと、ゲート電極に接続され、ソース領域を跨いで延びる金属膜とが形成され、第2の層間絶縁膜上にはゲート電極を跨いでフィールドプレートの上方およびソース領域の上方を被い、フィールドプレートに接続された金属膜17bが形成される。

(もっと読む)

電界効果トランジスタ

【課題】出力特性劣化などの不具合の発生を抑え、良好な信頼性を得ることが可能な電界効果トランジスタを提供する。

【解決手段】化合物半導体基板11に形成される動作領域12、動作領域12上に形成されるゲート電極13と、動作領域12上にゲート電極13を挟んで交互に形成されるソース電極14及びドレイン電極15と、外部回路と接続されるためのボンディングパッド18、19と、ソース電極14又はドレイン電極15と接続される電極接続部20aと、ボンディングパッド18、19と接続されるパッド接続部20bと、電極接続部20a及びパッド接続部20b間を接続する空中配線部20cを有するエアブリッジ20を備え、夫々エアブリッジ20の幅方向の断面において、電極接続部20aの断面積が、空中配線部20cの断面積以下及び/又は電極接続部の幅が、空中配線部の幅より狭いことを特徴とする。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制できる構造であり、しきい値電圧を制御でき、電流駆動力に優れ、高速動作が可能なマルチフィンFETを有する半導体装置を提供することである。

【解決手段】上記の課題を解決した半導体装置の1態様は、半導体基板上に設けられたソース領域及びドレイン領域と、前記ソース領域及びドレイン領域を接続する複数のフィンと、前記半導体基板の上方に設けられ、前記各フィンを覆って設けられたゲート電極と、前記ソース領域若しくはドレイン領域から前記ゲート電極に向けて張り出し、隣接するフィンに接続して形成された張出し領域と、前記ゲート電極に接続する複数のパッド電極と、前記複数のパッド電極を接続する配線とを具備する。

(もっと読む)

埋め込みビットラインの形成方法

【課題】選択的無電解蒸着法を利用した埋め込みビットラインの形成方法を提供する。

【解決手段】埋め込みビットラインの形成方法は、基板をエッチングして形成されたビットライン用溝に無電解金属層を選択的に形成し、シリサイド工程を行ってビットライン用溝の内部にシリサイド膜を形成する。

(もっと読む)

金属エレクトロマイグレーション設計を有するRFパワートランジスタデバイス、及びその製造方法

メタル構造(70)を具備したRFパワートランジスタは、ドレインパッド(72)、及びドレインパッドから延在する複数の金属ドレインフィンガー(74)を有する。少なくとも1つの金属ドレインフィンガーは1つ以上の金属区画(74−1、74−2、100−1、100−2、100−3)を有し、各金属区画は、バンブーレジーム内に維持された金属幅を有する1つ以上の金属ブランチ(54−1、54−2、116−1、116−2、116−11、116−21、116−41)を含む。

(もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】応力印加膜の膜厚の増大が容易な半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置が,半導体基板,ゲート絶縁膜,ゲート電極,ゲート側壁絶縁膜,層間絶縁膜,配線層,層間接続部,応力印加膜と,を具備する。この応力印加膜は,半導体基板と層間絶縁膜との間に配置される第1の部分と,ゲート電極と層間絶縁膜との間に配置される第2の部分と,ゲート側壁絶縁膜と層間絶縁膜との間に配置される第3の部分と,貫通孔の内面と層間接続部との間に配置される第4の部分と,を有し,かつ半導体基板に応力を印加する。

(もっと読む)

半導体ウエハならびに半導体装置およびその製造方法

【課題】従来の半導体装置においては、チップ面積の縮小という面で改善の余地がある。

【解決手段】半導体装置1は、評価用トランジスタ10(第1の特性評価用素子)、評価用トランジスタ(第2の特性評価用素子)、測定パッド30(第1の測定パッド)、および測定パッド40(第2の測定パッド)を備えている。測定パッド30と測定パッド40とは、配線層中の相異なる層に設けられている。

(もっと読む)

MOSトランジスタおよびその製造方法

本発明のMOSトランジスタ(1)は、ゲート電極(10)、チャネル領域(4)、ドレインコンタクト領域(6)、および、前記チャネル領域(4)と前記ドレインコンタクト領域(6)とを相互に接続するドレイン拡張領域(7)を具える。前記MOSトランジスタ(1)は、前記ドレイン拡張領域(7)の上方に延在するシールド層(11)をさらに具える。このシールド層(11)と前記ドレイン拡張領域(7)との間の距離は、前記ゲート電極(10)から前記ドレインコンタクト領域(6)へ向かう方向に増加する。このような方法で、前記MOSトランジスタ(1)の横方向破壊電圧は、MOSトランジスタが基地局アプリケーションにおいて用いられるものよりも高い供給電圧のためのブロードキャストアプリケーションの耐久性要求を満足することができるレベルまで増加する。  (もっと読む)

(もっと読む)

半導体装置

【課題】 酸化膜と窒化膜の多層膜よりなるサイドウォールを有する半導体装置において、サイドウォールを構成する酸化膜がコンタクトエッチングの際にエッチングされてゲート電極の側面が露出するのを防ぐことができる半導体装置を得る。

【解決手段】 半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極上に形成された第1の窒化膜と、ゲート電極及び第1の窒化膜の側面に順番に形成された第1の酸化膜、第2の窒化膜、第2の酸化膜及び第3の窒化膜からなるサイドウォールとを有し、第1の窒化膜は、上部の外径が下部の外径よりも小さく、第1の酸化膜のゲート電極の側面にある部分は、上面から見て第2の窒化膜で覆われ、第2の酸化膜のゲート電極の側面にある部分は、上面から見て第3の窒化膜で覆われている。

(もっと読む)

半導体装置

【課題】 高電圧駆動のMISトランジスタを有する半導体装置であって、耐圧の向上と、微細化の向上が図られた半導体装置を提供する。

【解決手段】 本発明の半導体装置は、半導体層10と、

前記半導体層10の上方に設けられたゲート絶縁層20と、

前記ゲート絶縁層20の上方に設けられたゲート電極22と、

前記半導体層10に設けられたソース領域またはドレイン領域となる不純物領域28a,bと、

前記ゲート電極22と電気的に接続されたフィールドプレート電極44と、

前記フィールドプレート電極44を覆う絶縁層と、を含み、

前記絶縁層は、比誘電率が異なる領域を有し、比誘電率が高い領域は、前記導電層の一の端部に接している。

(もっと読む)

半導体装置

【課題】

酸化シリコン層、窒化シリコン層の積層ライナを備えたSTIを有し、帯電を低減できる半導体装置およびその製造方法を提供する。

【解決手段】

半導体装置は、シリコン基板と、前記シリコン基板の表面から下方に向かって形成され、前記シリコン基板の表面に活性領域を画定するトレンチと、前記トレンチの内壁を覆う酸化シリコン層の第1ライナ層と、前記第1ライナ層の上に形成された窒化シリコン層の第2ライナ層と、前記第2ライナ層の上に形成され、前記トレンチを埋める絶縁物の素子分離領域と、前記活性領域に形成されたpチャネルMOSトランジスタと、前記pチャネルMOSトランジスタを覆って,前記シリコン基板上方に形成され,紫外光遮蔽能を有さない窒化シリコン層のコンタクトエッチストッパ層と、前記コンタクトエッチストッパ層の上方に形成され、紫外光遮蔽能を有する窒化シリコン層の遮光膜と、を有する。

(もっと読む)

1 - 17 / 17

[ Back to top ]