Fターム[5F140DB10]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | シミュレーション (228) | その他 (19)

Fターム[5F140DB10]に分類される特許

1 - 19 / 19

半導体装置の製造方法

【課題】トランジスタのチャネル部に印加される応力を増加させて、電流増加効果を高めることを可能とする。

【解決手段】半導体基板上にダミーゲートを形成した後、該ダミーゲートの側壁に側壁絶縁膜を形成し、該ダミーゲートの両側の前記半導体基板にソース・ドレイン領域を形成する工程と、前記ダミーゲートおよび前記ソース・ドレイン領域の上に応力印加膜を形成する工程と、前記ダミーゲートの上の領域に形成された前記応力印加膜と前記ダミーゲートを除去して溝を形成する工程と、前記溝内の前記半導体基板上にゲート絶縁膜を介してゲート電極を形成する工程と、を備えた半導体装置の製造方法。

(もっと読む)

絶縁破壊寿命シミュレーション方法及びシリコンウェーハ表面の品質評価方法

【課題】実際のデバイスの絶縁破壊寿命に適合する精度の良いシミュレーションを行って、正確な絶縁膜の絶縁破壊寿命を求めることで、実測データとの対比で欠陥種、欠陥の大きさ等を正確に解析できる絶縁破壊寿命シミュレーション方法及びシリコンウェーハ表面の品質評価方法を提供することを目的とする。

【解決手段】前記シミュレーションする構造における、前記シリコンウェーハと前記絶縁膜の界面及び前記絶縁膜と前記金属電極の界面に、及び/又は、前記絶縁膜中に予め欠陥を組み込み、該欠陥を組み込んだ構造において、前記絶縁膜中に欠陥を乱数にて発生させて前記絶縁膜の絶縁破壊寿命を求める絶縁破壊寿命シミュレーション方法。

(もっと読む)

MOSFETモデル出力装置及び出力方法

【課題】寄生素子の効果が適切に取り入れられた高精度のMOSFETモデルを作成可能なMOSFETモデル出力装置及び出力方法を提供する。

【解決手段】MOSFETの形状データを入力するための形状データ入力部101を備える。前記形状データを利用して、前記MOSFETモデルに付加するための寄生素子モデルのパラメータを算出するパラメータ算出部102を備える。前記寄生素子モデルのパラメータを利用して、前記寄生素子モデルが付加された前記MOSFETモデルを作成して出力するMOSFETモデル出力部103を備える。そして、前記MOSFETモデル出力部は、前記MOSFETがN型MOSFETである場合とP型MOSFETである場合とで、前記MOSFETモデルに対し、異なる前記寄生素子モデルを付加する。

(もっと読む)

SPICEモデルパラメータ出力装置及び出力方法

【課題】高周波MOSFETやアナログMOSFETの基板抵抗を正確にモデル化することが可能なSPICEモデルパラメータ出力装置及び出力方法を提供。

【解決手段】MOSFETの形状データと、MOSFETの周波数特性に関する測定データとを入力するためのデータ入力部101と、測定データに基づいて、MOSFETに関する1端子基板抵抗モデルの基板抵抗を算出する基板抵抗算出部102〜105と、1端子基板抵抗モデルの基板抵抗と、形状データとに基づいて、SPICEモデルパラメータを算出して出力するSPICEモデルパラメータ出力部106とを備える。

(もっと読む)

高耐圧半導体装置および駆動回路

【課題】スイッチング応答速度が速い高耐圧トランジスタ、および電力損失および誤動作を抑制した駆動回路を提供すること。

【解決手段】高耐圧半導体装置は、p-型シリコン基板100上に設けられ、かつp-ウエル領域102に囲まれたn-型領域101と、ドレイン電極120と接続されるドレインn+領域103と、ドレインn+領域103と離れて設けられ、かつドレインn+領域103を囲むpベース領域105と、pベース領域105内に形成されたソースn+領域114と、を備える。また、n-型領域101を貫通し、かつシリコン基板100に達するp-領域131が設けられている。n-型領域101は、p-領域131により、n-型領域101aとn-型領域101bに分離されている。n-型領域101aは、ドレインn+領域103を備えている。n-型領域101bは、フローティング電位を有する。

(もっと読む)

基板ドレイン接続を有する横型MOSFET

1つの形式として、横型MOSFETは、ソース領域とドレイン領域との間に横方向に配されているアクティブゲートを含み、当該ドレイン領域は、単結晶半導体ボディの上面から単結晶半導体ボディの底面まで伸張し、横型MOSFETは、ドレイン領域の上に配されている非アクティブゲートをさらに含む。他の形式において、横型MOSFETは、ソース領域とドレイン領域との間に横方向に配されているゲートを含み、ドレイン領域は、単結晶半導体ボディの上面から単結晶半導体ボディの底面まで伸張し、ソース領域及びドレイン領域は第1の導電タイプであって、横型MOSFETは、ソース領域に接しておりかつソース領域の下方にある第2の導電タイプのヘビーボディ領域をさらに含み、ドレイン領域は、ゲートのエッジに近接しているライトドープドレイン(LDD)領域及び単結晶半導体ボディの上面から単結晶半導体ボディの底面まで伸張しているシンカーを含んでいる。  (もっと読む)

(もっと読む)

直列電界効果型トランジスタのパラメータフィッティング方法

【課題】 直列接続電界効果型トランジスタの回路モデルパラメータのフィッティング方法に関し、多段直列接続電界効果型トランジスタの回路モデルパラメータの効率的な抽出手順を提供し、モデル化を実施可能にする。

【解決手段】 多段直列接続電界効果型トランジスタの評価テスト用デバイスを用意し、複数のゲート電極に印加する電圧を制御して電気特性を評価し、パラメータ変数の基準値を孤立電界効果型トランジスタのモデル変数で設定し、さらに、パラメータ変数の微小変動分を加える形で回路モデルを作成し、次いで、評価した電気特性の多数のバイアス点とパラメータ変数の微小変動分の関係を、評価関数で評価し、評価関数を最小化することで微小変動分の変数の最適解を求め、最適解を多数の多段直列接続電界効果型トランジスタの評価テスト用デバイスについて求めてレイアウト変数の関数としてモデル化する。

(もっと読む)

半導体装置の評価方法、評価装置、および、評価プログラム

【課題】従来よりも正確な信頼性寿命を簡単に予測することのできる半導体装置の評価方法、評価装置、および、評価プログラムを提供する。

【解決手段】PMOSトランジスタのゲート電極にストレス電圧を一定時間印加するストレス電圧印加ステップS42と、一定時間の経過後、ドレイン電流Idを測定する測定ステップS43と、ゲート電極にストレス電圧より絶対値の小さい回復電圧を一定時間印加する回復電圧印加ステップS45と、一定時間の経過後、ドレイン電流Idを測定する測定ステップS46と、測定ステップS43で測定したドレイン電流Idと、測定ステップS46で測定したドレイン電流Idとから、ドレイン電流劣化率ΔIdと作動時間の関係を近似した近似式を求める近似ステップと、近似式のドレイン電流劣化率ΔIdに、信頼性寿命の判断基準となる数値を代入することにより、信頼性寿命を算出する算出ステップと、を含む。

(もっと読む)

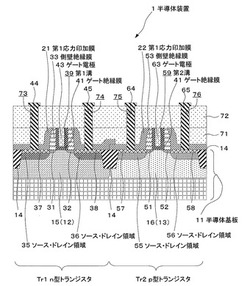

半導体装置

【課題】電流駆動能力が高いMOSFETを備えた半導体装置を提供する。

【解決手段】半導体装置1において、シリコン基板2の表面にNMOS3を形成し、NMOS3のチャネル領域7の直上域に、内部に圧縮応力を有する圧縮応力膜8を設け、シリコン基板2上における少なくともチャネル領域7の直上域の周囲に、内部に引張応力を有する引張応力膜9を設ける。

(もっと読む)

トランジスタのBT劣化のシミュレーションモデルおよびシミュレーションモデル化方法

【課題】過剰評価,過剰品質を招かない適正なレベルでのシミュレーションの実現。

【解決手段】トランジスタのドレイン端子,ソース端子,および基板端子のうちの少なくとも1端子のバイアス条件を他の端子と独立したバイアス条件として設定したうえで、設定したバイアス条件において前記トランジスタのモデルパラメータを変化させてなる、半導体集積回路におけるトランジスタのBT劣化のシミュレーションモデル。

(もっと読む)

半導体デバイス特性シミュレーション方法、半導体デバイス特性シミュレーション装置および半導体デバイス特性シミュレーションプログラム

【課題】新規開発デバイスの特性シミュレーションを高い精度で行うこと。

【解決手段】新規開発デバイスと構造や特性が近い既存デバイスモデルを用いてパラメータを補正しながらシミュレーションを行い、シミュレーションによる電極間容量が測定データと同等であると判定されたデバイスモデルに対して、その電流源モデルを測定データに基づいて作成した電流源モデルで入れ替え、電流源モデルを入れ替えたデバイスモデルを用いて特性のシミュレーションを行う。

(もっと読む)

絶縁膜の絶縁破壊寿命推定方法

【課題】実際の測定において検出可能な絶縁破壊が必ずしも最初の絶縁破壊でない場合においても、正しく最初の絶縁破壊寿命を推定する。

【解決手段】異なる面積の試料グループに属する各々複数の試料に対して各試料グループごとにワイブルプロットを行い、所定の累積不良率となる絶縁破壊寿命及びワイブルスロープを求め、各ワイブルスロープの試料面積に対する依存性を示すm値を求める。予め算出した試料内で最初の絶縁破壊までの絶縁破壊寿命のワイブルスロープとm値との相関関係に基づき、評価対象試料における最初の絶縁破壊までの絶縁破壊寿命のワイブルスロープを求める。各ワイブルスロープの面積依存性より、被測定試料における絶縁破壊寿命のワイブルスロープが、評価対象試料における最初の絶縁破壊までの絶縁破壊寿命のワイブルスロープとなる面積aを求める。各絶縁破壊寿命を面積に対してプロットし、面積aにおける絶縁破壊寿命を求める。

(もっと読む)

半導体装置

【課題】本発明は、bulk−FinFETにおいて、短チャネル効果の制御能力を向上できるようにする。

【解決手段】たとえば、bulk基板11の表面部に設けられたフィン12の両側面には、互いに対向するようにして、ゲート電極部21およびソース・ドレイン領域22,23が形成されている。また、ゲート電極部21の下部には、それぞれ、素子分離用絶縁膜13が設けられている。この素子分離用絶縁膜13は積層構造を有し、bulk基板11に接する下層側が、たとえば比誘電率が3.9程度のSiO2 膜13aによって、ゲート電極部21と接する上層側が、たとえば比誘電率が10以上の高誘電体膜13bによって、それぞれ形成されている。

(もっと読む)

半導体プロセスシミュレーション装置

【課題】転位の輪を考慮に入れた不純物拡散モデルを取り入れた半導体プロセスシミュレーション装置において、転位の輪の物理量を透過電子顕微鏡写真から抽出する時間と労力を低減した半導体プロセスシミュレーション装置を提供することを目的とする。

【解決手段】本発明に係る半導体プロセスシミュレーション装置イオン注入の際にシリコン基板中に導入される転位の輪の物理量を抽出するために用いる透過電子顕微鏡写真画像を取り込む画像データ入力部2001と、イオン注入工程後の熱処理工程における不純物の拡散に前記イオン注入工程により基板中に導入される転移の輪からの寄与を考慮した拡散モデルを用いて不純物拡散を行うプロセスシミュレーション装置計算部2002と、を備えている。

(もっと読む)

LSIのセルのライブラリデータ生成方法

【課題】微細化されたMOSトランジスタのソース、ドレインの抵抗値を正確に抽出して、より精度の高い入出力特性などを有するライブラリデータを生成することができるセルのライブラリデータ生成方法を提供する。

【解決手段】ソース、ドレイン領域の面積が第1の面積領域ではソース、ドレイン抵抗を面積Sに依存する抵抗値とし、面積が第1の面積領域よりも広い第2の面積領域では前記ソース、ドレイン抵抗を面積Sに依存しない固定抵抗値R0とする抵抗計算式によりまたは抵抗抽出参照ファイルを参照して、MOSトランジスタのソース、ドレイン抵抗を、当該ソース、ドレイン領域の面積に応じて抽出する抵抗抽出工程と、抵抗抽出工程で抽出されたソース抵抗、ドレイン抵抗を含むMOSトランジスタモデル及びその接続情報を有するネットリストと、入力信号とから前記セルの入出力特性を生成するシミュレーション工程とを有する。

(もっと読む)

半導体装置の検証方法および回路検証装置

【課題】 ESD保護回路を正確に、または迅速に、もしくは容易に検証することが可能な半導体装置の検証方法および回路検証装置を提供する。

【解決手段】 MOSトランジスタ素子からなるESD保護素子の等価回路として、ノードDとノードSの間に並列に接続されたNMOSトランジスタMN10およびそれに伴う寄生バイポーラトランジスタQN10と、寄生バイポーラトランジスタQN10のベースとノードDおよびノードSの間にそれぞれ設けられた電流源Ifgenおよび電流源Irgenと、寄生バイポーラトランジスタQN10のベースと基板ノードに該当するノードBとの間に設けられた基板抵抗Rsubとを用い、電流源Ifgen,Irgenのモデル式をその演算値が発散しないように変形し、また、このモデル式に電荷の生成および再結合を示す変数を組み込む。

(もっと読む)

高周波トランジスタの設計方法、および、マルチフィンガーゲートを有する高周波トランジスタ

【課題】高周波半導体回路のトランジスタユニットの各電極引き出しノードまでの配線およびコンタクトを最適化する。

【解決手段】配線およびコンタクトの構成に応じて変化する等価回路パラメータのうち、ゲート配線、ソース配線およびドレイン配線の各配線間の結合容量、ならびに、各配線と半導体基板と間の結合容量について、高周波トランジスタの高周波特性に対する感度を測定する(ステップST21)。この感度に基づいて、ゲート配線、ソース配線およびドレイン配線の階層レベルを各々決定する(ステップST22)。そして、決定した各階層レベルにおけるゲート配線、ソース配線およびドレイン配線のパターンと、各配線間あるいは配線とトランジスタ部とを接続するコンタクトの配置と大きさとを設計する(ステップST23)。

(もっと読む)

半導体装置の信頼性シミュレーション方法及び信頼性シミュレータ

【課題】 高精度のNBTI寿命モデルおよびTDDB寿命モデルを新たに作成し、該モデルを使用することにより、高精度で応用範囲の広いNBTI劣化シミュレーションおよびTDDB故障シミュレーションを実現する。

【解決手段】 半導体装置を構成するMOSトランジスタのNBTI劣化の予測値に基づき半導体装置の信頼性シミュレーションを行う際に、MOSトランジスタに対する累積NBTIストレス量を表すパラメータAgeを、Age=C・∫[(Ih/Area)m ]dt(但し、IhはMOSトランジスタのゲート絶縁膜を流れる正孔電流であり、AreaはMOSトランジスタのゲート面積であり、tはNBTIストレス時間であり、mはモデルパラメータであり、Cは比例定数である)で表されるモデル式を用いて算出する。

(もっと読む)

静電気放電保護回路のシミュレーション方法

【課題】ESD保護素子に等価回路を用いるESD保護回路のシミュレーション方法において、順方向バイアス及び逆方向バイアスに対して高精度なシミュレーションを行なえるようにする。

【解決手段】ESD保護素子の等価回路10は、n型MOSFET11、npn型寄生BJT12、電流源13、基板抵抗14及び寄生ダイオード15とを有している。npn型寄生BJT12のエミッタEはソース端子16と接続され、コレクタCはドレイン端子17と接続され、ベースBは基板抵抗14を介して基板端子19と接続されている。電流源13は、コレクタCとベースBとに接続されて、コレクタCからベースBに電流が流れるように配されている。寄生ダイオード15は、ドレイン端子17と基板端子19とに接続されて、基板端子19からドレイン端子17に順方向のダイオード電流が流れるように配されている。

(もっと読む)

1 - 19 / 19

[ Back to top ]