Fターム[5F152LN05]の内容

再結晶化技術 (53,633) | 格子整合、格子不整合技術 (1,553) | 目的 (706) | 歪みによる悪影響防止 (524) | 反りの低減 (63)

Fターム[5F152LN05]に分類される特許

1 - 20 / 63

半導体基板の接合方法

半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板、接着層、バッファ層および活性層がこの順に位置し、前記ベース基板の前記接着層と接する領域にSiが存在し、前記接着層、前記バッファ層および前記活性層が、窒化物半導体からなる半導体基板の製造方法であって、前記ベース基板をエピタキシャル結晶成長装置の成長室に設置した後に、前記ベース基板の温度を1000℃以上に維持しつつ前記ベース基板の表面をアンモニアガスとキャリアガスとの混合ガスに暴露するアンモニアガス暴露工程と、前記アンモニアガス暴露工程の後に、前記ベース基板の上に、前記接着層、前記バッファ層および前記活性層をエピタキシャル成長法により順次形成する層形成工程と、を有する半導体基板の製造方法を提供する。

(もっと読む)

半導体基板および半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

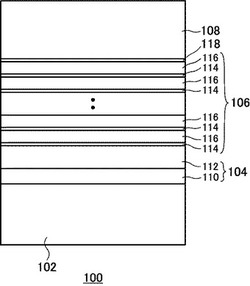

【解決手段】ベース基板、接着層、バッファ層および活性層を有し、前記ベース基板、前記接着層、前記バッファ層および前記活性層がこの順に位置し、前記ベース基板の前記接着層と接する領域にSiが存在し、前記接着層、前記バッファ層および前記活性層が、窒化物半導体からなる半導体基板であって、前記バッファ層が、第1結晶層と第2結晶層が交互に複数積層された積層構造体であり、前記第1結晶層が、AlmGa1−mN、(但し0≦m≦1)で表される結晶からなり、前記第2結晶層が、AlnGa1−nN、(但し0≦n≦1、m>n)で表される結晶からなり、前記第1結晶層の格子緩和度が、前記第2結晶層の格子緩和度より大きい半導体基板を提供する。

(もっと読む)

複合基板およびその製造方法、ならびに複合ウエハ

【課題】III族窒化物とは化学組成の異なる異組成基板とIII族窒化物層とが貼り合わされた複合基板であっても、反りおよびクラックを発生させることなくその複合基板上にIII族窒化物エピタキシャル層を形成することができる複合基板およびその製造方法を提供する。

【解決手段】本複合基板2Dは、III族窒化物以外の化学組成を有する異組成基板10と、異組成基板10に貼り合わされたIII族窒化物層21と、含み、III族窒化物層21は、平面充填が可能な少なくとも1種類の平面形状を有する複数のIII族窒化物タイル21pに分離している。

(もっと読む)

III族窒化物エピタキシャル基板およびその製造方法

【課題】デバイス化の工程で割れが発生することを抑制することが可能なIII族窒化物エピタキシャル基板およびその製造方法を提供する。

【解決手段】本発明のIII族窒化物エピタキシャル基板10は、Si基板11と、該Si基板11と接する初期層14と、該初期層14上に形成され、Al組成比が0.5超え1以下のAlGaNからなる第1層15A1(15B1)およびAl組成比が0超え0.5以下のAlGaNからなる第2層15A2(15B2)を順次有する積層体を複数組有する超格子積層体15と、を有し、前記第2層のAl組成比が、前記基板から離れるほど漸減することを特徴とする。

(もっと読む)

窒化物半導体エピタキシャル基板及び窒化物半導体デバイス

【課題】低転位であり、クラック発生を抑制できるIII族窒化物半導体層を有する窒化物

半導体エピタキシャル基板及び窒化物半導体デバイスを提供する。

【解決手段】基板上にAlを含むIII族窒化物半導体のバッファ層を介して成長した、C

面を表面とするIII族窒化物半導体層を有する窒化物半導体エピタキシャル基板であって

、前記バッファ層が、その表面にインバージョンドメインを有する。

(もっと読む)

半導体素子及びその製造方法

【課題】厚膜化が可能で、反りが小さく、かつリーク電流が小さい半導体素子を提供する。

【解決手段】基板と、基板の上方に形成された第1のバッファ領域と、第1のバッファ領域上に形成された第2のバッファ領域と、第2のバッファ領域上に形成された活性層と、活性層上に形成された少なくとも2つの電極とを備え、第1のバッファ領域は、第1半導体層と、第2半導体層とが順に積層した複合層を少なくとも一層有し、第2のバッファ領域は、第3半導体層と、第4半導体層と、第5半導体層とが順に積層した複合層を少なくとも一層有し、第4半導体層の格子定数は、第3半導体層と第5半導体層の間の格子定数を有する半導体素子。

(もっと読む)

半導体素子及びその製造方法

【課題】転位密度を低減させるバッファ層を有する半導体素子を提供する。

【解決手段】基板と、基板の上方に形成されたバッファ領域と、バッファ領域上に形成された活性層と、活性層上に形成された少なくとも2つの電極とを備え、バッファ領域は、第1の格子定数を有する第1半導体層と、第1の格子定数と異なる第2の格子定数を有する第2半導体層と、第1の格子定数と第2の格子定数との間の第3の格子定数を有する第3半導体層とが順に積層した複合層を少なくとも一層有する半導体素子。

(もっと読む)

半導体ウエーハ及び半導体素子及びその製造方法

【課題】クラックが少なく表面の平坦性が良好な半導体ウエーハ及び半導体装置及びその製造方法を提供する。

【解決手段】半導体ウエーハは、基板2と、基板2の一方の主面上に配置され且つ化合物半導体で形成されたバッファ領域3と、バッファ領域3の上に配置され且つ化合物半導体で形成された主半導体領域4とを有する半導体ウエーハであって、バッファ領域3は、第1の多層構造バッファ領域5と、基板と第1の多層構造バッファ領域5との間に配置された第2の多層構造バッファ領域8とから成る。

(もっと読む)

半導体基板及びその製造方法

【課題】単純な単結晶シリコン基板を出発基板として窒化ガリウム膜を形成することができ、反りやクラックが抑制された半導体基板及びその製造方法を提供する。

【解決手段】半導体基板10は、単結晶シリコン基板11と、前記単結晶シリコン基板11の最表面を除く表層領域に形成された転位層12と、前記単結晶シリコン基板11の前記最表面に形成されたバッファ層13と、前記バッファ層13の表面に形成された窒化ガリウム層14とを備えている。転位層12は、窒化ガリウム層14が形成された単結晶シリコン基板14の表層領域に転位が発生し且つ単結晶シリコン基板11の最表面には転位が発生しない条件下でイオン注入することにより形成される。イオン注入では、ドーズ量が5E+14atoms/cm2以上5E+17atoms/cm2以下のアルゴンイオンを注入する。

(もっと読む)

半導体素子およびその製造方法

【課題】異種基板上に高品質半導体結晶からなる島状のGaN系半導体層を基板の湾曲を抑えて成長させることができ、しかもGaN系半導体層が極めて厚くてもクラックなどの発生を抑えることができ、大面積の半導体素子を容易に実現することができる半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、GaN系半導体と異なる物質からなる基板11と、基板11上に直接または間接的に設けられ、一つまたは複数のストライプ状の開口12aを有する成長マスク12と、成長マスク12を用いて基板11上に(0001)面方位に成長された一つまたは複数の島状のGaN系半導体層13とを有する。成長マスク12のストライプ状の開口12aはGaN系半導体層13の〈1−100〉方向に平行な方向に延在している。

(もっと読む)

半導体積層構造体及びその製造方法

【課題】内部応力及び反りを低減させる。

【解決手段】まず、室温において、基板2の裏面上に、基板2よりも熱膨張率が低くかつヤング率が高い、Siを主成分とする酸化物又は窒化物からなる第1の膜3を成膜する(a)。次に、高温まで加熱した後に(b)、基板2の表面2a上に、AINからなるバッファ層4及び基板2よりも熱膨張率が高いIII−V族窒化物半導体からなる第2の膜5を成膜する(c)。しかる後、半導体積層構造体1の温度が室温まで低下すると、半導体積層構造体1は基板2及びすべての膜3、4、5がほぼ反りのない平坦なものとなる(d)。

(もっと読む)

シリコンウエハ及びその製造方法

【課題】ミスフィット転位や反りを低減できるシリコンウエハおよびその製造方法を提供する。

【解決手段】シリコン基板10と、ドナー濃度およびアクセプタ濃度間の差の絶対値が1×1018atoms/cm3以上で、かつ前記基板10上に設けられた第一のエピタキシャル層11と、ドナー濃度およびアクセプタ濃度間の差の絶対値が5×1017atoms/cm3以下で、かつ第一のエピタキシャル層11上に設けられ、該エピタキシャル層11と同じ導電型である第二のエピタキシャル層12と、を有し、第一のエピタキシャル層11に格子定数調整成分を添加して、シリコン単結晶の格子定数(aSi)に対する第一のエピタキシャル層11の格子定数(a1)の変化量((a1−aSi)/aSi)およびシリコン単結晶の格子定数に対する第二のエピタキシャル層12の格子定数(a2)の変化量((a2−aSi)/aSi)を臨界格子不整合度未満に調整する。

(もっと読む)

半導体基板

【課題】Si基板上にGaN結晶をエピタキシャル成長させた場合の基板の反り、またはGaN結晶の割れを抑制する。

【解決手段】ベース基板と第1結晶層と第2結晶層と機能層とを有し、ベース基板、第1結晶層、第2結晶層および機能層が、ベース基板、第1結晶層、第2結晶層、機能層の順に配置され、第1結晶層と第2結晶層とが格子整合または擬格子整合して接し、機能層の熱膨張係数が、ベース基板の熱膨張係数より大きく、第1結晶層の格子定数が、第2結晶層の格子定数より小さく、第1結晶層および第2結晶層が互いに接する第1界面と、機能層側に位置する第2結晶層の第2界面とを、同一視野に含んで断面TEM像を観察した場合、第1界面を含んで観察される第1モアレ画像の面積が、第2界面を含んで観察される第2モアレ画像の面積より小さい半導体基板を提供する。

(もっと読む)

積層体の製造方法、III族窒化物単結晶自立基板の製造方法、および、積層体

【課題】III族窒化物単結晶が積層された積層体を冷却したとしても、該積層体の反り(結晶軸の歪み)が低減できる製造方法を提供する。

【解決手段】ベース基板/第1のIII族窒化物単結晶層/第1の非単結晶層からなる積層基板を形成する工程、積層基板からベース基板を除去する工程、第1のIII族窒化物単結晶層上にIII族窒化物単結晶をエピタキシャル成長させて第2のIII族窒化物単結晶層を形成する工程、第2のIII族窒化物単結晶層上に、第2の非単結晶層を形成する工程、を含む積層体の製造方法。

(もっと読む)

多層膜付き単結晶基板、多層膜付き単結晶基板の製造方法および素子製造方法

【課題】多層膜の成膜により生じた反りを矯正すること。

【解決手段】単結晶基板20と、単結晶基板20の片面に形成された2つ以上の層を有しかつ圧縮応力を有する多層膜30とを含み、単結晶基板20をその厚み方向において2等分して得られる2つの領域20U、20Dのうち、少なくとも単結晶基板20の多層膜30が形成された面側と反対側の面側の領域20D内に、熱変性層22が設けられている多層膜付き単結晶基板、その製造方法および当該製造方法を用いた素子製造方法

(もっと読む)

半導体基板及び半導体基板の製造方法

【課題】半導体基板のアライメントマークを繰り返し使用する。

【解決手段】ベース基板にアライメントマークを形成する段階と、アライメントマークを形成する段階の後に、ベース基板上のアライメントマークを含む領域に、結晶成長を阻害する阻害層を形成する段階と、アライメントマークの位置を基準とする開口を形成すべき位置を示す情報に基づいて、阻害層におけるアライメントマークが設けられていない領域に、ベース基板を露出する開口を形成する段階と、開口内に半導体結晶を成長させる段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

III族窒化物結晶基板、エピ層付III族窒化物結晶基板、ならびに半導体デバイスおよびその製造方法

【課題】発光のブルーシフトが抑制された発光デバイスの製造に好適なIII族窒化物結晶基板、エピ層付III族窒化物結晶基板、ならびに半導体デバイスおよびその製造方法を提供する。

【解決手段】本III族窒化物結晶基板1は、III族窒化物結晶基板1の任意の特定結晶格子面のX線回折条件を満たしながら結晶基板の主表面1sからのX線侵入深さを変化させるX線回折測定から得られる特定結晶格子面の面間隔において、0.3μmのX線侵入深さにおける面間隔d1と5μmのX線侵入深さにおける面間隔d2とから得られる|d1−d2|/d2の値で表される結晶基板の表面層の均一歪みが1.7×10-3以下であり、主表面の面方位が、結晶基板のc軸を含む面から[0001]方向に−10°以上10°以下の傾斜角を有する。

(もっと読む)

III族窒化物エピタキシャル積層基板

【課題】基板の反り量を大きくすることなく、III族窒化物半導体の結晶性を向上させることが可能なIII族窒化物エピタキシャル積層基板を提供する。

【解決手段】基板2上に形成されたバッファ3と、その上にIII族窒化物層4をエピタキシャル成長する積層基板1であって、バッファ3は、基板2と接する初期成長層5ならびに初期成長層上に形成された第1超格子積層体6および第1超格子積層体上に形成された第2超格子積層体7からなり、第1超格子積層体6は、AlN材料からなる第1AlN層6aおよびGaN材料からなる第2GaN層6bを交互に5〜20組積層してなり、かつ、第1AlN層6aおよび第2GaN層6bの1組の厚みが44nm未満であり、第2超格子積層体7は、AlN材料またはAlGaN材料からなる第1層7aおよび該第1層とはバンドギャップの異なるAlGaN材料からなる第2層7bを交互に複数組積層する。

(もっと読む)

化合物半導体基板

【課題】基板の反りの低減とデバイスの高速性を高いレベルで実現することのできる化合物半導体基板を提供する。

【解決手段】

Si単結晶の基板と、基板の主面上に形成された窒化物半導体の中間層と、中間層の主面上に形成された窒化物半導体の化合物半導体層からなり、基板の酸素濃度が0.2×1018atoms/cm3以上1.4×1018atoms/cm3以下であり、抵抗値が1000Ωcm以上であり、前記中間層と前記化合物半導体層を合計した、主面と垂直方向の膜厚が450nm以上4500nm以下であることを特徴とする化合物半導体基板。

(もっと読む)

1 - 20 / 63

[ Back to top ]