Fターム[5F152NP30]の内容

再結晶化技術 (53,633) | 基板と活性層の間の層(バッファ層、マスク等)の材料 (2,042) | その他 (9)

Fターム[5F152NP30]に分類される特許

1 - 9 / 9

半導体ウエハの製造方法、複合基体および複合基板

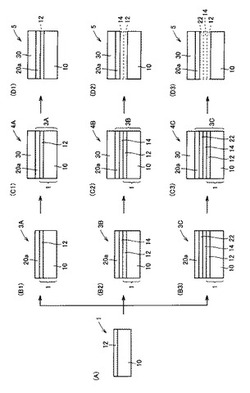

【課題】半導体デバイスを効率よく製造するために、基体の種類の如何を問わずに効率よく半導体ウエハを製造することができる半導体ウエハの製造方法、ならびにかかる製造方法に好適に用いられる複合基体および複合基板を提供する。

【解決手段】本半導体ウエハの製造方法は、基体10上に、表面のRMS粗さが10nm以下の基体表面平坦化層12を形成して複合基体1を得る工程と、複合基体1の基体表面平坦化層12側に半導体結晶層20aを貼り合わせて複合基板3A,3B,3Cを得る工程と、複合基板3A,3B,3Cの半導体結晶層20a上に少なくとも1層の半導体層30を成長させる工程と、基体表面平坦化層12をウェットエッチングで除去することにより、基体10から半導体結晶層20aを分離して、半導体結晶層20aおよび半導体層30を含む半導体ウエハ5を得る工程と、を含む。

(もっと読む)

エピタキシャルウェーハおよびその製造方法

【課題】デバイス活性層へのオートドーピングやミスフィット転位が発生し難く、且つ、デバイス形成後に薄厚化されても不純物金属によるデバイス活性層の汚染を有効に抑制することができるエピタキシャルウェーハおよびその製造方法を提供する。

【解決手段】シリコン基板の表面から内部に向かってV族原子を拡散させて形成した、濃度:2×1013atoms/cm3以上1×1018atoms/cm3以下のV族原子を含有してシリコン基板の表層に位置するバリア層と、バリア層上に形成したシリコンエピタキシャル膜よりなるデバイス活性層とを備えることを特徴とするエピタキシャルウェーハである。また、バリア層形成工程と、デバイス活性層形成工程とを含むエピタキシャルウェーハの製造方法である。

(もっと読む)

GaN系半導体エピタキシャル基板の製造方法

【課題】異種基板上にGaN系半導体を成長させることにより発生する貫通転位を低減し、低転位密度(例えば、105/cm2以下)のGaN系半導体をエピタキシャル成長させることができるGaN系半導体エピタキシャル基板の製造方法を提供する。

【解決手段】異種材料からなる成長用基板(例えばNGO基板)上にGaN系半導体をエピタキシャル成長させる際に、成長用基板上に、第1GaN系半導体層をエピタキシャル成長させ(第1工程)、第1GaN系半導体層における転位発生部分にエッチピットを形成し(第2工程)、エッチピットにSi3N4膜を選択的に形成し(第3工程)、Si3N4膜上に第2GaN系半導体層をエピタキシャル成長させる(第4工程)。

(もっと読む)

半導体ウエハの製造方法及び半導体ウエハ

【課題】格子不整合系基板を使用しながら、高品質な単結晶窒化物半導体の結晶成長を実現する半導体ウエハの製造方法を提供する。

【解決手段】半導体基板101の表面にグラフェン層110を設ける工程と、グラフェン層110の炭素原子の配列を示すハニカム構造の中心に、単結晶半導体層の結晶を構成する一の元素を吸着させる工程と、この一の元素に前記結晶を構成する当該元素とは異なる他の元素を結合させ、前記結晶の第1層114を形成する工程と、前記第1層の表面にさらに所定の層数の前記結晶半導体層を結晶成長する工程を備える。

(もっと読む)

低減した格子ひずみを備えた半導体材料、同様に包含する半導体構造体、デバイス、および、加工された基板を製造する方法

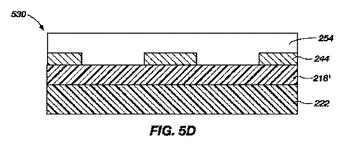

半導体装置を製作する方法または構造体は、従順な材料の層の上に横たわっている半導体材料の構造体を形成することを含み、その後半導体材料構造体を緩和させる従順な材料の粘性を変えて、緩和した半導体材料の連続層を形成する際の種子層として、緩和した半導体材料構造体を利用する。ある実施形態では、半導体材料の層は、III-Vタイプ半導体材料(例えばインジウム窒化ガリウム)から成る。新しい中間構造体が、この種の方法の間、形成される。加工された基板は、緩和した格子の構造体を有する半導体材料の連続層を含む。  (もっと読む)

(もっと読む)

SOI基板及び該基板の製造方法

【課題】SOI層の厚さのバラツキの無いSOI基板及び該SOI基板の製造方法を提供する。

【解決手段】シリコン基板上にエピタキシャル剥離層を介してALE成長でSOI層を形成し、ボデイウエーハを貼り付けた後、前記エピタキシャル剥離層を溶解除去することによって、全てがALE成長で作成したSOI層を形成し、

SOI層の厚さのバラツキの無いSOI基板とした。

(もっと読む)

窒化物系半導体素子の作製方法

【課題】 プラズマや活性イオンなどの衝突による結晶へのダメージの導入がなく、且つ多くの時間を必要としない方法で、窒化物系半導体層に分離溝を形成することにより、素子分離を容易にする窒化物系半導体素子の作製方法を提供する。

【解決手段】本発明に係る窒化物系半導体素子の作製方法は、主基板20の主面に所定の処理を施す事により、前記主面に、第1の領域20aと、前記第1の領域20aよりも結晶成長が起こりにくい第2の領域20bとを作製する領域作製工程と、前記主面に結晶成長により窒化物系半導体層1を形成する結晶成長工程と、前記第2の領域20bで、前記主基板20を前記主面に対して垂直方向に、前記第1の領域20a毎に分離する分離工程とを含むことを特徴とする窒化物系半導体素子の作製方法。

(もっと読む)

薄層を除去した後の多層構造を備えるウェハのリサイクル

半導体材料から選ばれた材料を含む有用層を除去した後にドナーウェハ(10)をリサイクル方法であって、ドナーウェハ(10)は基板(1)と多層構造(I)とを順次に備え、除去前の多層構造(I)は除去すべき有用層を備え、そのプロセスは除去が行われた側での物質除去を含み、物質除去の後に多層構造(I’)の少なくとも部分が残り、このバッファ構造(I’)の少なくとも部分は除去することができる別の有用層を1つ以上含み、有用層を再形成する補足的段階をともなわないことを特徴とする。本書はまた:本発明による少なくとも1つのリサイクル可能ドナーウェハ(10)から薄層を除去する方法、本発明によるリサイクル可能ドナーウェハ(10)に関する。  (もっと読む)

(もっと読む)

成長制御方法およびデバイス

【課題】複雑で高コストとなる処理工程を経ることなく、微小な構造の位置制御性およびサイズ均一性を高める。

【解決手段】第1の物質からなる基板の上に第2の物質を堆積させ、ステップが規則的に配列する二次元表面相11を形成する(S2)。ついで、二次元表面相11の上に第3の物質を配置することにより、二次元表面相11上のステップに第3の物質を含む液滴を配列させる(S3)。ついで、液滴島21を結晶化させることにより、微小構造22を形成する(S4)。

(もっと読む)

1 - 9 / 9

[ Back to top ]