Fターム[5F173AA26]の内容

半導体レーザ (89,583) | 半導体レーザの構造(垂直共振器を除く) (3,926) | 活性層がプレーナーでないもの(活性層が構造、形状分布を有するもの) (637) | 活性層の両側に設けられた半導体層により導波機構を実現するもの (524) | エッチングにより活性層を含むメサ部を形成してから埋め込んだBH構造 (438)

Fターム[5F173AA26]の下位に属するFターム

Fターム[5F173AA26]に分類される特許

1 - 20 / 417

半導体レーザ

光半導体素子及びその製造方法

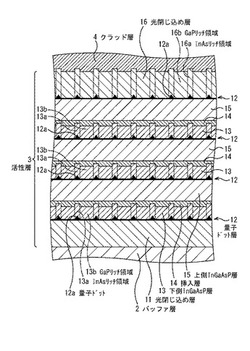

【課題】高い光利得を得ながら閾値電流値を低減することができる光半導体素子及びその製造方法を提供する。

【解決手段】基板の上方に形成された複数の量子ドット層12と、複数の量子ドット層12間に位置する中間層と、が設けられている。量子ドット層12に含まれる量子ドット12aの組成が、InxGa1-xAsySb1-y(0<x≦1、0<y≦1)で表わされる。中間層には、組成がInaGa1-aAsbP1-b(0<a<1、0<b<1)で表わされ、厚さが10nm以上40nm以下のInGaAsP層13、15と、InGaAsP層13、15の底面から10nm以上40nm未満の高さに位置し、厚さが0.3nm以上2nm以下のInP層14と、が含まれている。

(もっと読む)

光半導体装置及びその製造方法

【課題】容易且つ確実にTE−TM偏波間利得差を所期値以下に抑え、半導体基板間の製造ばらつきを低減し、製造ロット毎の歩留まりを大幅に向上させることを可能とする光半導体装置を実現する。

【解決手段】SOAは、半導体基板1と、半導体基板1の上方に形成され、量子ドット3を有する光学的に結合した単一の活性層5を備えた光導波路11とを含み、光導波路11は、TEモード偏波利得及びTMモード偏波利得の一方が他方よりも大きい第1の領域11aと、他方が一方よりも大きい第2の領域11bとを備えており、全体としてTEモード偏波利得とTMモード偏波利得との差が所定範囲内に調節されている。

(もっと読む)

光半導体装置の製造方法

【課題】信頼性を向上させることができる光半導体装置の製造方法を得る。

【解決手段】n−InP基板1上に、分離溝13で互いに分離された光半導体素子14,15を形成する。光半導体素子14,15の上面に、Ptを含む電極21,22をそれぞれ形成する。電極21,22に電気的に接続された電極24を形成する。電極24を給電層とした電解メッキ法により電極21,22上にAuメッキ層26,27をそれぞれ形成する。Auメッキ層26,27を覆うレジスト23をフォトリソグラフィにより形成する。レジスト23をマスクとして電極24をエッチングして電極21と電極22を電気的に分離する。電極24を形成する際に、分離溝13内に電極24が形成されないようにする。

(もっと読む)

光半導体素子、光送信モジュール、光伝送システム及び光半導体素子の製造方法

【課題】緩和振動周波数の温度による変化が小さい光半導体素子を提供する。

【解決手段】光半導体素子10は、活性層24を有するメサ部20と、メサ部20を埋め込む埋め込み層30と、を備え、埋め込み層30は、活性層24の屈折率の温度変化係数よりも大きい屈折率の温度変化係数を有し、且つ活性層24の屈折率よりも大きい屈折率を有する屈折率調整領域33を有し、屈折率調整領域33は、埋め込み層30の高さ方向において、活性層24と少なくとも一部が重なる位置に配置される。

(もっと読む)

半導体レーザ及びその製造方法

【課題】半導体レーザ(ストライプ状の活性層)が高密度に配置された半導体レーザを提供すること。

【解決手段】互いに離間してストライプ状に設けられた、複数の活性層10と、活性層10のそれぞれに対応して、活性層10の上側に設けられた複数の電極12と、半導体からなり、活性層10の間の領域にそれぞれに設けられ、電極12よりも高い位置にその上面が位置する支持部40と、複数の電極12のうち1つと電気的に接続されるとともに、複数の支持部40によって支えられて、当該複数の支持部40の間に位置する電極12と離間した構造を備える配線16と、を備えることを特徴とする半導体レーザ。

(もっと読む)

半導体レーザおよびその製造方法

【課題】無効なリーク電流を抑制し、高効率および高速動作を実現する。

【解決手段】p型InP半導体基板7上に、p型クラッド層4、活性層3、および、n型クラッド層2を有する活性層部からなる半導体レーザ部と、半導体レーザ部の両側を埋め込む電流狭窄層とを備えた半導体レーザの製造方法であって、前記電流狭窄層は、第一のp型InP層9、RuドープInP層5、および、第二のp型InP層11を有し、RuドープInP層5が、第一および第二のp型InP層9,11にのみ接するように形成する。当該構成を得るため、RuドープInP層5の成長の途中でハロゲン元素を含むガスを導入する、もしくは、RuドープInP層5の成長開始時にガスを導入し、成長途中でガス導入量を変え、RuドープInP層5の成長完了後にガス導入を停止させる。

(もっと読む)

光集積デバイス及び光集積デバイスの製造方法

【課題】光集積デバイスの素子と、素子との界面に流れる電流による、特性の劣化を抑える。

【解決手段】基板上に形成され、第1光路を有する第1導波路と、第1導波路上に形成された電極と、基板上に形成され、第2光路を有する第2導波路と、第1光路よりバンドギャップエネルギーが大きい材料で形成されて光路となる透明コアを有し、基板上の第1導波路及び第2導波路の間に形成された透明導波路と、を備え、電極は、第1導波路の上方に形成されており、かつ、透明導波路の上方には形成されておらず、第1導波路を有する素子は、電流注入により動作する光学的能動素子である光集積デバイスを提供する。

(もっと読む)

光増幅装置

【課題】PDGが小さい光増幅器をえる。

【解決手段】入射光の入力及び出射光の出力を行う入出力部と、入出力部から入力された入射光の偏光成分を分岐して、第1の偏光を有する第1偏光モード光、及び、第1の偏光と異なる第2の偏光を有する第2偏光モード光を出力する偏光分離部と、第1偏光モード光が入力され、第1の偏光を第2の偏光に変換して、第1偏光変換光を出力する偏光変換部と、導波路の一方の端部に入力された第1偏光変換光が増幅されて他方の端部から出力され、他方の端部に入力された第2偏光モード光が増幅されて一方の端部から出力される、光増幅部と、を備え、光増幅部に入力される光の、単位強度当たりの利得の変化の絶対値が、0.16dB/dBm以下である半導体光増幅器を用いることにより、PDG0.5dB以下の光増幅装置を提供する。

(もっと読む)

半導体光素子を作製する方法、及び回折格子を作製する方法

【課題】残渣による回折格子パターンの形成不良を低減可能な、半導体光素子を作製する方法を提供する。

【解決手段】凹凸部46bを設ける回折格子エリアは分離エリアに囲まれているので、回折格子エリア上の樹脂は分離エリアにおける平坦化樹脂層48より厚くなる。このように厚さむらの平坦化樹脂層48に起因して大きなパターン依存性を示さないように樹脂エッチングの条件を設定する必要があり、この場合において、厚さむらに起因する樹脂残渣が生成されるやすい。樹脂残渣の除去において、流量比R(フッ素系炭素の流量)/(酸素の流量)が1以下の範囲であるとき、SiNのエッチングレートは小さく、流量比Rが1より大きい流量比の範囲であるとき、SiNのエッチングレートは大きい。流量比Rが1以下の範囲であるとき、残渣処理における絶縁膜マスクの形状変化が小さい。

(もっと読む)

半導体光集積素子

【課題】利得領域の活性層の温度変化を抑えることができる半導体光集積素子を提供する。

【解決手段】半導体光集積素子1Aは、所定の光導波方向に並ぶ第1及び第2の領域10c、10dを含む主面10aを有する半絶縁性基板10と、第1の領域10c上に設けられ、n型クラッド層21、活性層22、及びp型クラッド層23を有する利得領域20と、第2の領域10d上に設けられ、下部クラッド層41、光導波層42、上部クラッド層43、及び抵抗体50(加熱部材)を有する波長制御領域40とを備える。半絶縁性基板10は、裏面10bから厚さ方向に延びて主面10aの第1の領域10cに至る貫通孔11を有しており、該貫通孔11の内部には、半絶縁性基板10の裏面10bからn型クラッド層21に達する金属部材12が設けられている。

(もっと読む)

光集積デバイス及び光集積デバイスの製造方法

【課題】マストランスポートを抑制したバットジョイントを有する光集積デバイスを得る。

【解決手段】基板と、マストランスポートが基板より遅い材料で基板上に形成され、基板のマストランスポートを抑制する抑制層と、抑制層上に形成された第1導波路層と、第1導波路層上に形成され、第1導波路層の端面より内側に端面を有する上部層と、抑制層上に形成され、第1導波路層の端面に接する第2導波路層と、を備える光集積デバイスを提供する。

(もっと読む)

光半導体素子の製造方法

【課題】絶縁層のクラックの発生を防止することが可能な光半導体素子の製造方法を提供する。

【解決手段】光半導体素子の製造方法は、半導体メサ16を埋め込む埋め込み樹脂領域18aを形成する工程(S6)と、第2絶縁層19a及びレジストマスク21を形成する工程(S8)と、レジストマスク21を用いてエッチングして開口25を形成する工程(S9)と、レジストマスク21を除去した後に、半導体メサ16の上面16s及び第2絶縁層19aの上に導電層26を形成する工程(S12)と、第2絶縁層19aを除去することにより第2絶縁層19aの上の導電層26bをリフトオフして半導体メサ16の上面16sに電極27を形成する工程(S13)と、電極27を熱処理する工程(S14)と、埋め込み樹脂領域18aの上に第3絶縁層28を形成する工程(S15)とを備える。

(もっと読む)

2次元光素子アレイ

【課題】半導体光素子にキャリアを注入することによって発生した熱の排熱効率を高くして、半導体光素子における、キャリアの再結合によるエネルギーから光への変換効率を高くする。

【解決手段】基板と、基板上の、第1の軸線、および、第1の軸線と所定の角度で交差する第2の軸線のいずれに対しても、所定の周期T1を有する位置に2次元的に配置され、キャリアが注入されて発光する活性層を有する複数の半導体光素子を備え、当該位置の少なくとも一つは、複数の半導体光素子のいずれもが形成されていない非光素子位置である、2次元光素子アレイを提供する。

(もっと読む)

半導体レーザ装置

【課題】新規な構造の分布反射レーザ装置である半導体レーザ装置を提供する。

【解決手段】半導体レーザ装置は、第1半導体層と、第1半導体層上の第1領域に形成された活性層と、第1半導体層上の第2領域に形成され、活性層から放出された光を導波する光導波層と、活性層および光導波層の近傍に配置され、活性層および光導波層を伝わる光を導波方向に反射させる回折格子と、活性層上および光導波層上に形成された第2半導体層と、光導波層上方で、第2半導体層上に形成された絶縁層と、第2半導体層上方に形成され、活性層上方から光導波層上方に延在し、活性層上方では第2半導体層に電気的に接続し、光導波層上方では第2半導体層との間に絶縁層が介在し、光導波層側に延在した部分に電圧が印加される電極とを有する。

(もっと読む)

半導体レーザ装置

【課題】12μm以上、18μm以下の波長を有する赤外線を出射可能な半導体レーザ装置を提供する。

【解決手段】半導体レーザ装置は、積層体と、誘電体層と、を有する。積層体は、量子井戸層を含む活性層を有し、リッジ導波路が設けられる。また、前記活性層は前記量子井戸層のサブバンド間光学遷移により12μm以上、かつ18μm以下の波長の赤外線レーザ光を放出可能な第1領域と、前記第1領域から注入されたキャリアのエネルギーを緩和可能な第2領域と、が交互に積層されたカスケード構造を有し、前記赤外線レーザ光を前記リッジ導波路が延在する方向に出射可能である。誘電体層は、前記リッジ導波路と直交する断面において、前記積層体の側面の少なくとも一部を両側から挟むように設けられる。前記誘電体層は、光の透過率が50%に低下する波長が16μm以上であり、前記活性層を構成するいずれの層の屈折率よりも低い屈折率を有する。

(もっと読む)

埋め込みヘテロ構造半導体レーザの製造方法及び埋め込みヘテロ構造半導体レーザ

【課題】耐圧特性を十分に維持しながら放熱特性を向上させることが可能な埋め込みヘテロ構造半導体レーザの製造方法等を提供する。

【解決手段】埋め込みヘテロ構造半導体レーザの製造方法は、半導体基板1上に半導体積層9とマスク層11を形成する工程と、マスク層11を用いて半導体構造物10をエッチングすることにより、第1方向に沿って延びる半導体メサ15であって、第1方向と直交する第2方向において被エッチング領域17と隣接する半導体メサ15を形成する工程と、マスク層11を半導体メサ15上に残した状態で、被エッチング領域17の第1領域17A1のみに埋め込み層19Aを形成する工程と、上部電極25を形成する工程と、を備える。上部電極25は、半導体メサ15の上面15Tから被エッチング領域17の第2領域17A2に亘って形成されることを特徴とする。

(もっと読む)

半導体レーザ

【課題】電極下に低誘電率の有機材料が挿入された構造であるにも関わらず、外力に対する破壊強度の低下を抑制して製造歩留まりを高めることができる半導体レーザを提供することにある。

【解決手段】光を出力する半導体レーザ部10aと、半導体レーザ部10aの出力側に設けられ、前記光を変調する光変調部10bとからなる素子本体10を、同一基板上に備え、光変調部10bは、前記光が導波する光導波層と、前記光導波層に隣接して設けられ、低誘電率の有機材料から成る埋め込み層12,13と、埋め込み層12,13の表面に設けられた第一の絶縁膜14と、第一の絶縁膜14の上に設けられ、前記光導波層へ電気信号を給電する上部電極16とを具備する半導体レーザであって、第一の絶縁膜14の上面および上部電極16の上面に第二の絶縁膜17を設けた。

(もっと読む)

半導体光反射器及び半導体レーザ、並びにそれらの駆動方法及び装置

【課題】導波路層に形成される屈折率分布のコントラストを従来よりも向上させた半導体光反射器及び半導体レーザ、並びにそれらの駆動方法及び装置を提供する。

【解決手段】n型基板11と、n型基板11自体の一部またはn型基板11の上方に形成されたn型クラッド層12と、n型クラッド層12の上方に形成されたp型クラッド層13と、p型クラッド層13とn型クラッド層12との間に形成された、光を導波するための導波路層14と、n型基板11の底面及びp型クラッド層13の上面にそれぞれ形成されたn型電極15及びp型電極16と、導波路層14の近傍に光導波方向に沿って規則的に配置された複数の電圧制御部材17と、を備え、複数の電圧制御部材17は、n型電極15及びp型電極16の間に逆バイアス電圧が印加された状態で、導波路層14内に光導波方向に沿った規則的な屈折率の分布を生じせしめる。

(もっと読む)

半導体レーザ素子の製造方法

【課題】回折格子に欠陥が生じることを抑制することが可能な半導体レーザ素子の製造方法を提供する。

【解決手段】半導体レーザ素子の製造方法は、モールド1を準備する工程と、半導体積層形成工程と、ストライプ構造形成工程とを備える。モールド1のストライプ状凹部は、2つの端部3Eと中央部3Mとを有し、2つの端部3Eの深さT3Eは、中央部3Mの深さT3Mよりも深い。半導体積層形成工程は、半導体層17を堆積する工程と、ストライプ状凹部3の形状を樹脂部21に転写し、樹脂部21に樹脂パターン部21Pを形成する工程と、樹脂パターン部21Pの形状を半導体層17に転写して回折格子17Pを形成する工程とを含む。ストライプ構造形成工程は、回折格子17Pの第3方向(Y軸方向)と直交する方向の両端部が除去されるように、半導体積層30をエッチングするエッチング工程とを含む。

(もっと読む)

1 - 20 / 417

[ Back to top ]