Fターム[5G013CB11]の内容

非常保護回路装置(断路なし) (2,677) | 過電圧の抑制方式 (331) | 2個形 (33)

Fターム[5G013CB11]の下位に属するFターム

Fターム[5G013CB11]に分類される特許

1 - 7 / 7

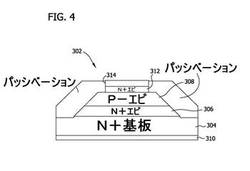

過渡電圧抑制器のための方法およびシステム

【課題】炭化シリコン過渡電圧抑制器(TVS)アセンブリを形成する方法および過渡電圧抑制器(TVS)アセンブリのためのシステムを提供する。

【解決手段】TVSアセンブリは、第1の極性の導電性を有する第1の広バンドギャップ半導体の第1の層306と、第1の層と電気的に接触して結合された第2の極性の導電性を有する第1または第2の広バンドギャップ半導体の第2の層308であって、第2の極性は第1の極性と異なる、第2の層とを含むメサ構造の半導体ダイ302を含む。TVSアセンブリはまた、第2の層と電気的に接触して結合された第1の極性の導電性を有する第1、第2、または第3の広バンドギャップ半導体の第3の層312も含む。第2の極性の導電性を有する層は、第1の極性の導電性を有する層に比して低濃度にドープされる。

(もっと読む)

電源装置及び照明器具

【課題】 高調波電流成分に対する対策とともに、過電圧に対する保護対策も実現できる電源装置及び照明器具を提供する。

【解決手段】 スイッチングトランジスタ24のオンオフによりスイッチングトランス23の二次巻線23bを通して放出されるエネルギーを整流平滑回路27により直流出力に変換し、この直流出力により発光ダイオード28〜31を点灯させる電源装置であって、交流電源11の交流電力を整流する全波整流回路12の出力端子に容量の小さな平滑用コンデンサ13と、容量の大きなコンデンサ15を有する過電圧吸収手段17をそれぞれ設け、容量の小さな平滑用コンデンサ13により全波整流回路12の出力に含まれる高調波電流成分について高調波電流規格を満足させ、容量の大きなコンデンサ15により交流電源11より侵入する雷サージの過電圧を吸収させる。

(もっと読む)

過電圧保護回路ならびにそれを用いた電源管理回路および電子機器

【課題】逆極性の電圧から回路を保護する。

【解決手段】メイントランジスタ10および逆流防止トランジスタ12は、入力端子102と出力端子104の間に直列に設けられる。入力ダイオード16は、逆流防止トランジスタ12とメイントランジスタ10の接続点N1と基準電圧端子106との間に、アノードが基準電圧端子106側となる向きで設けられる。制御部18は、直流電圧Vdcに応じてメイントランジスタ10のゲート電圧Vg1を制御する。逆流防止トランジスタ12は、そのボディダイオードD1のアノードが入力端子102側となる向きで配置される。入力端子102が高電位、基準電圧端子106が低電位となる正常状態において逆流防止トランジスタ12がオンするようにバイアスする。

(もっと読む)

避雷器及びそれを備えた接地端子盤

【課題】雷サージ吸収時における制限電圧を低くすることが可能であるとともに、続流の発生を抑制することが可能な避雷器及びそれを備えた接地端子盤を提供すること。

【解決手段】B種接地電極12bとD種接地電極12dとを有する接地端子盤10であって、B種接地電極12bとD種接地電極12dとの間に、コンデンサ21とギャップ式アレスタ22とが直列に接続された避雷器20を接続する。ギャップ式アレスタ22を用いることで、雷サージ電流吸収時における制限電圧を低く抑えることが可能となる。また、ギャップ式アレスタ22にコンデンサ21を直列接続することで、商業電源電圧による続流を抑制することが可能となる。

(もっと読む)

サージ吸収回路

【課題】高速信号に対してもインピーダンス整合に優れたサージ吸収素子を提供すること。

【解決手段】サージ吸収回路SA1は、相互に極性反転結合されると共に端同士が接続された第1の導体11及び第2の導体21と、第1の導体11及び第2の導体21と電気的に絶縁された第3の導体31とが形成された回路基板1Aと、一方の端子が第1の導体11と第2の導体21との接続部分に接続され、他方の端子が第3の導体31に接続されたサージ吸収素子3と、を備える。

(もっと読む)

系統連系システム

【解決手段】2つの電力系統間に系統連系されて、互いに電力系統の電力を供給し合うための系統連系システAであって、2つの電力系統間に、回路遮断器14と、電流検出器15と、スイッチ回路12aに、バリスタ12bとコンデンサ12cとの直列回路を並列に接続してなる限流器12と、該限流器12のスイッチ回路12aを制御する制御器13とからなる限流遮断器11を配置したものである。

【効果】限流器を、スイッチ回路と、該スイッチ回路に並列接続されたバリスタとコンデンサとの直列回路とにより構成したので、スイッチ回路の開放動作によるアーク放電を、バリスタとコンデンサの直列回路が短時間で小さい安全な電流にして、電力系統の事故時の瞬時停止や瞬時電圧低下を避け、重要負荷を保護することができる。

(もっと読む)

サージ吸収回路

【課題】

ICやLSI等の半導体デバイスは高圧の静電気によって破壊されたり、特性が劣化したりするため、静電気対策としてバリスタ等のサージ吸収素子が使用されている。バリスタを始めとするサージ吸収素子は浮遊容量成分や浮遊誘導成分を持つため、高速信号を扱う回路に適用すると信号を劣化させてしまう。浮遊容量と制御電圧・エネルギー耐量はトレードオフの関係にあるため、高速信号用途に対して特性のよいサージ吸収素子を適用できないという課題があった。

【解決手段】

上記目的を達成するために、本願発明に係るサージ吸収回路は、相互誘導素子等を利用してサージ吸収素子の浮遊容量成分の影響をキャンセルする。

(もっと読む)

1 - 7 / 7

[ Back to top ]