Fターム[5H420NB19]の内容

電気的変量の制御(交流、直流、電力等) (13,664) | 出力部 (2,015) | 複数の出力制御部を有するもの (81) | 直列接続されたもの (14)

Fターム[5H420NB19]に分類される特許

1 - 14 / 14

トンネル電流回路

【課題】消費電力の少ない基準電圧を発生する回路を、従来並みのサイズで提供することを目的とする。

【解決手段】

半導体接合に異なる電流密度の電流を流したときの差電圧に比例する電圧と、半導体接合に生ずる順方向電圧に比例する電圧とを加算して出力電圧とするバンドギャップリファレンス回路において、

前記差電圧が印加される第一のトンネル電流素子と、

第二のトンネル電流素子もしくは第二の複数のトンネル電流素子を直列接続した回路と、

前記第一のトンネル電流素子に流れる電流に比例した電流を前記第二のトンネル電流素子に流す手段によって、

上記「差電圧に比例する電圧」を発生させることを特徴とする。

(もっと読む)

定電流回路

【課題】面積の小さい定電流回路を提供する。

【解決手段】高い抵抗値の抵抗によらず、強反転領域の非飽和領域で動作するNMOSトランジスタ13の高い抵抗値のオン抵抗により、定電流回路の定電流IREFが少なくなる。NMOSトランジスタ13の面積はこのトランジスタのオン抵抗の抵抗値と同じ抵抗値の抵抗の面積よりも小さいので、定電流回路の面積が小さくなる。

(もっと読む)

特にナノアンペアオーダーの電流を生じる電流発生器、およびそのような発生器を用いる電圧調整器

【課題】特にナノアンペアオーダーの電流を生じる電流発生器、およびそのような発生器を用いる電圧調整器を提供する。

【解決手段】電圧調整器は、電流ミラーとして接続されていて、電源Vddに接続可能な3個のトランジスタP1、P2、P3の第1組41と、電流ミラーとして接続された2個のトランジスタN1、N2の第2組であって、各トランジスタが第1組のトランジスタに直列に接続されているトランジスタの第2組とを含み、第2組の第1トランジスタN1が、第1組の最後のトランジスタP3に直列に接続されたトランジスタN4に電流ミラーとして接続されたトランジスタN3Rに直列に接続されている。トランジスタN3Rは自身の線形領域で動作し、発生される電流の値は当該トランジスタの等価抵抗に依存し、2個のトランジスタが超長チャネルを有することにより比率L/Wが極めて大きい。

(もっと読む)

基準電圧回路

【課題】温度依存性を改善した基準電圧回路を提供する。

【解決手段】基準電圧回路100は、電源端子と接地端子の間に順に直列にスタックされた電流源30、第1バンドギャップリファレンス回路10および第2バンドギャップリファレンス回路20を備える。第1バンドギャップリファレンス回路10と第2バンドギャップリファレンス回路20はそれぞれ、互いに反対の温度係数を有する第1基準電圧Vref1、第2基準電圧Vref2を生成するよう構成される。基準電圧回路100は、第1基準電圧Vref1と第2基準電圧Vref2の和電圧Vref(=Vref1+Vref2)を出力する。

(もっと読む)

電圧発生回路

【課題】低消費電力および高精度な電圧発生回路を提供する。

【解決手段】例えば、電源電圧VCCと接地電源電圧GNDの間に、ソース−ドレイン経路が直列接続される複数のNMOSトランジスタMN1,MN2と、MN1,MN2をサブスレッショルド領域で動作させるための定電流源IS1を備える。MN1,MN2のゲートは、MN2のドレインに共通される。MN1のゲート幅W1およびゲート長L1とMN2のゲート幅W2およびゲート長L2は、例えば、L1=L2かつW2>W1とされる。これにより、MN1のドレイン電圧(Vout_2n)は、GNDを基準に正の温度特性となり、例えば、その後段で負の温度特性のデバイスを加算することで温度依存性が小さい電圧を生成できる。

(もっと読む)

半導体装置

【課題】低い電源電圧で駆動でき、かつ、電源電圧の変動に対して安定な基準電圧を生成するとともに、基準電圧の温度係数が製造工程におけるパラメータの変動に影響されにくい半導体装置を提供することである。

【解決手段】第1のトランジスタのコレクタ端子と第2のトランジスタのエミッタ端子とを接続して出力端子とし、第1のトランジスタのベース端子と第2のトランジスタのベース端子とを接続して第1のベース端子とし、第1のトランジスタと第2のトランジスタとは同一構造であり、第1のベース端子には、第1のトランジスタのエミッタ側pn接合がわずかに順方向バイアスされる動作領域から逆方向バイアスされる動作領域となる範囲の電圧を印加され、供給電圧には、第1及び第2のトランジスタがnpn、又はpnpかによって、正の電圧又は負の電圧を印加される半導体装置。

(もっと読む)

半導体集積回路装置

【課題】プロセスバラツキの影響を抑制し、低電圧動作に適した基準電圧発生回路を提供する。

【解決手段】第1トランジスタ(以下、Tr)と大きなエミッタ面積を持つ第2Trを有し、第1増幅回路により第1Trのベースとコレクタ電圧が等しくなるよう第1と第2Trのベース電流を形成する。第1抵抗は、第2Trのエミッタと基準電位との間に設けられてバンドギャップ電圧が印加される。第3TrのエミッタとVSSとの間に第2抵抗が、コレタク,ベースとVSSとの間に第3抵抗が設けられる。第1と第2抵抗の比により、第3Trのコレタク,ベースから出力される基準電圧の温度補償を行う。第2増幅回路は、第1と第2Trのコレタクが等しくなるよう第1ないし第3MOSのゲート電圧を形成し、第1ないし第3Trのコレタク電流をそれぞれ形成する。第1ないし第3MOSのソース側に第4ないし第6抵抗を設ける。

(もっと読む)

定電流・定電圧回路

【課題】基準電圧と基準電流を同時に得ることのできる定電流・定電圧回路を提供する。

【解決手段】基準電圧生成回路100の出力Vrefはオペアンプ102の−側入力端子に入力され、トリミングを行っても総抵抗値が変わらない基準電圧トリミング回路103の出力電圧Voutがオペアンプ102の+側入力端子に入力され、両方の電圧値が比較される。そしてオペアンプ102の出力が出力トランジスタ104のゲートを制御することでオペアンプ102の2つの入力が仮想短絡され、出力電圧Vref1を所望の値にする。出力電圧Vref1を調整する必要がある場合には抵抗R1,R2をトリミングする。トリミングを行っても総抵抗値が変わらないため安定して定電圧と定電流の両方を得ることができる。

(もっと読む)

電流ミラー回路、およびチャージポンプ回路

【課題】高耐圧系の回路へ出力電流を出力するとともに、回路面積を削減する。

【解決手段】MOSトランジスタ101は、基準電流源REF100からの基準電流Irefに応じたゲート電圧VGを生成する。MOSトランジスタ102は、バイアス電圧VBをゲートに受け、低耐圧トランジスタ101が破壊されないように中間ノード電位VN1を抑制する。電圧電流変換部103は、低耐圧系の回路であり、ゲート電圧VGに応じた出力電流Ioutを生成する。ゲイン制御部104は、低耐圧系の回路であり、制御信号Scntlに応じて、電圧電流変換部103における電圧電流変換係数を変更する。MOSトランジスタ105は、バイアス電圧VBを受け、電圧電流変換部103が破壊されないように、中間ノード電位VN2を抑制する。

(もっと読む)

基準電圧発生回路

【課題】発生させる基準電圧の電圧レベルが高くなった場合でも、基準電圧を所定の許容範囲内に調整することができる基準電圧発生回路を提供する。

【解決手段】モード切替回路12より、発生させる基準電圧に応じて当該基準電圧の電圧レベルが高くなるほど電流値の大きな供給電流を供給し、調整回路14により、供給電流の通電経路における所定位置の電圧を基準電圧Vrefとして出力すると共に、当該通電経路の抵抗値を変更することにより出力される基準電圧の電圧レベルを調整しており、基準電流制御回路16により、発生させる基準電圧の電圧レベルが高い場合に通電経路に通電される供給電流の一部を分岐させる。

(もっと読む)

基準電圧発生装置

【課題】温度変化/電圧変動に依存性しない複数出力の基準電圧発生回路。

【解決手段】電源電圧変動/温度変化の影響を受け無いバイアス電圧発生回路と、チャンネル幅とチャンネル長の比が実質的に等しい2つのNMOS型トランジスタを直列に接続して構成した第1〜第H(Hは2以上の正の整数)の直列回路と、これらの直列回路に電流を供給する電流供給源とを備え、前記夫々の直流回路を構成するNMOS型トランジスタのゲートとドレインとを接続し、前記第1の直列回路の一方のNMOS型トランジスタのゲートに前記バイアス電圧発生回路の直流出力電圧を印加し、他方のNMOS型トランジスタの出力端子に前記直流出力電圧の2倍の直流出力電圧を発生させ、第H−1の直列回路の出力電圧を第Hの直列回路の相互接続点に印加し、他方のNMOS型トランジスタの出力端子に前記バイアス電圧発生回路の直流出力電圧に(H+1)倍の直流出力電圧を発生させる。

(もっと読む)

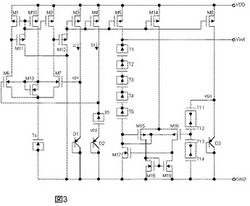

半導体装置用の内部電圧発生器

【課題】電源電圧の変動と無関係に一定の電圧を出力することができる半導体装置用の内部電圧発生器を提供すること。

【解決手段】電源電圧と第1ノードaの間に接続された第1トランジスターP3、第1ノードと第2ノーcの間に接続された第2トランジスターN2、電源電圧と第3ノードbの間に接続された第3トランジスターP4、第3ノードと第2ノードの間に接続された第4トランジスターN4、及び第2ノードと接地の間に接続された第5トランジスターN3を備え、第1及び第3トランジスターのゲートがともに第1ノードに接続されているカレントミラー部201と、カレントミラー部の第1及び第3ノードからの出力信号によって制御される第1ドライバー202と、第1ドライバーの出力信号によって制御される第2ドライバー203と、第2ドライバーの出力ノードと接地の間に接続された分圧器204とを具備する。

(もっと読む)

基準電圧発生回路及びこれを用いた電源電圧監視回路

【課題】 低い電源電圧でも高精度な基準電圧を発生できると共に、外部から印加される初期化信号や複数の定電流源を必要とすることなく、回路の安定した起動を実現できる基準電圧発生回路を提供する。

【解決手段】 この基準電圧発生回路は、2つのPN接合を含む回路に発生する2つの電圧を入力して出力電圧を生成する差動増幅部と、2つのPN接合に電流を供給する電流供給部と、起動信号に従って差動増幅部の動作を第1の安定状態から第2の安定状態に移行させるために電流供給部を制御する制御部とを含み、差動増幅部の出力電圧に基づいて生成された第1の電圧を分圧して基準電圧として出力する定電圧回路20と、第1の電圧に基づいて差動増幅部の動作が第1の安定状態を経過するまで起動信号を活性化する起動回路10と、起動信号が活性化されているときに第1の電圧を減少させる起動促進回路30とを具備する。

(もっと読む)

定電圧電源回路

【課題】 出力電流の制限値が測定装置の測定範囲を超えた場合でも該測定装置で制限電流値を測定することができる、電流制限回路を備えた定電圧電源回路を得る。

【解決手段】 制限電流測定時には、測定装置から負荷10に、所定の定電圧V1よりも少し小さい電圧Vsが印加されると共に、該測定装置によってテスト信号S1をハイレベルにして負荷10に大きな電流を流し、入力電圧VddとNMOSトランジスタM4のドレインとの間に接続される抵抗値を、抵抗R4と抵抗R3の各抵抗値の和になるようにして、通常動作時と比較して小さい電流値で出力電流ioの電流制限がかかるようにした。

(もっと読む)

1 - 14 / 14

[ Back to top ]