Fターム[5H730BB83]の内容

DC−DCコンバータ (106,849) | 主変換部の型式 (20,669) | 変換部を複数持つもの (3,223) | 並列に持つもの (1,239) | 変換部の一部を共用するもの (227)

Fターム[5H730BB83]に分類される特許

221 - 227 / 227

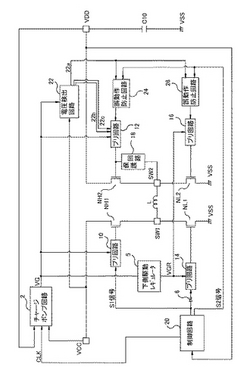

電源回路

【課題】NMOSNH2の保護を行う際、ツェナーダイオードに流れる電流を制限することで電源回路の効率の悪化を防止する電源回路を提供する。

【解決手段】入力電圧および出力電圧を用いて、第1のN型MOSFETおよび第3のN型MOSFETのゲート電圧を得るための共用電圧として、前記入力電圧および前記出力電圧より高い昇圧電圧を発生する昇圧電圧発生回路と、前記昇圧電圧に基づいて、第2のN型MOSFETとともにスイッチング動作する前記第1のN型MOSFETと、前記第3のN型MOSFETとをオンさせる制御回路と、前記第3のN型MOSFETのゲート・ソース間に接続され、前記第3のN型MOSFETのゲート・ソース間電圧が前記入力電圧の大きさに応じて所定電圧以上となるときに両端に定電圧を発生するツェナーダイオードと、前記ツェナーダイオードに流れる電流を所定値に制限する電流制限回路と、を備えた。

(もっと読む)

電源回路

【課題】出力電力が所定の値より小さい場合の効率を改善することができる電源回路を提供する。

【解決手段】入力電圧がドレインに印加され、入力電圧より高いゲート電圧でオンする第1のN型MOSFETと、第1のN型MOSFETと直列接続されるとともに、ダイオードと並列接続される第2のN型MOSFETと、第1のN型MOSFETと並列接続されるスイッチング素子と、第1のN型MOSFETのゲート電圧を得るための昇圧電圧を発生する昇圧電圧発生回路と、昇圧電圧に基づいて第1のN型MOSFETを第2のN型MOSFETとスイッチングすることによって、出力電圧を得る第1のモード、または昇圧電圧に関わらずスイッチング素子をスイッチングするとともに第1のN型MOSFETと第2のN型MOSFETをオフすることによって、出力電圧を得る第2のモードを選択的に実行する制御回路と、を備えた。

(もっと読む)

電源回路

【課題】入力電圧の変化に応じてゲート・ソース間電圧が変化するNMOSが破壊することを防止することで、使用電圧範囲の広い電源回路を提供する。

【解決手段】入力電圧および出力電圧を用いて、第1のN型MOSFETおよび第3のN型MOSFETのゲート電圧を得るための共用電圧として、入力電圧および出力電圧より高い昇圧電圧を発生する昇圧電圧発生回路と、前記昇圧電圧に基づいて、第2のN型MOSFETとともにスイッチング動作する前記第1のN型MOSFETと、前記第3のN型MOSFETとをオンさせる制御回路と、前記第3のN型MOSFETのゲート・ソース間電圧が前記入力電圧の大きさに応じて所定電圧以上となるときに動作して、前記第3のN型MOSFETを保護する保護回路と、を備えた。

(もっと読む)

電源供給装置

【課題】直流電源のプラスとマイナスとを逆接によって流れる過電流を防止した電源供給装置を提供する。

【解決手段】バッテリB−LED20間に設けられたMOSFETQ1及びDC/DCコンバータ11から構成される直流回路を備えている。DC/DCコンバータ11は、MOSFETQ1とLED20との間に設けられるコイルL1、順方向がコイルL1に向くように、コイルL1上流側−グランド間に設けられたダイオードD1及びコイルL1下流側−グランド間に設けられたコンデンサC1を有する。コイルL1上流側−グランド間に、ダイオードD1と直列に、バッテリBの逆接続時にオフするMOSFETQ2を設ける。

(もっと読む)

DC−DCコンバータ回路

【課題】解決しようとする問題点は従来の複数電圧出力タイプDC−DCコンバータは小型化及び低コスト化が困難であった点と、エネルギーの変換効率が悪かった点である。

【解決手段】コイルと該コイルのエネルギー蓄放電を制御するスイッチング素子とを直列接続した電圧可変回路と、該コイルと該スイッチング素子との間に接続され、出力制御用スイッチング素子と出力電圧モニター手段とを有する複数の出力回路と、各出力電圧モニター信号が入力される制御回路とを設け、該制御回路が、1つの制御サイクルで、1つの前記モニター信号に応答して前記蓄放電制御用スイッチング素子と当該出力回路の出力制御用スイッチング素子を制御して当該出力回路の出力電圧を調整すると共に、該制御サイクルを時分割的に複数設けて前記複数の出力回路の出力電圧を時分割的に順次繰り返し制御する。

(もっと読む)

インターリーブパワーコンバータ

パワーコンバータのアーキテクチャは、フルブリッジコンバータをインターリーブすることで、高電流印加時の熱管理問題を緩和でき、例えば、パーツ数およびコストを削減しながら、出力能力を倍にし得る。例えば、3位相インバータの1位相は、2つの変圧器間で分かち合われる。これら2つの変圧器は、2つの整流手段を有する整流器のような整流器に出力を提供し、4つの高電圧インバータレグよりも、むしろ、3つの高電圧インバータレグを有する2つのフルブリッジDC/DCコンバータを提供する。  (もっと読む)

(もっと読む)

カスケードバック段を有する配電システム

マイクロプロセッサまたは他のASICのための配電システムである。配電システムは、直列に接続された複数のカスケードバック段であって、複数のカスケードバック段における最後のバック段が、複数のカスケードバック段の第1バック段に印加された入力電圧Vinに応じて出力電圧Voを供給する、カスケードバック段、を含む。負荷サイクル制御が、各バック段の負荷サイクルを制御して出力電圧Voを維持する。負荷サイクル制御は、入力対出力電圧比率(Vin/Vo)が、入力対出力電圧比率の閾値RTよりも低い場合に、複数のカスケードバック段の第1バック段の負荷サイクルを1に設定する。  (もっと読む)

(もっと読む)

221 - 227 / 227

[ Back to top ]