Fターム[5H730BB83]の内容

DC−DCコンバータ (106,849) | 主変換部の型式 (20,669) | 変換部を複数持つもの (3,223) | 並列に持つもの (1,239) | 変換部の一部を共用するもの (227)

Fターム[5H730BB83]に分類される特許

161 - 180 / 227

昇圧型スイッチングレギュレータ

【課題】高倍率昇圧においても負荷電流を引け、電池を入力電源とした場合に、電池電圧が低下して昇圧倍率が高くなっても所望の出力電圧を得られ、電池寿命を長くすることが可能な昇圧型スイッチングレギュレータを提供する。

【解決手段】チョッパ方式昇圧型スイッチングレギュレータにおいて、チョッパ用コイルに中間端子を設けて、コイルの中間端子をスイッチング素子と接続する構成で、スイッチング素子のオン期間に流れる電流をチョッパ用コイルの一部を用いて磁気的なエネルギーを蓄積し、スイッチング素子のオフ期間に蓄積されたエネルギーをチョッパ用コイルの全部を利用して負荷側に移行させる構成とした。

(もっと読む)

スイッチング電源装置と半導体集積回路装置及び電源装置

【課題】高速応答でしかも安定動作を行うスイッチング電源装置、半導体集積回路装置及び電源装置を提供する。

【解決手段】インダクタの出力側と接地電位との間にキャパシタを設ける。第1パワーMOSFETにより入力電圧からインダクタの入力側に電流を供給し、第1パワーMOSFETがオフ状態のときにオン状態となる第2パワーMOSFETによりインダクタの入力側を所定電位にする。インダクタの出力側から得られる出力電圧に対応した第1帰還信号と、第1パワーMOSFETに流れる電流に対応した第2帰還信号とを用いてPWM信号を形成する。第1パワーMOSFETを縦型MOS構造のセルの複数個で構成し、セル数が1/Nにされて第1パワーMOSFETとゲート及びドレインがそれぞれ同一半導体基板で共通にされた検出MOSFETを設けて第2帰還信号を形成する。

(もっと読む)

電力変換装置

パワーコンバータは、トランスと、主スイッチと、補助スイッチと、第1及び第2の共振コンデンサと、二次側に配設された整流手段とを備える。トランス共振用のエネルギ源として、反射した電圧及び寄生容量を用いるスイッチモード電源を構成する。補助スイッチは、トランスの一次側インダクタンスと、第1及び第2の共振コンデンサとの間で、エネルギを有効に交換する。また、補助スイッチは、トランス共振を、2つの個別の周波数の間で切り換える。本発明の一実施の形態においては、パワーコンバータは、以下に限定されるものではないが、フライバックコンバータであってもよく、更に、第2の共振コンデンサに亘る電圧を検出する比較器と、駆動手段とを備えていてもよい。駆動手段は、この比較器の出力に基づいて補助スイッチを駆動する。コンバータの共振特性によって、主スイッチ及び補助スイッチのゼロ電圧スイッチング(ZVS)が実現する。  (もっと読む)

(もっと読む)

フェライト積層部品、及びこれを用いたマルチフェ−ズコンバ−タ

【課題】 マルチフェ−ズコンバ−タに、好適な複数のインダクタを備えたフェライト積層部品と、これを用いたマルチフェ−ズコンバ−タを提供する。

【解決手段】 上主面及び下主面と、前記上下主面間を連結する側面を備え、コイル用導体と磁性体とを積層して、一体焼成した積層体の内部に、前記コイル用導体によりコイルを形成したフェライト積層部品であって、前記コイルが、マルチフェ−ズコンバ−タの複数のインダクタを形成する。

(もっと読む)

多出力スイッチング電源装置

【課題】多出力スイッチング電源装置の何れかの2次巻線への電流集中を軽減すると共に、各々の2次側出力回路で発生する電力損失を低減する。

【解決手段】本発明による多出力スイッチング電源装置は、直流電源(1)に直列に接続されたトランス(2)の1次巻線(2a)及び主MOS-FET(3)と、1次巻線(2a)と逆極性で結合する第1及び第2の2次巻線(2b,2c)に各々接続された第1及び第2の整流平滑回路(6,15)と、第1の整流平滑回路(6)の出力電圧VO1に応じて主MOS-FET(3)をオン・オフ制御する主制御回路(9)と、第2の2次巻線(2c)と第2の出力平滑コンデンサ(14)との間に接続された出力制御用MOS-FET(18)と、出力制御用MOS-FET(18)と第2の出力平滑コンデンサ(14)との間に接続されたリアクトル(31)と、第2の整流平滑回路(15)の出力電圧VO2に応じて出力制御用MOS-FET(18)をオン・オフ制御する出力制御回路(19)とを備える。

(もっと読む)

大電流発生方法および装置

【課題】エネルギー分配による損失が無く、原理的に出力電流値に上限のない大電流発生装置を提供する。

【解決手段】制御回路7は、並列接続用スイッチ5-1,…,5-N+1および6-1,…,6-Nをオフした状態で直列接続用スイッチ4-1,…,4-Nおよび励磁スイッチ3をオンする。次に、励磁電流が予め与えた値Ioになると、励磁スイッチ3をオフすると共に並列接続用スイッチ5-1,…,5-N+1および6-1,…,6-Nを全てオンする。次に、直列接続用スイッチ4-1,…,4-Nをオフする。

【効果】エネルギー分配による損失が無くなる。負荷の抵抗値はかなりの自由度をもって選ぶことが出来る。原理的に出力電流値に上限がなくなる。

(もっと読む)

電源装置およびそれを搭載した画像形成装置

【課題】擬似負荷の消費電力を大きくすることなく、精度の良いスイッチング電源装置およびそれを搭載した画像形成装置を提供する。

【解決手段】二次電圧Vbの出力がツェナーダイオード35のツェナー電圧Vzで設定される電圧以上になるとトランジスタ36がオンし、二次電圧Vbがフィードバックされる。抵抗37で決まる電流によりフィードバックされたVbが二次電圧Vaのフィードバックとバランスをとりながら電源コントローラ32のFB端子電流を制御する。二次電圧Vaの精度を許容範囲内に抑えつつ、二次電圧Vbの急激な上昇を抑制することができる。

(もっと読む)

昇圧装置および降圧装置

【課題】平滑容量を持たない基準電源を有する昇圧装置において、デッドタイム期間に発生する基準電源へのノイズを低減する。

【解決手段】昇圧電圧蓄積用の容量素子C0に対して並列接続された第1、第2の昇圧回路部A1,A2は、基準電源電圧蓄積用の容量素子C1,C2に対して電荷蓄積動作を行ったのち、逆方向に基準電源電圧を印加して昇圧電圧蓄積用の容量素子に対してポンプ動作を行い、電荷蓄積動作の期間とポンプ動作の期間との間およびポンプ動作の期間と電荷蓄積動作の期間との間に基準電源との接続を断つデッドタイム期間を有する。制御部10は、両昇圧回路部の複数のスイッチ素子をオン・オフ制御し、両昇圧回路部のうちいずれか一方の昇圧回路部のデッドタイム期間において他方の昇圧回路部では電荷蓄積動作またはポンプ動作を行うという制御を、両昇圧回路部において交互かつサイクリックに行う。

(もっと読む)

電源回路

【課題】

整流用FETのスイッチング損失が小さく、かつ負荷電圧にかかわらず安定かつ確実に整流用FETを動作させることができる電源回路を提供すること。

【解決手段】

スイッチング半導体素子と、その制御回路と、トランスの2次巻線に接続される第1、第2の整流素子と、駆動回路とを備える電源回路において、前記第1の整流素子は少なくとも整流用FETとして働く電界効果トランジスタからなり、前記駆動回路は前記整流用FETを駆動するものであって、トランスの第3の巻線と、その第3の巻線に接続されている整流回路と、その出力側に接続されているインダクタとインピーダンス素子とからなり、前記インダクタに蓄えられたエネルギーが前記整流回路を通して放出されることによって、前記整流用FETのゲート容量の電荷が高速で放電されることを特徴とする電源回路。

(もっと読む)

多相コンバータ、ハイブリッド燃料電池システム、及び電源制御方法

【課題】システムの状態に応じて可能な限り通過電流量を大きくすることのできる多相コンバータを提供する。

【解決手段】電圧を変換する多相コンバータ(2)であって、独立して制御対象量(IL)を変更可能な複数の相(P1〜P3)と、各相の状態を検出する検出装置(Si)と、各相に対する制御対象量を規定する制御信号を供給する制御部(200)と、を備える。検出装置(Si)によって検出された各相の状態に基づいて、相ごとに制御対象量を補正する制御信号(MUP,MUN,GUN,GUP)が供給される。

(もっと読む)

スイッチング電源装置

【課題】リカバリー電流に起因する効率の低下を防止することの可能なスイッチング電源装置を提供する。

【解決手段】互いに並列に接続された電圧変換部1A,1Bと、これら電圧変換部1A,1Bの後段に接続された平滑コンデンサ3と、制御部4とを備える。電圧変換部1Aは、互いに同極性となるように共通のコア20に巻回された変圧インダクタ11A、ダイオード12Aおよび整流型スイッチング素子13Aからなり、電圧変換部1Bは、互いに同極性となるように共通のコア20に巻回された変圧インダクタ11B、ダイオード12Bおよび整流型スイッチング素子13Bからなる。制御部4は、各スイッチング素子13A,13Bを互いに異なる位相で順次動作させるようになっている。

(もっと読む)

スイッチング電源装置

【課題】リカバリー電流に起因する効率の低下を防止することの可能なスイッチング電源装置を提供する。

【解決手段】互いに並列に接続された電圧変換部1A,1Bと、これら電圧変換部1A,1Bの後段に接続された平滑コンデンサ3と、補助インダクタ20Aと、制御部4とを備える。電圧変換部1Aは変圧インダクタ11A、ダイオード12Aおよび整流型スイッチング素子13Aからなり、電圧変換部1Bは変圧インダクタ11B、ダイオード12Bおよび整流型スイッチング素子13Bからなる。補助インダクタ20Aは接続点J1と接続点J2との間に配置されている。制御部4は、各スイッチング素子13A,13Bを互いに異なる位相で順次動作させるようになっている。

(もっと読む)

チャージポンプ回路

【課題】基準電圧と異なる2つの電圧を出力するチャージポンプ回路の回路規模を小さくする。

【解決手段】第1の電圧Vout+を生成する第1のチャージポンプ回路部102と、第2の電圧Vout−を生成する第2のチャージポンプ回路部104と、第1のチャージポンプ回路部102と第2のチャージポンプ回路部104とに備えられるスイッチング素子30a〜30c,40a〜40cに接続され、スイッチング素子30a〜30c,40a〜40cを駆動する駆動パルスを供給するバッファ素子56a,56bを含む駆動パルス供給部108と、コンデンサ32a〜32c,42a〜42cを介して第1のチャージポンプ回路部102及び第2のチャージポンプ回路部104に接続され、コンデンサ32a〜32c,42a〜42cを充電するクロックパルスを生成する充電パルス供給部106と、を備えることにより上記課題を解決することができる。

(もっと読む)

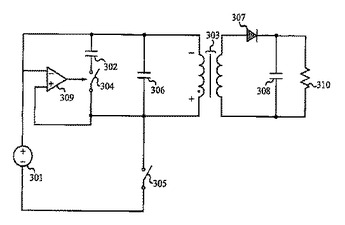

高電圧充電器

【課題】 容量性負荷のインバータ充電方式の高電圧充電器において、大きな充電速度を得ながら、充電後の電圧低下がなく、高い電圧安定度を得ることができ、かつノイズの発生も小さくできる高電圧充電器を提供する。

【解決手段】 高速充電を行う大出力の主インバータ4と、電圧調整を主目的とする小出力の補助インバータ7を並列接続し、充電期間の前半においては、主インバータと補助インバータを同時に運転して、容量性負荷を目標電圧の近傍まで高速充電し、ひきつづき、充電期間の後半では、主インバータ4を停止し、補助インバータ7のみで低速充電を行い、目標電圧に到達させ、その後、外部回路が放電動作を行うまでの期間は、目標電圧に保持するよう補助インバータ7の運転を持続させる。

(もっと読む)

スイッチング電源装置およびその制御回路、ならびにそれを用いた電子機器

【課題】軽負荷時におけるスイッチング電源装置の消費電流を低減する。

【解決手段】第1演算増幅器12および第1PWMコンパレータ14は、第1出力電圧Vout1に応じた電圧Vout1’と、第1基準電圧Vref1にもとづき、第1PWM信号Vpwm1を生成する。同様に、第2演算増幅器22および第2PWMコンパレータ24は、第2PWM信号Vpwm2を生成する。ロジック回路40は、第1、第2パルス幅変調信号Vpwm1、Vpwm2にもとづき、メインスイッチならびに2系統の同期整流スイッチを時分割してオンオフする。第1演算増幅器12、第2演算増幅器22は、軽負荷時においてコンパレータとして機能し、電圧Vout1’、Vout2’をそれぞれ基準電圧Vref1、Vref2と比較し、Vout1’>Vref1かつVout2’>Vref2のとき、オシレータ30、第1、第2PWMコンパレータ14、24の動作を停止する。

(もっと読む)

複数の結合インダクタを有する多相バックコンバータ

【課題】出力電流に低調波リップルを生じみくい多相コンバータを提供する。

【解決手段】多相コンバータは、2N+1個のインダクタと、並列接続されてそのそれぞれがスイッチノードを含む2N+1個のスイッチングコンバータとを備える。ここでNは偶数であり、上記インダクタの対が結合されて共通コアの周りに巻かれる。それぞれの結合インダクタが、その一方の極でそれぞれのスイッチノードに接続され、その他方の極で出力ノードに接続され、上記インダクタの少なくとも1つが他のインダクタとは非結合である。

(もっと読む)

電源装置

【課題】コンバータ回路の一部が故障しても性能を低下させずに動作を継続させる。

【解決手段】クロック信号生成手段、位置特定信号作成手段を設けたベースユニットに配置したコネクタに接続保持される各コンバータユニットは、コネクタへの接続を検出する接続検出手段22と、回路の動作異常を検出する異常検出手段19と、異常検出によりコンバータ回路を停止させるコンバータ停止手段20と、各コンバータユニットからベースユニットに出力した接続検出信号と各コンバータユニットからベースユニットに出力した異常検出信号により正常動作しているユニットの数と位置を特定する正常ユニット特定手段21と、クロック信号、位置特定信号、正常ユニット特定信号から、正常動作しているユニットの数をP、位置をQ番目としたとき、クロック信号の位相を基準に、(360/P)×(Q-1)度異なった位相信号をパルス幅変調制御手段に供給する位相信号生成手段23を設ける。

(もっと読む)

降圧型スイッチングレギュレータおよびその制御回路ならびにそれを用いた電子機器

【課題】 重負荷時のオン抵抗を抑えつつ、軽負荷時のゲートドライブ電流を低減する。

【解決手段】 ドライバ回路20は、スイッチングトランジスタM1および同期整流用トランジスタM2を相補的にオンオフする。スイッチングトランジスタM1および同期整流用トランジスタM2を、それぞれオンオフが独立に制御可能な2つのセグメントPMOS1、PMOS2、NMOS1、NMOS2に分割して形成する。負荷監視回路40は、降圧型スイッチングレギュレータ200の負荷状態を監視する。ドライバ回路20は、軽負荷状態となるに従い、スイッチングトランジスタM1および同期整流用トランジスタM2の駆動するセグメント数を減少させる。

(もっと読む)

フルブリッジ回路および大きな調整領域を有する電源装置

本発明は、少なくとも1つのトランス(TR1)と、該トランス(TR1)の1次巻線を入力側直流電圧(UE)に接続している少なくとも1つのフルブリッジ回路と、ブリッジ整流回路並びに出力側チョーク(L2)および出力側コンデンサ(C2)を介して出力回路に出力側直流電圧(UA)を供給している2次巻線と、ダイオード(D5)、コンデンサ(C4)および2次側のピーク電圧を低減するための抵抗(R1)から成っている負荷軽減回路とから成っており、その際別の2次巻線、別のブリッジ整流器回路および別の負荷軽減回路が設けられており、該別の負荷軽減回路を用いて出力側チョーク(L2)および出力側コンデンサ(C2)を介して出力側回路に出力側直流電圧(UA)の一部を供給するようになっている。これにより抵抗(R1,R2)において損失は低減されかつ効率は改善される。  (もっと読む)

(もっと読む)

電流共振型マルチフェーズDC/DCコンバータおよびその制御方法

【課題】 多相化に制限が無く、大容量化を可能とすること。

【解決手段】 並列接続されたM個の電流共振型マルチフェーズDC/DCコンバータ(10B−1〜10B−M)から出力されるM個のコンバータ出力電圧を出力コンデンサ(Co)で合成して、1つの出力電圧(Vout)を出力する電流共振型マルチフェーズDC/DCコンバータ(10C)において、M個の電流共振型マルチフェーズDC/DCコンバータ(10B−1〜10B−M)の各々は、並列接続されたN個の電流共振型DC/DCコンバータ(12D−11〜12−1N;…;12D−M1〜12D−MN)を備え、N個の電流共振型DC/DCコンバータはそれぞれN個の共振回路を含み、M個の電流共振型マルチフェーズDC/DCコンバータ(10B−1〜10B−M)の各々は、N個の共振回路の共振用インダクタ(Lr1;…;LrM)を共用している。

(もっと読む)

161 - 180 / 227

[ Back to top ]