Fターム[5H730FF06]の内容

DC−DCコンバータ (106,849) | 比較、演算部、信号伝達部 (4,636) | デジタル演算を行うもの (1,733)

Fターム[5H730FF06]の下位に属するFターム

カウンタのオーバーフローパルスを用いるもの (63)

レジスタ内容との比較によるもの (62)

マイコン、CPUの使用 (1,156)

Fターム[5H730FF06]に分類される特許

441 - 452 / 452

エネルギ節約型不連続モードシステム

【課題】 出力レギュレータの動作特性を改善して、出力レギュレータを使用する機械および装置をさらに小型化したり、より少ない電力で済むようにしたり、過渡状態中の精度と信頼性の向上を図ったり、あるいは動作の向上を図ったりすることなどにより、機械および装置の改善を可能にする。

【解決手段】 コントローラが出力レギュレータを制御し、出力レギュレータを制御する機能を提供するサブブロックを有する。コントローラは出力レギュレータの検知ポイントをモニタするエネルギ節約型不連続モード(ESDM)コントローラを備える。検知ポイントは出力レギュレータの出力電力の状態を示す。ESDMコントローラはサブブロックへの電力の流れを制御して、出力レギュレータの選択された電力状態の間、コントローラの消費電力を低減する。

(もっと読む)

ロバストディジタル制御器の設計装置

【課題】 近似度が高く、しかも制御入力の大きさを考慮する必要のないロバストディジタル制御器の設計装置を提供する。

【解決手段】 制御補償手段70Aは、目標値rと制御量yとの間の離散化した伝達関数Wry(z)を、より近似性の高い二次近似したモデル伝達関数Wm(z)に定め、このモデル伝達関数Wm(z)に基づいて、ディジタル制御器70の内部で演算処理できる積分形制御系として構築されている。また設計装置は、ここにあるパラメータを自動的に算出する。そのため、従来の一次近似モデルを実現する近似的なディジタル制御系に比べてより近似度が高く、出力ノイズに強いディジタル制御器70を実現できる。

(もっと読む)

デューティサイクル推定装置

【課題】出力レギュレータの動作特性を改善して、使用する機械および装置をさらに小型化したり、より少ない電力ですむようにする。

【解決手段】デューティサイクル推定装置が出力レギュレータの公称デューティサイクルを決定し、少なくとも2つのモードがモード1の推定装置とモード2の推定装置とを含む。モード1の推定装置は前回までのデューティサイクルに応じて公称デューティサイクルを決定する。モード2の推定装置は累積誤差に応じて公称デューティサイクルを決定する。モードセレクタは少なくとも2つのモードのうちの一方を選択し、モード選択基準に基づいて基準デューティサイクルを生成する。

(もっと読む)

出力レギュレータ

【課題】出力レギュレータの動作特性を改善して、過渡状態の精度向上や信頼性の向上を図ったり、装置の小型化、省電力を実現する。

【解決手段】入力電圧を調整済出力に変換する出力レギュレータが入力電圧から電力出力を生成する電力段を備える。出力フィルタが、電力出力をフィルタして調整済出力を生成する。出力センサが、少なくとも3つの基準範囲のどの範囲に調整済出力が含まれるかを示すデジタル検知信号を生成する。少なくとも3つの基準範囲の個々の範囲が調整済出力の複数の可能な値を含む。デジタルコントローラがデジタル検知信号に応動して、電力段を制御する駆動信号を生成する。

(もっと読む)

適応型デューティサイクルリミッタ

【課題】出力レギュレータの動作特性を改善して、過渡状態の精度改善や信頼性の向上を図ったり、装置の小型化、省電力を実現する。

【解決手段】デューティサイクルリミッタが、入力源と、出力レギュレータの調整済出力間のエネルギの移動に制限を設ける。出力レギュレータは、レギュレータ特性と、入力源と調整済出力間のエネルギの移動を制御する計算済みデューティサイクルを有する。デューティサイクルリミッタは、デジタルコントローラを備え、基準レベルを生成し、出力レギュレータのレギュレータ特性を基準レベルと比較して、最大デューティサイクルを決定する。デジタルコントローラは出力レギュレータのスイッチング周波数に少なくとも等しい周波数で基準レベルを制御する。デジタルコントローラは計算済みデューティサイクルを最大デューティサイクルに制限する。

(もっと読む)

電圧変換装置、電圧変換方法、および、電子機器

【課題】 出力電圧が所定の電圧より高くなった場合でも、所定の電圧まで降下させる制御が可能な電圧変換装置を提供すること。

【解決手段】 入力電圧をスイッチングする第1のスイッチング手段(NチャネルFET13)と、第1のスイッチング手段の出力側に接続された出力電圧を誘起するインダクタンス素子(インダクタンス素子17)と、第1のスイッチング手段の出力側と、グランドとに接続された第2のスイッチング手段(NチャネルFET31)と、出力電圧に基づいて第1のスイッチング手段のスイッチング動作を制御する第1の制御手段(制御回路30)と、出力電圧に応じて第2のスイッチング手段をスイッチングさせる第2の制御手段(制御回路30)と、を有する。

(もっと読む)

半導体集積回路装置

本発明は、負荷を検出し、その負荷の大きさに最適な電流供給能力に制御される正または負の高電圧を、電流供給能力に応じた消費電力で発生する半導体集積回路装置を提供する。正または負の高電圧を生成するチャージポンプと、チャージポンプを駆動するパルス信号を生成する発振器と、発振器の電源電圧を制御する電圧制御回路と、チャージポンプの負荷の大きさを検出する負荷検出回路と、チャージポンプの出力電圧を検出する電圧センサとを備える。  (もっと読む)

(もっと読む)

容量性負荷を充電するための回路および技術

【課題】 コンデンサの負荷電圧が広い範囲にわたる容量性負荷に電力を送達する電力スイッチングのトポロジーを提供する。

【解決手段】コンデンサ充電回路を用いて出力コンデンサを所定の出力電圧レベルまで充電する方法は、出力コンデンサに電力を送達する工程と、出力電圧レベルが所定の出力電圧レベル以上である場合、出力コンデンサへの電力送達および出力電圧測定を終了する工程と、終了から時間間隔をおいて電力送達を再開する工程と、電力送達の再開に基づいて出力電圧レベルを決定する工程であって、電圧レベルを測定した回路を一時的に駆動させる工程をさらに包含する。

(もっと読む)

開回路電圧調整を備える電子バラスト

開回路電圧調整を有する電子バラストは、該電子バラストの出力へ動作可能な状態で接続され、検知出力電圧信号を発生させるフィラメント電流検知回路224と、前記検知出力電圧信号を受信し、当該電子バラストの出力での電圧を制御するよう動作可能な状態で接続された調整パルス幅変調器U3とを有する。調整パルス幅変調器U3は、出力電圧閾値限界を有する。調整パルス幅変調器U3は、検知出力電圧信号が出力電圧閾値限界を超える場合に、電子バラストの出力での電圧を制限する。調整パルス幅変調器U3は、高電圧ドライバ及び共振ハーフブリッジへのパルス幅を制限することによって、出力電圧を制限することができる。フィラメント電流検知回路224は、例えばタンク電流を検知することによって、間接的に出力電圧を検知することができ、あるいは、出力電圧を直接的に検知することもできる。  (もっと読む)

(もっと読む)

PFC−PWM電力変換器の消費電力を低減する装置

【課題】PFC−PWM電力変換器の消費電力を低減する装置を開示する。

【解決手段】装置はライン入力電圧を検出し、PFC信号とPWM信号を制御するために用いられる制御端子を有する。さらに、装置は、PFC電力管理部とPWM電力管理部を有する。PFC制御部のPFC電力管理部は、PFC制御部のエラー増幅器用のPFC基準電圧を決定する。PFC基準電圧は、制御端子における電圧に応じて生成する。制御端子における電圧が低電圧閾値電圧より低下すると常に、PFC電力管理部はPFC信号を無効にする。制御端子における電圧がプログラム可能な閾値電圧より低下すると常に、PWM電力管理部はPWM信号を無効にする。その上、PWM電力管理部は軽負荷および無負荷条件中、制御端子における電圧を引き下げPFC回路を無効にする。

(もっと読む)

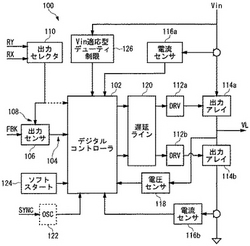

全体的フィードフォワードスイッチング電源制御

【課題】

【解決手段】開示された電源は、制御信号によって制御可能でありDC入力電圧から所望の出力を供給するスイッチング式変換器と、スイッチング式変換器のスイッチのゲート駆動電圧,温度測定値などをアナログ入力として受信し、アナログ入力をデジタル入力信号に変換するアナログデジタル変換器と、デジタル入力信号を受信して、スイッチを駆動する制御信号を生成するデジタルプロセッサと、デジタル入力信号をスイッチング式変換器の所望の出力に関連付けるデータを記憶して、制御信号の生成に用いるメモリ出力信号をデジタルプロセッサに提供するメモリとを備える。

(もっと読む)

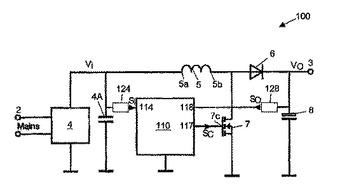

デジタル信号プロセッサを備えたパワーコンバータ

アップコンバータ(100)は、出力(3)と直列に接続されたインダクタ(5)及びダイオード(6)と、前記出力と並列に接続されたコンデンサ(8)と、前記インダクタと前記ダイオードとの間のノードに結合された1つのスイッチ端子を持つ制御可能スイッチ(7)とを有する。制御方法は、−インダクタに整流化された交流電圧(Vi)を供給するステップと、−スイッチをスイッチ開閉するために、パルス幅(TH)を持つスイッチ制御信号(SC)を発生させるステップと、を有し、スイッチ制御信号は、出力(3)における出力電圧(VO)に基づいて発生させられる。本発明によれば、アップコンバータは、デジタルプロセッサ(110)を有し、該デジタルプロセッサ(110)は、出力電圧(VO)をサンプリングし、出力電圧(VO)が略一定に留まるようにスイッチ制御信号(SC)のパルス幅(TH)を計算するように、サンプリングされた出力電圧(VO)をデジタル的に処理する。  (もっと読む)

(もっと読む)

441 - 452 / 452

[ Back to top ]