Fターム[5J034AB11]の内容

半導体素子を用いたパルス発生器 (1,143) | 目的、効果 (486) | 他の回路機能を共用 (13)

Fターム[5J034AB11]に分類される特許

1 - 13 / 13

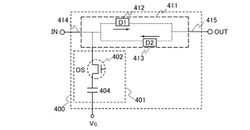

半導体装置

【課題】新規な構成を有する半導体装置である。

【解決手段】第1の素子を有し、第2の素子を有し、トランジスタを有し、容量を有し、第1の素子の出力は、第2の素子の入力と電気的に接続され、第2の素子の出力は、第1の素子の入力と電気的に接続され、第1の素子の入力は、入力端子と電気的に接続され、第1の素子の出力は、出力端子と電気的に接続され、トランジスタのソース及びドレインの一方は、容量の一方の電極と電気的に接続され、トランジスタのソース及びドレインの他方は、入力端子と電気的に接続され、トランジスタのチャネル形成領域は、結晶を有する酸化物半導体を有する。結晶を有する酸化物半導体を有するトランジスタはリーク電流が非常に小さいため、データを保持することができる。

(もっと読む)

デュアルパスマルチモード順次記憶素子

【課題】デュアルパスマルチモード順次記憶素子

【解決手段】本明細書では、デュアルパスマルチモード順次記憶素子(SSE)(10)が説明されている。一実施例では、デュアルパスマルチモードSSEは、第1(14)および第2(12)の順次記憶素子、データ入力、データ出力ならびに選択機構(16)を備えている。第1および第2の順次記憶素子(14、12)は、それぞれ、入力および出力を有する。データ入力は両方の順次記憶素子の入力に結合され、データを受け入れるように構成される。データ出力は両方の順次記憶素子の出力に結合され、データを出力するように構成される。選択機構(16)は、データ入力からのデータをデータ出力に渡すために、順次記憶素子のうちの1つを選択するように構成される。一実施例では、第1の順次記憶素子はパルストリガー式記憶素子(14)を備えており、第2の順次記憶素子はマスタースレーブ記憶素子(12)を備えている。

(もっと読む)

高速量子化器

【課題】高速量子化器および最適化された時間遅延を提供する。

【解決手段】高速量子化器コンパレータの装置と方法は、3部を含む:プリアンプ部、再生ラッチ部、およびデータラッチ部。時間遅延は、再生ラッチ出力の最初の電圧を変えることによって減少される。電流源はコンパレータの底部に提供され、時間遅延最適化を可能にする。PMOS同等化スイッチが停止されたとき、クロック信号をフィードスルーにし、出力に電荷の注入を提供する。これらの電荷によって、コンパレータの時間遅延が可変となる。リセット時間が比較時間より長いために、非常に低い電流が出力電圧を決定する。

(もっと読む)

データ保持装置

【課題】通常動作時の速度低下や消費電力の増大を招くことなく、電源遮断後もデータを不揮発的に保持することが可能であり、かつ、信頼性や利便性の高いデータ保持装置を提供する。

【解決手段】データ保持装置は、ループ状に接続された複数の論理ゲートNAND3、NAND4を用いてデータを保持するループ構造部LOOPと、強誘電体素子のヒステリシス特性を用いてループ構造部LOOPに保持されたデータを不揮発的に記憶する不揮発性記憶部NVMと、ループ構造部LOOPと不揮発性記憶部NVMとを電気的に分離する回路分離部SEPと、複数の論理ゲートは、それぞれ、所定のセット信号SNL及びリセット信号RNLに応じて、任意の出力論理レベルにセット/リセットされるものであり、不揮発性記憶部NVMに記憶されたデータに基づいて、セット信号SNL及びリセット信号RNLを生成するセット/リセット制御部SRCを有する。

(もっと読む)

SRフリップフロップならびにそれを用いたレベルシフタおよび試験装置

【課題】レベルシフト機能を有するSRフリップフロップを提供する。

【解決手段】クロスカップルインバータ30は、互いに入力端子と出力端子とがクロスカップリングされた第1インバータ32および第2インバータ34を含む。第1セットトランジスタms1のゲートにセット信号Sが入力され、第4セットトランジスタms4のゲートに、反転セット信号SXが入力される。リセット部20の第1リセットトランジスタmr1のゲートにリセット信号Rが入力され、第4リセットトランジスタmr4のゲートに、反転リセット信号RXが入力される。第2セットトランジスタms2のゲートおよび第3リセットトランジスタmr3のゲートは、第2インバータ34の出力端子と接続される。第3セットトランジスタms3のゲートおよび第2リセットトランジスタmr2のゲートは、第1インバータ32の出力端子と接続される。

(もっと読む)

電圧比較回路および半導体装置

【課題】消費電力の増大や応答速度の低下をきたすことなく、閾値のばらつきを抑えて確実な動作を可能とする電圧比較回路の提供を図る。

【解決手段】複数のトランジスタM1,M2,M11,M12,M21,M22を有する電圧比較回路であって、該複数のトランジスタの少なくとも1つの第1トランジスタM1(M2)は、制御端子と、該制御端子に供給される信号の電圧Vi+(Vi-)により接続が制御される第1および第2端子と、第1スイッチS2p(S2m)を介して所定の電位線PL2に接続されると共に、第1容量C1(C2)の一端が接続されたボディと、を有するように構成する。

(もっと読む)

半導体集積回路

【課題】データ選択機能付きのダイナミック型フリップフロップ回路において、動作の高速性を良好に確保しながら、複数のデータの何れもが選択されていない場合であっても、正常動作するようにする。

【解決手段】例えば選択信号S0によりHのデータD0が選択されていた場合、第1ノードN1がLとなり、第2ダイナミック回路1Bの第2ノードN2はHとなっており、出力信号QはHレベルである。この状態において、選択信号S0〜S2によって複数のデータD0〜D2の何れもが選択されなくなった際には、第1ノードN1がHとなり、前記第2ノードN2は、その電荷が放電されて、出力信号QはLレベルに誤動作する状況となる。しかし、この場合には、出力ノードN3がHとなり、第4ノードN4がLとなって、前記第2ダイナミック回路1Bのn型トランジスタTr6がオフして、第2ノードN2の放電を阻止する。

(もっと読む)

スキャン用フリップフロップ回路

【課題】スキャン用フリップフロップ回路におけるマスタラッチ部へのデータ取込みに要する時間を短縮する。

【解決手段】スキャン用フリップフロップ回路(100)は、データ信号又はスキャンイン信号をクロック信号に同期して保持可能なマスタラッチ(13)と、上記マスタラッチの出力信号を上記クロック信号に同期して保持可能なスレーブラッチ(15)とを含む。上記マスタラッチは、上記データ信号を取込むための第1取込み部(13A)と、上記スキャンイン信号を取込むための第2取込み部(13B)と、上記第1取込み部を介して取込まれた上記データ信号、又は上記第2取込み部を介して取込まれた上記スキャンイン信号を上記クロック信号に同期して保持可能なラッチ部(13C)とに分割して配置する。これによりマスタラッチの前段へのセレクタの配置を不要とし、マスタラッチ部へのデータ取込みに要する時間の短縮を図る。

(もっと読む)

半導体メモリ素子及びその駆動方法

【課題】データラインにターミネーションスキーム(termination scheme)を使用する半導体メモリ素子及びその駆動方法を提供すること。

【解決手段】本発明の半導体メモリ素子は、コア領域とインターフェス領域との間にデータを伝達するためのグローバルデータラインと、ターミネーションイネーブル信号に応答して、予定されたターミネーション電圧レベルで前記グローバルデータラインを駆動するメイン駆動手段と、前記ターミネーションイネーブル信号のアクティブ区間の初期に一定時間の間アクティブになるオーバードライビング信号に応答して、前記グローバルデータラインを予定されたターミネーション電圧レベルで駆動する補助駆動手段とを備える。

(もっと読む)

スキャンフリップフロップ回路、及び、半導体集積回路装置

【課題】遅延故障試験時に遅延故障試験用の2パタンを印加可能とするスキャンフリップフロップを提供することを目的とする。

【解決手段】スキャンフリップフロップ回路は、ラッチ部(1、2、3、4、5、6、7、)と、ホールド部(8、9)と、第1出力ノード(N01)と、第2出力ノード(N02)とを具備する。ラッチ部(1、2、3、4、5、6、7、)は、データを保持する。ホールド部(8、9)は、制御信号(H)に基づいて内部状態を取り込んで出力状態を保持する。第1出力ノード(N01)は、出力状態に基づいて第1出力信号(Q)を出力する。第2出力ノード(N02)は、内部状態に基づいて第2出力信号(SOT)を出力する。

(もっと読む)

データラッチ回路およびそれを用いた液晶表示装置

【課題】 大容量の負荷を安定して駆動することができるデータラッチ回路およびそれを用いた液晶表示装置を実現する。

【解決手段】 本発明のデータラッチ回路およびそれを用いた液晶表示装置は、第1および第2の信号レベルの間を交互に周期的に遷移する第1のクロック信号CKと、CKと略相補的な第2のクロック信号BCKと、CK/BCKの信号レベルに基づいて、入力されるデータ信号INの取り込みと保持および出力を行うデータラッチ23と、CKおよびBCKが同時に第1または第2の信号レベルにある期間は、INの取り込みを行わないようデータラッチ23を制御する制御回路24を有する。

(もっと読む)

汎用論理モジュール及びそれを有する回路

【課題】プログラマブルかつ最適制御可能な汎用論理モジュール及びそれを有する回路を提供する。

【解決手段】集積回路29は、汎用論理モジュール25と、結合部26と、計算部28とを具える。汎用論理モジュール25は、二つの入出力制御部23と、記憶部24とを有し、設定及び制御情報が入力される。入出力制御部23は、入出力端子21に入力される情報及び入出力端子22に入力される入出力制御情報の組合せ論理演算を行う。記憶部24は、組合せ論理演算の結果を記憶し、その結果の肯定又は否定を出力する。記憶部24は、第1反転増幅器及びそれに交差結合した第2反転増幅器と、強誘電体又は強磁性体の記憶素子とを有する。

(もっと読む)

分周回路

【課題】 動作速度を高めることができる分周回路を提供する。

【解決手段】 マスター回路10は、クロックCK+に応答して分周回路の出力を取り込む差動増幅回路10aと、クロック周期の間差動増幅回路の出力を保持するラッチ回路10bとから成る。スレーブ回路20はクロックCK-に応答してマスター回路の出力を取り込む差動増幅回路20aと、相補的なクロック周期の間差動増幅回路20aの出力を保持するラッチ回路20bとから成り、クロックを分周した信号を出力する。差動増幅回路の定電流源1と別個にラッチ回路に対する定電流源2,3を設ける。差動増幅回路の差動対トランジスタは各クロックに応答して定電流源に接続される。ラッチ回路の差動対トランジスタは別個の定電流源に直結されている。

(もっと読む)

1 - 13 / 13

[ Back to top ]