Fターム[5J034DB00]の内容

半導体素子を用いたパルス発生器 (1,143) | 回路形式 (339)

Fターム[5J034DB00]の下位に属するFターム

Fターム[5J034DB00]に分類される特許

1 - 10 / 10

記憶素子および信号処理回路

【課題】消費電力を抑えることができる記憶素子、当該記憶素子を用いた信号処理回路を提供する。

【解決手段】一対のインバータ(クロックドインバータを含む)を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積および放出を制御するスイッチング素子とを設ける。例えば、容量素子の一方の電極を一対のインバータのいずれかの入力あるいは出力である第1のノードに接続し、他方の電極をスイッチング素子の一方の電極に接続する。スイッチング素子の他方の電極は前記インバータの出力あるいは入力である第2のノードに接続する。ここで、第1のノードの電位と第2のノードの電位は互いに逆の位相である。このような接続により、データ回復時における第1のノードと第2のノードの電位差の絶対値を十分に大きくすることができ、データ回復時のエラーを減らせる。

(もっと読む)

半導体装置、表示モジュール、及び電子機器

【課題】開示する発明の一態様は、安定して動作することが可能なパルス信号出力回路及

びそれを含むシフトレジスタを提供することを課題の一とする。

【解決手段】開示する発明の一態様のパルス信号出力回路は、第1乃至第10のトランジ

スタを有し、第1のトランジスタおよび第3のトランジスタのチャネル長Lに対するチャ

ネル幅Wの比W/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタ

のW/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタのW/Lは

、第7のトランジスタのW/Lと等しく、第3のトランジスタのW/Lは、第4のトラン

ジスタのW/Lよりも大きくする。これによって、安定して動作することが可能なパルス

信号出力回路及びそれを含むシフトレジスタを提供することができる。

(もっと読む)

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

半導体装置

【課題】電源をオフしてもデータを保持することができ、退避動作と復帰動作が不要なレジスタ回路を提供する。

【解決手段】複数のレジスタ構成回路と、オフ電流が小さい第1のトランジスタと、オフ電流が小さい第2のトランジスタと、を有するレジスタ回路において、データ保持部を前記第1のトランジスタのソース及びドレインの一方に接続し、前記第2のトランジスタのソース及びドレインの一方に接続する。前記第1のトランジスタ及び前記第2のトランジスタはオフ電流が小さいので、データ保持部の電荷がリークせず、レジスタ回路の電源をオフしてもデータ保持部にデータが保持される。そのため、退避動作と復帰動作を行わなくてよい。

(もっと読む)

半導体集積回路装置

【課題】従来に比べて高速に動作する半導体集積回路装置を提供する。

【解決手段】実施形態の半導体集積回路装置は、遷移期間に出力ノードのレベルを遷移可能にし、遷移期間以外の期間に出力ノードのレベルを保持させるフリップフロップであって、プリチャージノードの充放電を行う第1の充電部及び放電部と、出力ノードの充放電を行ってプリチャージノードの状態に応じた正相出力又は反転出力を出力ノードに出力させる第2の充電部及び放電部と、を有し、入力信号に基づいて出力ノードの正相出力又は反転出力の状態を決定するフリップフロップを備えた半導体集積回路装置であって、第1の放電部の経路途中のノードを遷移期間の前の期間に放電させるよう構成された制御部を具備し、フリップフロップは、遷移期間以外の期間に出力ノードのレベルを保持させる状態保持回路と、遷移期間に、状態保持回路の保持動作を停止させる保持動作停止部とを有する。

(もっと読む)

半導体回路

【課題】スイッチングノイズを低減できるようにすると共に出力波形の立ち上がり時間を短縮できるようにする。

【解決手段】フリップフロップ回路100は、CML回路3aにおけるMOSトランジスタM9のドレイン側と、このCML回路3aと逆位相で動作するCML回路3cにおけるMOSトランジスタM11のドレイン側とが、充放電動作を行う容量素子C1addを介在させて接続されている。この構成によって、容量素子C1addは、電流経路切り替え時に発生するMOSトランジスタM9の放電電流ICaをON状態のMOSトランジスタM11に電流I1caddとして流すことができる。これにより、逆流する放電電流ICaにより消費される電流を低減できるので、スイッチングノイズを低減できると共に波形の立ち上がりの遅延を防止できる。

(もっと読む)

不揮発ラッチ回路および不揮発性フリップフロップ回路

【課題】微細化してもスケーラビリティーに優れ、膨大な書き換え耐性が不要となることを可能にする。

【解決手段】入力信号の取り込みまたは遮断を制御する第1ゲート部と、第1入力端子および第1制御信号を受ける第2入力端子を有し、第1制御信号に応じてインバータかまたは一定電圧を出力するゲートとして動作する第1論理ゲートと、第1論理ゲートの出力を受ける第1入力端子および第1制御信号を受ける第2入力端子を有し、第1制御信号に応じてインバータかまたは一定電圧を出力するゲートとして動作する第2論理ゲートと、第2論理ゲートの出力を第1論理ゲートの第1入力端子に送出する第2ゲート部と、電流の流れる方向によって抵抗が変化する第1および第2抵抗素子と、第1および第2データ書き込み信号線と、第2論理回路の出力を第1出力ノードと、第1論理回路の出力の反転信号として出力する第2出力ノードと、を備えている。

(もっと読む)

直交3分割分周器および低電圧マラーC素子

多数の入力を有する広帯域低電圧、低電力差動マラーC素子を使用する低電圧、低電力、広帯域直交3分割分周器は直交入力および直交出力信号で作動する。この分周器は周波数シンセサイザ内で使用することができ、かつ直交局部発振器発生器として使用することができる。  (もっと読む)

(もっと読む)

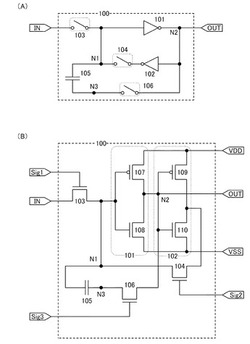

パルス出力回路、シフトレジスタ、および表示装置

【課題】 一導電型のTFTによって構成し、かつ出力信号振幅を正常に得られる回路を提供する。

【解決手段】 TFT101、103は、CK1にHレベルが入力されてONし、信号出力部(Out)の電位がLレベルに確定される。次に、信号入力部(In)にパルスが入力されてHレベルとなり、TFT102のゲート電位は(VDD−VthN)まで上昇し、浮遊状態となる。これによりTFT102がONする。次にCK1がLレベルとなり、TFT101、103がOFFする。同時にCK3がHレベルとなって信号出力部の電位は上昇し、同時に容量104の働きによってTFT102のゲートの電位が(VDD+VthN)以上に上昇することによって信号出力部(Out)に現れるHレベルはVDDに等しくなる。SPがLo、CK3がLo、CK1がHレベルになると、信号出力部(Out)の電位は再びLレベルとなる。

(もっと読む)

フリップフロップ回路

【課題】 フリップフロップ回路の入出力端子の入力容量や駆動力が一定に保たれるようにする。

【解決手段】 フリップフロップ回路は、マスターラッチ部101と、スレーブラッチ部102と、データ出力選択部107とを有する。マスターラッチ部101は、トライステートインバータ111を含み、データ入力端子105は上記トライステートインバータ111に接続される。データ出力選択部107は、パスゲート117、パスゲート118、インバータ119によって構成され、上記インバータ119がデータ出力端子106に接続される。フリップフロップ回路の入力容量は、データ入力端子105が接続されるトライステートインバータ111のトランジスタのゲート容量によって定まり、駆動能力は、インバータ119の駆動能力によって定まるので、クロック信号などのタイミング信号の状態によって変化しない。

(もっと読む)

1 - 10 / 10

[ Back to top ]