Fターム[5J034DB08]の内容

半導体素子を用いたパルス発生器 (1,143) | 回路形式 (339) | ラッチ回路 (170)

Fターム[5J034DB08]に分類される特許

1 - 20 / 170

ラッチ回路および表示装置

【課題】ドレインアバランシェ効果を抑圧し、信頼性を向上させることが可能となるラッチ回路を提供する。

【解決手段】ゲートに前記走査電圧が入力されたときに、「0」あるいは「1」のデータに対応する電圧を取り込む入力トランジスタと、他端に容量制御信号が入力されるとともに、一端が前記入力トランジスタの第2電極に接続され、前記入力トランジスタで取り込まれた電圧を保持する保持容量と、ゲートが前記入力トランジスタの第2電極に接続され、第2電極が第1出力端子に接続されるとともに、第1電極に第1ラッチ制御信号が入力される第1導電型の第1トランジスタと、ゲートが前記第1トランジスタの第2電極に接続され、第2電極が第2出力端子に接続されるとともに、第1電極に第2ラッチ制御信号が入力される第2導電型の第2トランジスタとを備える。

(もっと読む)

ラッチ回路

【課題】回路面積が小さく、かつ省電力化したラッチ回路を提供する。

【解決手段】複数の論理回路(第1の論理回路11、第2の論理回路13、第3の論理回路15、及び第4の論理回路17)によりラッチ回路1を構成し、選択信号の論理レベルに応じて差動動作とシングルエンド動作の切り替えを行う。また、これらの複数の論理回路11,13,15,17へのクロック入力信号に応じて個々の論理回路をON状態又はOFF状態にすることで、差動動作とシングルエンド動作それぞれにおいてスルー動作とホールド動作をさせる。

(もっと読む)

半導体装置

【課題】トランジスタのしきい値電圧の変動を抑制し、表示パネルに実装するドライバI

Cの接点数を削減し、表示装置の低消費電力化を達成し、表示装置の大型化又は高精細化

を達成することを目的とする。

【解決手段】劣化しやすいトランジスタのゲート電極を、第1のスイッチングトランジス

タを介して高電位が供給される配線、及び第2のスイッチングトランジスタを介して低電

位が供給される配線に接続し、第1のスイッチングトランジスタのゲート電極にクロック

信号を入力し、第2のスイッチングトランジスタのゲート電極に反転クロック信号を入力

することで、劣化しやすいトランジスタのゲート電極に高電位、又は低電位を交互に供給

する。

(もっと読む)

フリップフロップ回路

【課題】セレクタ付フリップフロップ回路の入力信号がラッチ回路へと伝播するまでに、選択信号により制御されるスイッチ回路とクロック信号により制御されるスイッチ回路とを介するため、入力信号がラッチへと伝播するまでの時間が長い。

【解決手段】セレクタ付フリップフロップ回路100は、選択信号SA、クロック信号CKおよび複数の入力データが入力され、複数の入力データのうち1つを出力するフリップフロップ回路であって、選択信号SAおよびクロック信号CKに基づいて、第1の制御信号CAを生成する第1の論理回路102と、第1の制御信号CAにより制御される第1のスイッチ回路101と、第1のスイッチ回路101を介して、複数の入力データから選択された一の入力データを保持する第1のラッチ回路103とを有する。

(もっと読む)

半導体装置

【課題】新規な不揮発性のラッチ回路及びそれを用いた半導体装置を提供する。

【解決手段】第1の素子の出力は第2の素子の入力に電気的に接続され、第2の素子の出

力は第2のトランジスタを介して第1の素子の入力に電気的に接続されるループ構造を有

するラッチ回路であって、チャネル形成領域を構成する半導体材料として酸化物半導体を

用いたトランジスタをスイッチング素子として用い、またこのトランジスタのソース電極

又はドレイン電極に電気的に接続された容量を有することで、ラッチ回路のデータを保持

することができる。これにより不揮発性のラッチ回路を構成することができる。

(もっと読む)

不揮発性のラッチ回路

【課題】新規な不揮発性のラッチ回路及びそれを用いた半導体装置を提供する。

【解決手段】第1の素子の出力が第2の素子の入力に電気的に接続され、第2の素子の出力が第1の素子の入力に電気的に接続されるループ構造を有するラッチ部と、ラッチ部のデータを保持するデータ保持部とを有し、このラッチ部とデータ保持部とにより不揮発性のラッチ回路が構成される。データ保持部は、チャネル形成領域を構成する半導体材料として酸化物半導体を用いたトランジスタをスイッチング素子として用いている。またこのトランジスタのソース電極又はドレイン電極に電気的に接続されたインバータを有している。上記トランジスタを用いて、ラッチ部に保持されているデータをインバータのゲート容量あるいは別に用意した容量に書き込むことができる。

(もっと読む)

ラッチ回路、分周回路、フリップフロップ回路、PLL回路、マルチプレクサ及び半導体集積回路

【課題】CMLレベルのデータを出力するラッチ回路を使用した分周回路の出力をCMOSレベルで扱うためにはレベル変換が必要となる。そのため、CMLレベルのクロックを受け付け、CMOSレベルのデータを出力することで、回路規模及び消費電力の抑制を実現するラッチ回路が望まれる。

【解決手段】ラッチ回路では、差動入力データを受け付けるNチャンネル型MOSトランジスタのドレイン端子とPチャンネル型MOSトランジスタのゲート端子にクロスして接続している。このようにして、CMLレベルのデータをCMOSレベルのデータに変換する。

(もっと読む)

記憶素子、記憶装置、信号処理回路

【課題】消費電力を抑えることができる信号処理回路を提供する。

【解決手段】記憶素子に電源電圧が供給されない間は、揮発性のメモリに相当する第1の記憶回路に記憶されていたデータを、第2の記憶回路に設けられた第1の容量素子によって保持する。酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、第1の容量素子に保持された信号は長期間にわたり保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。また、第1の容量素子によって保持された信号を、第2のトランジスタの状態(オン状態、またはオフ状態)に変換して、第2の記憶回路から読み出すため、元の信号を正確に読み出すことが可能である。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】信号処理回路は、メモリと、メモリを制御する制御部と、を有し、制御部は、データラッチ端子を有する揮発性の記憶回路と、データラッチ端子の一方に電気的に接続された第1の不揮発性の記憶回路と、データラッチ端子の他方に電気的に接続された第2の不揮発性の記憶回路と、データラッチ端子の一方及びデータラッチ端子の他方に、高電源電位の半分の電位を供給する機能を有するプリチャージ回路と、を有し、第1の不揮発性の記憶回路及び第2の不揮発性の記憶回路のそれぞれは、酸化物半導体を有するチャネル形成領域を有するトランジスタと、トランジスタがオフ状態となることによってフローティングとなるノードに接続された容量素子と、を有する。

(もっと読む)

半導体装置

【課題】所望のタイミングでデータの評価、書き換えを行うことができる半導体装置を提供する。

【解決手段】フリップフロップ回路と、選択回路と、選択回路を介して前記フリップフロップ回路と電気的に接続する不揮発性記憶回路と、を含むレジスタ回路と、ビット線と、データ線と、を有し、データ線はフリップフロップ回路と電気的に接続し、ビット線は、選択回路を介して不揮発性記憶回路と電気的に接続し、選択回路は、データ線の電位またはビット線の電位に応じたデータを選択的に不揮発性記憶回路に格納する半導体装置。

(もっと読む)

ラッチ回路及び半導体装置

【課題】新規のラッチ回路を提供すること。

【解決手段】ラッチ回路は、酸化物半導体(OS)によってチャネル領域が形成されるトランジスタ10を有し、出力端子(Q端子)並びにトランジスタ10のソース及びドレインの一方に電気的に接続され、且つトランジスタ10がオフ状態となることによって浮遊状態となるノード11においてデータを保持する。なお、当該酸化物半導体は、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い。このような酸化物半導体によってトランジスタのチャネル領域が形成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。

(もっと読む)

記憶装置

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置を提供する。

【解決手段】揮発性の第1の記憶回路と、酸化物半導体層にチャネルが形成されるトランジスタを有する不揮発性の第2の記憶回路と、を有し、高周波数で駆動する場合、電源電圧が供給されている期間では、第1の記憶回路にデータ信号を書き込み及び当該データ信号を出力し、電源電圧の供給が停止する前の期間である、電源電圧が供給されている期間の一部では、第2の記憶回路にデータ信号を書き込み、低周波数で駆動する場合、電源電圧が供給されている期間では、第2の記憶回路にデータ信号を書き込み、第2の記憶回路に書き込まれたデータ信号を第1の記憶回路に書き込み、第1の記憶回路に書き込まれたデータ信号を出力する記憶装置に関する。

(もっと読む)

データ処理装置

【課題】電源の遮断時/起動時におけるレジスタデータの退避/復帰を簡易な構成で実現し、通常時のパフォーマンスが低下しないデータ処理装置を提供する。

【解決手段】CPU101、揮発性RAM102、不揮発性FeRAM103、ROM104、CPU101のアクセス対象を選択する選択器105を有する。選択器105は、通常動作時においてはRAM102を選択し、データ処理装置100の電源遮断処理が開始され、且つHALT可能な状態に移行した段階で、FeRAM103を選択する。これにより、電源遮断時において、CPU101が保持しているレジスタ111のデータをFeRAM103に記録できるようにする。また選択器105は、データ処理装置100の電源起動処理が開始され、且つFeRAM103に記録されているレジスタデータをCPU101が読み出してレジスタ111に格納した段階で、RAM102を選択する。

(もっと読む)

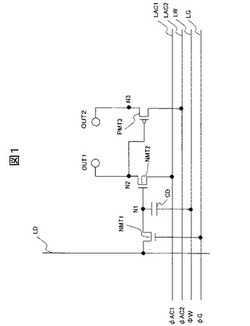

ラッチ回路およびラッチ回路を用いた表示装置

【課題】比較的短い時間間隔で、ラッチ情報をラッチすることが可能で、より低コスト化を図ることが可能となる単チャンネルラッチ回路を提供する。

【解決手段】入力トランジスタと、前記入力トランジスタの第2電極と第1ラッチ制御線との間に接続される保持容量と、第1電極が前記第1ラッチ制御線に接続され、ゲートが前記入力トランジスタの第2電極に接続される第1トランジスタと、ゲートが前記第1トランジスタの第2電極に接続され、第1電極が第2ラッチ制御線に接続される第2トランジスタと、ゲートが前記第1トランジスタの第2電極に接続され、第1電極が前記第2トランジスタの第2電極に接続されると共に、第2電極が出力端子に接続される第3トランジスタと、前記第1トランジスタの第2電極と前記第2トランジスタの第2電極との間に接続される容量と、前記第1トランジスタの第2電極と前記第1ラッチ制御線との間に接続されるダイオードとを有する。

(もっと読む)

ディレイラッチ回路、および、ディレイフリップフロップ

【課題】Dラッチ回路またはDフリップフロップの消費電力の増大を抑制しつつ、低電圧におけるDラッチ回路またはDフリップフロップの誤動作を防止する。

【解決手段】内部信号出力回路320は、内部透過開始タイミングから内部透過終了タイミングまでの間においてはデータ信号を反転した信号を内部信号として出力する。内部信号出力回路320は、内部透過終了タイミングから内部透過開始タイミングまでの間においては所定値に値を固定した信号を内部信号として出力する。nMOSトランジスタ330は、保持指示遅延タイミングからデータの透過が指示されるまでの間に内部透過終了タイミングが含まれるように前記出力された内部信号を遅延させる。

(もっと読む)

ラッチ回路、CDR回路、および受信装置

【課題】 消費電力を抑えた受信回路を提供する。

【解決手段】 本発明では、差動信号を差動増幅させる際に、差動入力によって発生する電流を対となる差動出力により遮断することで差動信号をラッチする回路を提供する。該ラッチ回路の適用により、受信信号の差動信号電圧差が小さい場合でも伝送データを受信できる為、増幅用アンプの削減が可能となり、受信装置の消費電力の低減を図ることができる。

(もっと読む)

不揮発性ラッチ回路および半導体集積回路

【課題】 抵抗変化素子の磁化特性が劣化することを防止し、読み出しマージン等の電気的特性の低下を防止する。

【解決手段】 不揮発性ラッチ回路は、相補の記憶ノードである第1および第2ノードを含むラッチ回路と、電流を流すことにより抵抗値が変化する第1および第2抵抗変化素子と、第1および第2抵抗変化素子をラッチ回路に接続するスイッチ回路とを有している。スイッチ回路は、外部からラッチ回路に論理が書き込まれる通常動作時に、第1および第2抵抗変化素子とラッチ回路との接続を遮断する。これにより、外部からラッチ回路の論理が書き換えられるときに、第1および第2抵抗変化素子に電流が流れることを防止でき、抵抗変化素子の磁化特性が劣化することを防止できる。この結果、読み出しマージン等の電気的特性の低下を防止できる。

(もっと読む)

高速量子化器

【課題】高速量子化器および最適化された時間遅延を提供する。

【解決手段】高速量子化器コンパレータの装置と方法は、3部を含む:プリアンプ部、再生ラッチ部、およびデータラッチ部。時間遅延は、再生ラッチ出力の最初の電圧を変えることによって減少される。電流源はコンパレータの底部に提供され、時間遅延最適化を可能にする。PMOS同等化スイッチが停止されたとき、クロック信号をフィードスルーにし、出力に電荷の注入を提供する。これらの電荷によって、コンパレータの時間遅延が可変となる。リセット時間が比較時間より長いために、非常に低い電流が出力電圧を決定する。

(もっと読む)

レベルシフト回路及びその方法

【課題】レベルシフト回路及びその方法の提供。

【解決手段】本発明のレベルシフト回路及びその方法は、レベルシフト回路のラッチ装置と電圧源の間に限流回路を接続して、前記ラッチ装置の駆動電流が設定値を超えないように制限する。これにより、レベルシフト回路を変換する時の消耗電流を減らし、通路の短いトランジスタを使用したラッチ装置を実現し、レベルシフト回路面積を縮小する。前記設定値は調節可能とし、レベルシフト回路の出力駆動能力を調整することにより、前記レベルシフト回路の変換速度を加速させることができる。

(もっと読む)

半導体集積回路装置

【課題】動作速度を低下させることなく、従来と略同程度のサイズの回路構成により消費電力の低減を図る。

【解決手段】実施形態の半導体集積回路装置は、第1の充電部及び放電部と、第2の充電部及び放電部とを有するフリップフロップと、出力ノードの正相出力と同一論理の入力信号が入力された場合には、第1の放電部及び第2の放電部の少なくとも一方の放電動作を停止させるよう構成された制御部とを具備し、第1の放電部は、入力信号に基づいて制御されるよう構成された第1の放電経路と、入力信号の反転信号によって制御されるよう構成された第2の放電経路とを具備し、第1及び第2の放電経路には、プリチャージノードの放電を許可する遷移期間を定める第1及び第2のトランジスタが夫々設けられ、第1及び第2の放電経路は、第3の放電経路に共通接続され、第3の放電経路上に、第3の放電経路の導通,非導通を制御する第3のトランジスタが設けられる。

(もっと読む)

1 - 20 / 170

[ Back to top ]