Fターム[5J039DB06]の内容

パルスの操作 (9,993) | しきい値の特性 (335) | 複数のしきい値を持つもの (101) | ウィンド型 (83) | 2以上の比較要素の出力を合成するもの (17)

Fターム[5J039DB06]に分類される特許

1 - 17 / 17

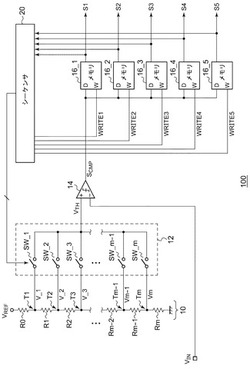

電圧検出回路、それを用いた温度検出回路、電子機器

【課題】回路面積、消費電力を低減するとともに、正しい電圧比較が可能な電圧比較回路を提供する。

【解決手段】抵抗ストリング10は、直列に接続された複数の抵抗の接続点に設けられた各タップに電圧を発生する。セレクタ12は、複数のスイッチを含み、ひとつのスイッチがオンした状態において、当該スイッチが接続されるタップの電圧を出力する。コンパレータ14は、入力電圧VINをセレクタ12の出力電圧と比較する。メモリ16_iは、それぞれがしきい値電圧VTHiごとに設けられ、書き込み信号WRITEiに応答してコンパレータ14の出力SCMPを格納して検出信号Siを生成する。シーケンサ20は、N個のメモリ16_1〜16_Nからの検出信号S1〜SNを受け、セレクタ12の複数のスイッチを制御するとともに、書き込み信号を生成する。

(もっと読む)

二値化回路

【課題】RFアナログ信号に直流成分が含まれていても正しく二値化する。

【解決手段】光ディスクから読み取ったRFアナログ信号をコンパレータ16でスライスレベルと比較することで二値化する。第1スライサ10はRFアナログ信号のピークレベルとボトムレベルの平均値をスライスレベルとして出力し、第2スライサ12は信号列の連続したパターンの部分におけるピークレベルとボトムレベルの平均値をスライスレベルとして出力する。切替スイッチ14でスライスレベルを切り替えて出力する。

(もっと読む)

診断回路、発振回路

【課題】リファレンスクロックを要することなく発振信号の周波数範囲を診断できる、回路規模の小さな診断回路等を提供する。

【解決手段】制御信号102に応じて周波数が変化する発振信号166の周波数範囲を診断する診断回路10であって、制御信号102を受け取り、制御信号102に基づく値である比較値と所定の限界値とを比較する比較器を含み、比較器が比較した結果に基づいて診断出力値100を生成する。所定の限界値として上限値と下限値とを定め、比較値と上限値とを比較する上限比較器と、比較値と下限値とを比較する下限比較器とを含み、上限比較器および下限比較器が比較した結果に基づいて、診断出力値100を生成する。

(もっと読む)

多入力差動増幅器

【課題】各動作モードにおいてレベルシフト回路を用いることなく所望の入力電圧範囲となる多入力差動増幅器を提供する。

【解決手段】差動部1は、バイアス部2と出力部3との間に設けられ、第一入力部10と第二入力部20とを有する。第一入力部10は、ソースがバイアス部2と接続され、ドレインが出力部3と接続された1個のn型MOSFET(M11)からなる。第二入力部20は、直列接続される2個のn型MOSFET(M21)、(M22)と、直列接続される2個のn型MOSFET(M23)、(M24)とが2列に並列接続される。また、入力端INaはM11のゲートに接続され、入力端INxはM22とM23のゲートに接続され、入力端INyはM21とM24のゲートに接続される。バイアス部2は1つの定電流源21を有し、出力部3は2つのp型MOSFET(Q1、Q2)で構成のカレントミラー回路を有する。

(もっと読む)

ヒシテリシス装置

【課題】簡易な構成でヒシテリシス特性を付与する。

【解決手段】ヒシテリシス装置1000は、複数の閾値に対応するオフセット電圧を入力信号Vinに付加した調整信号Vxを出力する入力信号調整部300と、調整信号Vxに基づいて2値化した第1信号10aを出力するコンパレータ10と、入力信号調整部300を制御して複数の閾値ごとにオフセット電圧を切り替えるとともに、オフセット電圧の切り換えごとに第1信号10aを取得し、複数の閾値に対応する第1信号10aと前回の出力信号DETとに基づいて今回の出力信号DETを生成する判定部200とを備える。

(もっと読む)

信号処理回路

【課題】差動信号の同相成分を有効に抑制する。

【解決手段】信号処理回路30の入力端子321および入力端子322には差動信号SINが供給される。差動増幅器42は、非反転入力端子PIN1と反転入力端子PIN2と反転出力端子POUT1と非反転出力端子POUT2とを有する。差動増幅器42には抵抗R1〜R4が接続される。制御回路46は、抵抗R1と抵抗R2との抵抗比R2/R1が抵抗R3と抵抗R4との抵抗比R4/R3に近づくように、抵抗R1〜R4の少なくともひとつの抵抗値を、反転出力端子POUT1および非反転出力端子POUT2の少なくとも一方の電位に応じて制御する。同相設定部44は、制御回路46の動作時に入力端子321と入力端子322とを同電位に設定する。

(もっと読む)

信号レベル検出回路

【課題】増幅回路の動作に必要な電流値を増加させることなく、ヒステリシスを用いて耐ノイズ特性を向上させることができる信号レベル検出回路を提供すること。

【解決手段】増幅回路6aの電圧利得は、増幅回路6bの電圧利得より大きく、切替装置6cは、ピークホールド回路7aに増幅回路6aの出力信号が入力している場合に比較回路9からアラーム信号を受信すると、ピークホールド回路7aに出力する信号を増幅回路6aの出力信号から増幅回路6bの出力信号に切り替え、ピークホールド回路7aに増幅回路6bの出力信号が入力している場合に比較回路9からアラーム信号を受信すると、ピークホールド回路7aに出力する信号を増幅回路6bの出力信号から増幅回路6aの出力信号に切り替える。

(もっと読む)

適応ループ帯域を有する位相同期ループ

【課題】向上されたループ安定度とより早いロッキング率を有する適応的位相同期ループを含む半導体装置を公開する。

【解決手段】本発明の実施形態では、ループの安定度のために第2電荷ポンプを用いない方法として具現されていて、結果的に、本発明の位相同期ループはより小さいチップダイ(chip die)面積を占める。本発明の他の実施形態では、複数の電荷ポンプが用いられて、従来技術に比べてより向上されたロッキング(locking)応答時間を得ることができる。

(もっと読む)

ヒステリシスコンパレータ

【課題】入力信号の振幅が当初の想定よりも小さい場合や入力信号の振幅変動が生じた場合でも、適正な出力信号を得ることができるヒステリシスコンパレータを提供する。

【解決手段】電圧レベルが連続的に変化する入力信号を互いに異なる電圧レベルを有する2つの閾値電圧に基づいて2値化判定し、この判定結果に応じた出力信号を生成するヒステリシスコンパレータであり、入力信号のトップピークを検出し、トップピークに応じたトップピーク検出電圧を生成するトップピーク検出部と、入力信号のボトムピークを検出し、ボトムピークに応じたボトムピーク検出電圧を生成するボトムピーク検出部と、トップピーク検出電圧の電圧レベルとボトムピーク検出電圧の電圧レベルの範囲内で第1および第2の閾値電圧を生成する閾値電圧生成部と、第1および第2の閾値電圧と入力信号の電圧レベルを比較して入力信号を2値化判定し、この判定結果に応じた出力信号を生成する電圧比較部と、を含む。

(もっと読む)

インタフェイス回路およびインタフェイス回路の動作方法

【課題】不正または異常動作による電子スイッチの誤動作を抑制できるようにする。

【解決手段】異常信号受信回路32は、被検出体検出装置の異常、または、正常動作不能状態の有無を示す異常検知信号をセンサ2より受信し、判定回路31は、異常検知信号により電子スイッチ1の異常、または、正常動作不能状態が検知されているか否かを判定し、電子スイッチ1の異常、または、正常動作不能状態が検知されていると判定した場合、電子スイッチ1からの被検出体の有無を示す検出信号を直前の状態に維持する判定信号を出力するか、または、被検出体が検出されていないことを示す判定信号にして出力し、出力回路33は、判定信号に基づいて、遊技球の有無の状態を示す状態信号を出力する。

(もっと読む)

電流電圧変換回路及び電流電圧変換方法

【課題】従来の電流電圧変換回路は、電源投入直後の初期状態に誤出力が発生する場合があった。

【解決手段】電流電圧変換回路は、入力電流に基づいて第1の電圧を生成する第1の電圧生成部と、第1の電圧生成部の入力電位と前記第1の電圧の昇圧側に所定の電圧差を有する第1の基準電圧を出力する基準電圧生成部と、前記第1の電圧と第1の電圧の降圧側に所定の電圧差を有し、前記第1の電圧の変動に対して遅延を有して変動する第2の電圧を生成する第2の電圧生成部と、前記第1の基準電圧と前記第2の電圧との大小関係に基づいて、いずれか一方を選択して第2の基準電圧を出力する第1の比較部と、前記第2の基準電圧と前記第1の電圧を比較する第2の比較部とを有する。

(もっと読む)

コンパレータ並びにA/D変換器

【課題】高速変換に適したフラッシュ型ADコンバータに使用することができるダイナミック・コンパレータを提供する。

【解決手段】ダイナミック・コンパレータは静止電流が全く流れず、低消費電力動作に最適な回路構成である。リニア領域で動作するNチャネル・トランジスタ1、2、3、4は抵抗値の大きさに応じたラッチ動作を行なうが、ラッチの時定数を微調整可能であるので、遅延時間のばらつき、素子(閾値電圧)のばらつきによるオフセットの影響によって劣化するビット・エラー・レートを改善することができる。

(もっと読む)

信号一致検出回路

【課題】信号一致検出回路および該回路で実施する方法。

【解決手段】信号一致検出回路は、第1差動トランジスタ対と、第1差動トランジスタ対と結合する第2差動トランジスタ対と、第2差動トランジスタ対と並列に第1差動トランジスタ対と結合する第3差動トランジスタ対とを含む。回路はまた、第1、第2および第3差動トランジスタ対と結合する第1入力信号端子を含み、この端子は、第1、第2および第3差動トランジスタ対へ送られる第1入力信号を受け取る。回路は更に、第1、第2および第3差動トランジスタ対と結合する第2入力信号端子を含み、この端子は、第1、第2および第3差動トランジスタ対へ送られる第2入力信号を受け取る。回路は更に、第1差動トランジスタ対と結合する電流源を含み、動作時に第2および第3差動トランジスタ対の複数の電流が組み合わされ、組み合わされた電流が、第1入力信号と第2入力信号とが一致するか否かを示す。

(もっと読む)

電圧差比較回路

【課題】高速動作が可能で単純な構成の電圧差比較回路を低コストに提供する。

【解決手段】同一構成の各変換器11,12は、2つの入力信号の電圧差を電流値に変換し、その電流値を出力電流として出力する。変換器11は入力信号IN1,IN2の電圧差(IN1−IN2)を電流値に変換する。変換器12は基準電圧VREF1,VREF2の電圧差(VREF1−VREF2)を電流値に変換する。電流比較器13は、変換器11の出力電流が変換器12の出力電流よりも大きい場合(すなわち、電圧差(IN1−IN2)が電圧差(VREF1−VREF2)よりも高い場合)には出力信号OUTをハイレベルにし、変換器11の出力電流が変換器12の出力電流よりも小さい場合(すなわち、電圧差(IN1−IN2)が電圧差(VREF1−VREF2)よりも低い場合)には出力信号OUTをローレベルにする。

(もっと読む)

コンパレータ回路

【課題】入力電圧の比較可能レベルを広げ、かつ比較レベルによる判定時間の変動、入力からみた出力に対する比較精度の変動を抑えられるコンパレータ回路の提供。

【解決手段】第1差動増幅回路11は、入力電圧Vin+、Vin−の差に応じた電流を出力する。ソースフォロワ回路18は、入力電圧Vin+、Vin−を電圧SV+、SV−にレベルシフトする。第2差動増幅回路12は、その電圧SV+、SV−の差に応じた電流を出力する。受け渡し回路16は、入力電圧Vin+、Vin−の動作コモン電位レベルに応じて第1差動増幅回路1と第2差動増幅回路2の動作を切り替える。電流電圧変換回路15は、第1差動増幅回路11の出力電流と第2差動増幅回路12の出力電流とを加算し、その加算に応じた出力電圧Vout を出力する。

(もっと読む)

信号検出回路

【課題】 高速信号に対応し、精度良く差動信号の検出が可能であり、回路のレイアウト面積を縮小し、消費電力を低減することができる。

【解決手段】 本発明による信号検出回路は、2個ある信号検出用のコンパレータ(COMP10、COMP21)の双方に対し、直流基準電圧(Vref)に接続された第3のコンパレータ(COMP22)を接続してコモンモード電位(VR1、VR2)を設定し、信号検出用のコンパレータ(COMP10、COMP21)から出力される差動信号(CMP9Eout、CMP10Eout)の差動排他的論理和を出力し、設定したレベル以上の差動入力信号(Sin)を検出する。

(もっと読む)

アナログ・ディジタル変換回路

【課題】 回路構成が簡単で、消費電流の少ないA/D変換回路を提供する。

【解決手段】 変換対象のアナログ入力信号AIが共通に与えられ、それぞれ異なる論理閾値電圧を有する複数のインバータ10i(但し、i=1〜2n−1)を設け、これらのインバータ10iから出力される信号S10iをデコーダ20でデコードして、nビットのディジタル出力信号DOを得る。各インバータ10iは、PMOS11iとNMOS12iを組み合わせたCMOSインバータで、これらのPMOS11iとNMOS12iゲート幅の比を変えることによって、それぞれ異なる論理閾値電圧を持たせるように構成する。

(もっと読む)

1 - 17 / 17

[ Back to top ]