Fターム[5J039DB17]の内容

パルスの操作 (9,993) | しきい値の特性 (335) | 入力信号レベルに応動するもの (84) | 複数のしきい値の選択 (14)

Fターム[5J039DB17]に分類される特許

1 - 14 / 14

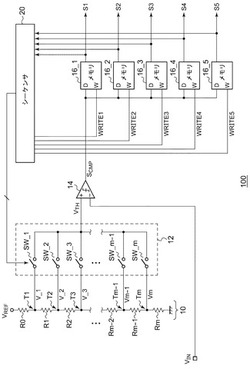

電圧検出回路、それを用いた温度検出回路、電子機器

【課題】回路面積、消費電力を低減するとともに、正しい電圧比較が可能な電圧比較回路を提供する。

【解決手段】抵抗ストリング10は、直列に接続された複数の抵抗の接続点に設けられた各タップに電圧を発生する。セレクタ12は、複数のスイッチを含み、ひとつのスイッチがオンした状態において、当該スイッチが接続されるタップの電圧を出力する。コンパレータ14は、入力電圧VINをセレクタ12の出力電圧と比較する。メモリ16_iは、それぞれがしきい値電圧VTHiごとに設けられ、書き込み信号WRITEiに応答してコンパレータ14の出力SCMPを格納して検出信号Siを生成する。シーケンサ20は、N個のメモリ16_1〜16_Nからの検出信号S1〜SNを受け、セレクタ12の複数のスイッチを制御するとともに、書き込み信号を生成する。

(もっと読む)

ヒシテリシス装置

【課題】簡易な構成でヒシテリシス特性を付与する。

【解決手段】ヒシテリシス装置1000は、複数の閾値に対応するオフセット電圧を入力信号Vinに付加した調整信号Vxを出力する入力信号調整部300と、調整信号Vxに基づいて2値化した第1信号10aを出力するコンパレータ10と、入力信号調整部300を制御して複数の閾値ごとにオフセット電圧を切り替えるとともに、オフセット電圧の切り換えごとに第1信号10aを取得し、複数の閾値に対応する第1信号10aと前回の出力信号DETとに基づいて今回の出力信号DETを生成する判定部200とを備える。

(もっと読む)

電圧範囲判断回路

【課題】電圧範囲判断回路を提供すること。

【解決手段】電圧範囲判断回路は対象電圧生成部、選択電圧生成部、比較電圧選択部及び出力信号生成部を含む。対象電圧生成部は、入力電圧に基づいて対象電圧を生成する。選択電圧生成部は、基準電圧に基づいて第1〜第2選択電圧を生成する。比較電圧選択部は、出力信号に基づいて、第1〜第2選択電圧の中で1つを選択して比較電圧に出力する。出力信号生成部は、対象電圧と比較電圧を比べて出力信号を生成する。電圧範囲判断回路は外部ノイズが流入する場合も入力電圧の電圧範囲を正確に判断することができる。

(もっと読む)

比較回路、集積回路装置及び電子機器

【課題】ヒステリシス幅を設定できる比較回路、集積回路装置及び電子機器等を提供すること。

【解決手段】比較回路は、第1の入力端子に入力信号SINが入力され、第2の入力端子に比較用の基準電圧VRが入力されるコンパレーター10と、コンパレーター10の出力信号SQをモニターする制御部20と、制御部20からのしきい値電圧制御信号SVTが入力される電圧生成回路30とを含み、電圧生成回路30は、コンパレーター10の出力信号SQの電圧レベルが第1のレベルである場合には、基準電圧VRとして、ヒステリシス幅を規定する高電位側しきい値電圧又は低電位側しきい値電圧のいずれか一方である第1のしきい値電圧を出力し、出力信号SQの電圧レベルが第2のレベルである場合には、基準電圧VRとして、高電位側しきい値電圧又は低電位側しきい値電圧の他方である第2のしきい値電圧を出力する。

(もっと読む)

信号レベル検出回路

【課題】入力信号に対する検出閾値の変更を入力信号の増幅により相対的に実現する信号レベル検出回路は、入力信号の増幅に用いる可変ゲインアンプを要するため、回路規模が大きくなり、また消費電力が増加する。

【解決手段】抵抗分圧回路54x,54yはそれぞれ、入力信号レベルAに応じた差の差動信号を構成する電位VX1,VY1を入力され、VX1,VY1から接地電位までの電位範囲を分圧して複数のVX,VYを生成する。選択回路56は、VX,VYの組み合わせのいずれかを選択する。コンパレータ58は選択されたVX,VYの大小を比較し、検出閾値に対するAの高低を判定する。VX,VYの各組は、Aの変化に対して大小関係が反転する交換点を有し、また、組毎の交換点は、Aの異なる位置に存在するように設定される。選択回路56により選択されるVX,VYの組に応じて検出閾値が変更される。

(もっと読む)

クランプ機能付コンパレータ

【課題】追加的な製造プロセスを不要としながら一定且つ任意のクランプ電圧を設定できる。

【解決手段】信号入力線6の電圧が参照電圧VHよりも低い場合、信号ScがLレベル、スイッチ回路16がオフ、スイッチ回路17がオンとなり、FET14、15がオフする。信号入力線6の電圧が参照電圧VH以上になると、信号ScがHレベル、スイッチ回路16がオン、スイッチ回路17がオフとなり、クランプ回路4が動作可能となる。入力電圧がさらに上昇してクランプ電圧VCL以上になると、FET13がオンとなり、抵抗11、端子1a、抵抗12を介してFET13、14に電流が流れ、それに応じてFET15に電流が流れてクランプ動作する。

(もっと読む)

適応ループ帯域を有する位相同期ループ

【課題】向上されたループ安定度とより早いロッキング率を有する適応的位相同期ループを含む半導体装置を公開する。

【解決手段】本発明の実施形態では、ループの安定度のために第2電荷ポンプを用いない方法として具現されていて、結果的に、本発明の位相同期ループはより小さいチップダイ(chip die)面積を占める。本発明の他の実施形態では、複数の電荷ポンプが用いられて、従来技術に比べてより向上されたロッキング(locking)応答時間を得ることができる。

(もっと読む)

信号入出力状態検出回路

【課題】双方向信号を使用するデバイス間において、信号の方向、両デバイスの信号同時出力による衝突、両デバイスとも出力のない状態等を検出する。

【解決手段】デバイス1Aとデバイス1B間の双方向信号の方向検出動作時、アナログスイッチ11のA点はD点に接続され、B点はC点に接続される。制御回路13は、レベル検出回路12−1、12−2の出力信号Vout1、Vout2の立ち下がりの有無、入力信号Vin1、Vin2、出力信号Vout1、Vout2のレベルの組み合わせから、デバイス1A、1BのポートPA、PBが共にドライブされている場合の双方向信号の方向、バイス1A、1BのポートPA、PBが共にドライブされていない状態、デバイス1A、1Bの信号同時出力による信号衝突、デバイス1A、1Bが正常動作していない、のいずれかのデコード結果を出力する。

(もっと読む)

複数の電流信号受信器に対するスレッシュホールド制御回路

【課題】電流信号の形態におけるデータ信号を受取る複数の信号受信器に対して一定の信号検知スレッシュホールドを維持するためのキャリブレーション回路及び方法。

【解決手段】複数個の電流信号受信器に対する複数個の信号スレッシュホールドを制御するための制御回路は、所定の信号パターンを具備する入力して来る電流信号のうちの1つの値が検知され且つ使用されてデータ信号検知スレッシュホールドを制御するための信号受信器の各々に対するスレッシュホールド制御信号を発生する。

(もっと読む)

AD変換器、無線受信機

【課題】消費電力の増大を招くことなく、受動素子の数を削減しチップ占有面積を小さくして低コスト化を図ることが可能なAD変換回路を提供すること。

【解決手段】n次元ベクトルを表すm(n<m<2n)個のアナログ信号のそれぞれを1ビット以上に量子化してm個並列の量子化信号を生成する量子化部と、このm個並列の量子化信号をそれぞれ復号してm個の復号アナログ信号を生成する復号部と、このm個のアナログ信号のそれぞれと上記m個の復号アナログ信号のそれぞれとの差のそれぞれを定数倍してm個の増幅残差信号を出力する残差増幅部と、を有する変換ステージを複数縦続接続して備えた変換部と、この変換部の変換ステージそれぞれにおけるm個並列の量子化信号を該変換ステージの縦続位置に応じた遅延量を考慮して並列位置ごとに合成し、m個並列のディジタル信号を生成する合成部とを具備する。

(もっと読む)

電流電圧変換回路及び電流電圧変換方法

【課題】従来の電流電圧変換回路は、電源投入直後の初期状態に誤出力が発生する場合があった。

【解決手段】電流電圧変換回路は、入力電流に基づいて第1の電圧を生成する第1の電圧生成部と、第1の電圧生成部の入力電位と前記第1の電圧の昇圧側に所定の電圧差を有する第1の基準電圧を出力する基準電圧生成部と、前記第1の電圧と第1の電圧の降圧側に所定の電圧差を有し、前記第1の電圧の変動に対して遅延を有して変動する第2の電圧を生成する第2の電圧生成部と、前記第1の基準電圧と前記第2の電圧との大小関係に基づいて、いずれか一方を選択して第2の基準電圧を出力する第1の比較部と、前記第2の基準電圧と前記第1の電圧を比較する第2の比較部とを有する。

(もっと読む)

シュミットトリガ回路及びそれを具備する半導体集積回路

【課題】無駄な電流を減少させると共に入出力特性のヒステリシス幅の調整範囲を広くすることが可能なシュミットトリガ回路を提供する。

【解決手段】このシュミットトリガ回路1は、入力信号を反転して出力する第1のインバータ2と、第1のインバータ2の出力信号を反転して出力する第2のインバータ3と、入力信号及び第2のインバータ3の出力信号に基づいて、第1のインバータ2の出力ノードと高電位側の電源電位との間及び/又は第1のインバータ2の出力ノードと低電位側の電源電位との間のインピーダンスを調整するインピーダンス調整回路4とを具備する。

(もっと読む)

改良型のフラッシュアナログデジタルコンバータ

【課題】差動抵抗ラダーの駆動源から最大遅延を受ける中央ノードの遅延量を低減するADCを提供する。

【解決手段】差動アナログデジタルコンバータ(ADC)は、第1及び第2の抵抗ラダーレッグ、第1及び第2の増幅器、並びに複数の比較器を備える。各抵抗ラダーレッグは、中間ノードに接続する第1の端部及び電流源に接続する第2の端部を有する二つの抵抗を含む。第1の増幅器は、入力信号の第1の相に基づく電圧を第1の抵抗ラダーレッグの中間ノードに印加する。第2の増幅器は、入力信号の第2の相に基づく電圧を第2の抵抗ラダーレッグの中間ノードに印加する。複数の比較器は各々、第1及び第2の入力を有し、第1の入力は第1の抵抗ラダーレッグの二つの抵抗のうち一方に接続し、第2の入力は第2の抵抗ラダーレッグの二つの抵抗のうち一方に接続する。

(もっと読む)

半導体装置

【課題】 基準電圧が入力される増幅回路内のトランジスタにおいて製造プロセスの変動に起因する閾値の変動が生じた場合に外部入力信号に対して高速な出力を得られる半導体装置を提供する。

【解決手段】半導体装置1は、外部電源電圧Vccと接地電圧Vssとを供給され、外部電源電圧Vccを基に基準電圧Vrefを生成する基準電位発生回路2と、外部電源電圧Vccと接地電圧Vssとを供給され、前記基準電位発生回路2で生成される前記基準電圧Vrefと外部入力信号Vinの電圧とを比較してその比較結果に応じて出力信号Voutを生成する増幅回路3と、前記基準電圧Vrefを調節するためのデータが記憶された記憶回路4とを有する。

(もっと読む)

1 - 14 / 14

[ Back to top ]