Fターム[5J039EE23]の内容

パルスの操作 (9,993) | パルス分配 (453) | 出力波形 (137) | 他相のパルスとオーバーラップしないもの (66) | 間欠形のもの (20) | 180度の位相差を持つもの (19)

Fターム[5J039EE23]に分類される特許

1 - 19 / 19

クロックバッファ回路及びこれを用いたクロック分配回路

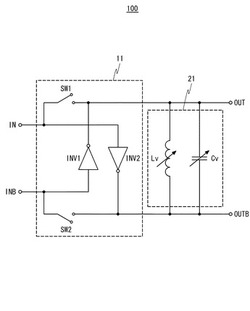

【課題】小さな回路規模により広帯域のクロック信号に対応できるクロックバッファ回路を提供すること。

【解決手段】本発明の一態様であるクロックバッファ回路100は、ドライバ部11及びLCタンク部21を有する。ドライバ部11は、クロック入力IN及びINBからの入力クロック信号の少なくとも正転出力を、それぞれクロック出力OUT及びOUTBへ出力する。LCタンク部は、ドライバ部11とクロック出力OUT及びOUTBとの間に配置される。ドライバ部11は、入力クロック信号の周波数に対応した制御信号に応じて、ドライバ部11の入力と出力とを短絡させるスイッチSW1及びSW2を有する。

(もっと読む)

半導体装置

【課題】マルチプレクサとクロック分割回路との間における相互の電源ノイズの影響を低減する。

【解決手段】外部クロック信号CKに基づいて内部クロック信号LCLK1を生成するDLL回路100と、内部クロック信号LCLK1に基づいて、互いに位相の異なる内部クロック信号LCLK2,LCLK2Bを生成するクロック分割回路200と、内部データ信号CD,CEに基づいて、クロック信号LCLK2,LCLK2Bにそれぞれ同期した内部データ信号DQP,DQNを出力するマルチプレクサ300とを備える。クロック分割回路200に供給される内部電源電圧VPERI2とマルチプレクサ300に供給される内部電源電圧VPERI3は、互いに異なる電源回路82,83によって生成され、且つ、該半導体装置内で分離されている。これにより、相互にノイズの影響を及ぼし合うことがなくなる。

(もっと読む)

電子機器

【課題】複数の接続部に動作クロックを出力すると、それぞれのクロックの立ち上がり及び立ち下がりにより生じる電磁波の周りへの影響が大きい。

【解決手段】電子機器は、信号の授受する動作クロックの周波数が同じ複数の外部機器が接続される複数の接続部と、複数の接続部に対して互いに位相をずらした動作クロックを出力するクロック出力部とを備える。クロック出力部は、複数の接続部のうちの2つに対して互いに逆位相の動作クロックを出力する。

(もっと読む)

多相クロック生成回路

【課題】N相から2N相に切り替わったときに位相関係が不適切にならないようにする。

【解決手段】多相クロック生成回路は,基準クロックに同期して0°,90°の位相の中間クロックを生成する第1の分周器と,0°の中間クロックに同期して0°,90°の位相の第1群の出力クロックを生成する第2の分周器と,90°の中間クロックに同期して45°,135°の位相の第2群の出力クロックを生成する第3の分周器と,第1の分周器と第3の分周器との間に設けられ,切替信号に応じて,90°の中間クロックまたは固定値のいずれかを第3の分周器に供給するセレクタとを有する。さらに,切替信号が2N相モードのときに,第1群の出力クロックと第2群の出力クロックの位相関係にエラーがあるか否かを検出するエラー検出回路と,エラー検出回路がエラーを検出したときに基準クロックと非同期のタイミングで2N相モードの切替信号をセレクタに出力する再リセット回路とを有する。

(もっと読む)

クロック分配回路及びその回路を含む半導体回路装置

【課題】

半導体チップを製造する際の製造バラツキ又は半導体チップ内の半導体回路の動作条件による、複数の最終バッファから出力される複数のクロック間の位相差を軽減することが可能なクロック分配回路を提供することを目的とする。

【解決手段】

回路装置内に配置されたクロック分配回路であって、リング状のクロック配線と、前記クロック配線に接続し、自己発振により、前記クロック配線内に第1クロック信号を発生させる発振回路と、前記回路装置内において、2以上の場所それぞれに、配置され、第2クロック信号を出力する2以上の位相調整回路と、を備え、前記位相調整回路それぞれは、配置場所に応じた位相を有する前記第1クロック信号を受け取り、前記位相調整回路それぞれが受け取った前記第1クロック信号間の位相差よりも、前記位相調整回路それぞれが出力する前記第2クロック信号間の位相差を減じる調整を行うことを特徴とするクロック分配回路。

(もっと読む)

半導体装置

【課題】入力信号に基づいて位相の一致した相補の出力信号を生成する。

【解決手段】入力信号INTを受けて反転信号INBを出力するインバータ11と、反転信号INBを受けて内部信号INTTを出力するインバータ12と、反転信号INBを電源とし、入力信号INTを受けて内部信号INBBを出力するインバータ21と、を備える。本発明によれば、一方の信号パス上の信号を他方の信号パスに含まれるインバータの電源として用いていることから、調整用の容量や抵抗を付加することなく、一対の出力信号の位相を正確に一致させることが可能となる。

(もっと読む)

多相クロック生成回路

【課題】

位相ノイズが少ない多相クロック生成回路を提供する。

【解決手段】

多相クロック生成回路は,基準クロックを生成する基準クロック生成器と,リング状に接続された複数の遅延回路を有し,前記複数の遅延回路がそれぞれ位相がずれた出力クロックを出力する多相クロック発振器と,前記複数の遅延回路のいずれかの出力端子に前記基準クロックを供給する基準クロック注入回路とを有する。多相クロック発振器のクロックの位相ノイズを低減し周波数変動が抑制できる。

(もっと読む)

単相差動変換回路

【課題】

正相出力信号と逆相出力信号とが180°の位相差で位相が一致する単相差動変換回路を提供する。

【解決手段】

単相差動変換回路は,単相入力信号が入力される入力端子と,正相出力信号が出力される正相出力端子と,正相出力信号と差動関係にある逆相出力信号が出力される逆相出力端子と,入力端子と正相出力端子との間に設けられ,直列に接続された第1,第2のインバータを少なくとも含む第1のインバータ列と,入力端子と逆相出力端子との間に設けられ,直列に接続された第3,第4,第5のインバータを少なくとも含み第1のインバータ列よりも段数が1段多い第2のインバータ列とを有し,第1のインバータ列は,さらに,第1のインバータの出力端子にドレインが接続され,導通しない電圧にゲートが接続されたトランジスタを有するダミーインバータを有する。好ましくは,第1,第2,ダミー,第3,第4,第5のインバータのゲート幅の比が,m/2:m2:m/2:1:m:m2であり,前記mはインバータの増倍率である。

(もっと読む)

パルス発生装置

【課題】良好な信号レベルのパルス信号を効率よく発生するのに好適なパルス発生装置を提供する。

【解決手段】パルス発生装置100を、遅延回路10と、バッファー回路20と、パルス発生回路30とを含んだ構成とし、遅延回路10を、M(Mは3以上の整数)個のインバーターI1〜IMを縦続接続した構成とし、バッファー回路20を、遅延回路10の各接続部から出力される遅延信号にそれぞれ対応するM個のバッファーB1〜BMを含み、バッファーB1〜BMによって遅延回路10からの遅延信号をバッファリングする構成とし、パルス発生回路30を、N(Nは1≦N<Mの整数)個の単位パルス発生回路31_1〜31_Nを含んだ構成とし、各単位パルス発生回路において、バッファー回路20を介して入力される複数の遅延信号に基づき、1つのパルス信号を構成する複数の単位パルス信号のうち2以上の単位パルス信号を発生するようにした。

(もっと読む)

クロック信号生成装置

【課題】本発明は、温度特性、電源電圧特性、個体バラツキを吸収し、最適なノンオーバーラップ時間を有する2相クロック信号を確実に生成できる信頼性の高いクロック信号生成装置を提供することを目的とする。

【解決手段】本発明のクロック信号生成装置は、ノンオーバーラップクロック信号を使用する負荷回路において使用される2相クロック信号の遅延時間を可変する可変遅延器と、2相クロック信号におけるHレベル区間のノンオーバーラップ時間を検出し、ノンオーバーラップ時間に応じた検出信号を出力するノンオーバーラップ検出器と、ノンオーバーラップ検出器からの検出信号に基づいて可変遅延器を制御する制御信号を生成する制御信号生成部と、を備えている。

(もっと読む)

相補信号生成回路

【課題】 容量素子のみによるこれまでのスキュー調整方法よりもスキューの微調整を可能にした相補信号生成回路を提供する。

【解決手段】 本発明による相補信号生成回路は、複数のインバータ(901、904、905、906)を含む第1の信号伝達経路と、インバータ(901、907、908)と抵抗素子903を含む第2の伝達経路とを有する。

(もっと読む)

情報処理装置、信号伝送回路及び信号伝送方法

【課題】 差動信号の位相差(遅延)を検出する回路が差動信号の伝送路に接続されていると、伝送路への付加容量が増大し、差動信号の波形劣化が大きくなるという問題がある。

【解決手段】 上記課題を解決するため、本発明は、受信回路に信号を送信する送信回路を含み、送信回路は、第1の周期でハイレベルとローレベルを繰り返す差動信号を、遅延量を変化させて受信回路に送信する信号送出部と、差動信号の差動電位差が基準値以上である間における、第1の周期の整数倍の時間間隔との差分が所定の時間間隔となる第2の周期の標本化信号による差動信号の標本化回数と、所定の時間間隔とにより、差動信号の差動電位差が基準値以上となっている期間を示すレベル確定期間を遅延量の変化に応じて算出する算出部と、差動信号の遅延量の変化に対応した前記レベル確定期間のそれぞれのうちで最も大きいものを検出する検出部とを含むことを特徴とする。

(もっと読む)

半導体メモリ装置のクロック生成回路

【課題】本発明は、P.V.T変化及び伝送距離により、立ち上りクロック及び立ち下りクロックの遷移タイミングがずれることを防止できる半導体メモリ装置のクロック生成回路を提供する。

【解決手段】本発明は、クロックを遅延させて遅延クロックを生成し、前記クロックを反転させて反転クロックを生成する位相スプリッタと、遅延クロック及び反転クロックをバッファリングして、立ち上りクロック及び立ち下りクロックとして出力するクロックバッファを含む。

(もっと読む)

半導体メモリ装置及びその駆動方法

【課題】デューティ補正された遅延固定クロックを生成することができ、1つのDLLだけでもデューティ補正が可能で、かつ、入力されるクロック信号のデューティ比を効率的に補正して出力することができる半導体メモリ装置を提供すること。

【解決手段】遅延固定動作により遅延固定クロックを生成するDLL回路と、前記遅延固定クロックと、その遅延固定クロックの偶数倍に分周したクロックとを用いて、前記遅延固定クロックのデューティ比を補正するデューティ補正回路とを備える半導体メモリ装置を提供する。

(もっと読む)

分相器

【課題】分相器を提供する。

【解決手段】外部クロック信号を入力し、相互180°の位相差を有する第1内部クロック信号及び第2内部クロック信号を発生させる分相器において、外部クロック信号をバッファリングして出力する第1バッファと、外部クロック信号を反転させて出力する反転部と、反転部の出力信号をバッファリングする第2バッファと、外部クロック信号を反転させて出力する第1補間用信号発生部と、反転部の出力信号を反転させて出力する第2補間用信号発生部と、を備え、第1バッファから出力される信号と第2補間用信号発生部から出力される信号とを補間して第1内部クロック信号を発生させ、第2バッファから出力される信号と第1補間用信号発生部から出力される信号とを補間して第2内部クロック信号を発生させることによって、分相器のスキューが最小化される。

(もっと読む)

CML回路及びそれを用いたクロック分配回路

【課題】電源投入時やクロックゲーティング時などクロック停止状態から復帰する際にクロック配線や次段クロックドライバのRC成分の影響で最初の一定期間クロック波形が出なくなることを防ぎつつ通常動作時や低速動作するテスト時に消費電力や電源ノイズを低減すること、また過剰な駆動力によって発生するクロック波形のリンギングを低減する。

【解決手段】クロック停止状態から復帰する際にのみブースト回路12を動作させる。通常同作用バッファ13は、レファレンス信号REFがアクティブである間は、ずっと動作する。

(もっと読む)

半導体装置

【課題】本発明は、低いコストでワンチップLSIと同等のデータ転送速度を達成する半導体システムを提供することを目的とする。

【解決手段】半導体装置は、外部から受信した受信クロック信号を入力として内部クロック信号を供給する内部クロック発生回路と、チップの一辺に配置され該内部クロック信号を出力するクロック送信用端子と、該一辺に配置された複数の入出力端子と、該内部クロック信号に基づいて入出力制御用クロック信号を生成する制御用クロック発生回路と、該入出力制御用クロック信号に同期して該入出力端子を介して外部へのデータ出力及び外部からのデータ取り込みを行う複数の入出力回路と、該制御用クロック発生回路と該複数の入出力回路の各々とを接続する同一長の複数の接続配線を含むことを特徴とする。

(もっと読む)

半導体装置

【課題】 タイミングマージンの改善を図った同期化回路を備えた半導体装置を提供する。

【解決手段】 第1導電型の第1と第2MOSの共通ソースと第1電位との間に第1導電型第3MOSを設け、第2電位と上記第1と第2MOSのドレインと間に第2導電型の第4と第5MOSを設け、上記第4と第5MOSに並列形態にゲートとドレインが交差接続された第2導電型の第6と第7MOSを設ける。上記第1MOSのゲートに入力信号を供給し、上記第2MOSのゲートを上記第1MOSのドレインに接続し、上記第3MOSのゲートにクロックを供給し、上記第4と第5MOSのゲートに上記クロックと同相クロックを供給して、上記第1と第2MOSのドレインから第1、第2信号を出力してRSフリップフロップ回路に伝える。

(もっと読む)

低振幅差動出力回路及びシリアル伝送インターフェース

【課題】 CMOS回路を用いた差動出力回路において、電源・温度・プロセス等の変動による影響により、不所望の大きさのVCM変動が発生している。

【解決手段】 本発明による低振幅差動出力回路は、相互に相補である正相駆動信号MINTと逆相駆動信号MINBとによる差動信号であるメインバッファ駆動信号MINT/MINBを出力するプレバッファ回路1と、プレバッファ1に接続され、メインバッファ駆動信号MINT/MINBに応答して差動出力信号OUTT/OUTBを出力するメインバッファ回路2とを備え、正相駆動信号MINTと逆相駆動信号MINBは、第1の電位VDDと第2の電位GNDとの電位差を振幅とし、正相駆動信号MINBと逆相駆動信号MINBは、前記第1の電位と前記第2の電位との中間の電位と、前記第1の電位との間の電位で同電位となる。

(もっと読む)

1 - 19 / 19

[ Back to top ]