Fターム[5J042DA04]の内容

Fターム[5J042DA04]に分類される特許

1 - 20 / 257

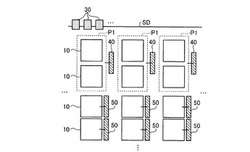

半導体集積回路

【課題】回路規模を低減しつつ任意の論理を実現可能な半導体集積回路を提供する。

【解決手段】実施形態の半導体集積回路は、第1論理ブロックを少なくとも1つ含む第1回路群と、第1論理ブロックよりも多い数の第2論理ブロックを含む第2回路群と、入力データを第1論理ブロックまたは第2論理ブロックへ入力する機能、および、第1論理ブロックまたは第2論理ブロックから出力される出力データを外部へ出力する機能を有する入出力部とを含む。第1回路群は、第1スイッチブロックと、第1電源制御回路とを有する。第1電源制御回路は、第1回路群に含まれる第1論理ブロックおよび第1スイッチブロックに対する電力の供給および停止を共通に制御する。第2回路群は、第2スイッチブロックと第2電源制御回路とを有する。第2電源制御回路は、第2回路群に含まれる論理ブロックおよび第2スイッチブロックに対する電力の供給および停止を共通に制御する。

(もっと読む)

プラグインカード収容装置及びプラグインカード制御方法

【課題】コンフィグデータ提供に要する処理負荷及び通信帯域の集中を分散できる。

【解決手段】FPGA21を搭載したプラグインカード10と、管理テーブル32を参照して、ネットワーク2に接続された異なるノード3に対してFPGA21のコンフィグデータのダウンロードを要求する主制御カード13内のCPU34とを有する。CPU34は、ダウンロード要求に応じてダウンロード元のノード3から取得されたコンフィグデータを、FPGA制御部22を通じて、FPGA21内のメモリ21Aに格納する。更に、CPU34は、FPGA21内のメモリ21A内のコンフィグデータに基づき、当該FPGA21に対するコンフィグレーションを実行する。

(もっと読む)

信号処理ユニット及びこれを備える統合管理システム

【課題】コンフィギュレーションデータの更新情報を極めて簡素な信号で表現させ得る信号処理ユニットを提供する。

【解決手段】信号処理ユニット100は、コンフィギュレーションデータの更新情報が周波数信号によって表現され、当該周波数信号がFPGAから出力される。また、CPUでは、入力された周波数信号の周波数fに基づいて、コンフィギュレーションデータの更新情報を認識する処理を行うこととされる。このため、FPGAでは、一つのデータpinから更新情報に係る信号を出力させることが可能となり、当該FPGAに配備される他のデータpinを有効に利用できる。また、CPUでは、周波数信号の周波数fに基づいて更新情報を特定できるので、パルスエッジ等の間隔を検出することで直ちに更新情報を認識することが可能となる。

(もっと読む)

FPGA内部回路変更方法および画像形成装置

【課題】FPGA内部回路を動的に書き換えた後の制御に待ち時間を発生させないFPGA内部回路変更方法および画像形成装置を提供する。

【解決手段】画像形成装置は、複数のコネクタから受信された信号を検知する検知手段と、検知手段による信号の検知をASICに通知する信号検知通知手段と、信号検知通知手段による信号検知通知を受けたASICにより複数のメモリの何れかから読み出された内部回路の書換情報に基づいて一の内部回路が動作中に他の内部回路を書き換える書換手段と、他の内部回路の書換完了をASICに通知する書換完了通知手段と、書換完了通知手段による書換完了通知と同時に出力切替回路及び出力変更回路を切り替える回路切替手段を備える。

(もっと読む)

情報処理装置、演算方法およびプログラム

【課題】 再構成可能なプログラマブル・デバイスを搭載するアクセラレータと連携して処理を実行する情報処理装置、演算方法およびプログラムを提供すること。

【解決手段】

本発明の情報処理装置110は、プログラマブル・デバイス150に接続されている。情報処理装置110は、各々前記プログラマブル・デバイス上で実現させる機能を定義する構成データが、複数格納される構成データ蓄積手段120と、各々対応する構成データによりプログラマブル・デバイス150上に実現される機能を利用するソフトウェア・プログラムが、複数格納されるプログラム蓄積手段118と、プログラマブル・デバイス150に、複数の構成データのうち選択された選択機能に対応する構成データを転送し、構成を要求する構成要求手段112とを含む。

(もっと読む)

再構成可能な集積回路ユニットを備えた論理回路及びその論路回路のエラー修正方法

【課題】エラー箇所の特定を実施する際に、システムを停止しないでエラー発生前の高信頼性までシステム性能を復帰させる。

【解決手段】同一動作を行う複数個の再構成可能な集積回路ユニットを備え、複数の該集積回路ユニットのそれぞれに複数のバンクを有する論理回路において、入力されたデータを、複数個の前記集積回路ユニットの各バンクに振り分けて入力する入力データ制御部と、複数個の集積回路ユニットの各バンクから出力されるデータを比較して、データ間の不一致を検出するエラー解析部と、エラー解析部から、データ間の不一致の通知を受けた場合に、複数個の集積回路ユニットの該当するバンクの再構成を行う構成情報制御部と、を備える。

(もっと読む)

FPGAシステム及び電子機器

【課題】書き込まれているコンフィグレーションデータでビット誤りを検出した場合に、置換用のコンフィグレーションデータを取得するためのアクセスを行う機能を有するFPGAを用いても、システム全体が安定に動作するFPGAシステムを提供する。

【解決手段】FPGAシステム(10)のコンフィグレーションコントローラ(16)は、FPGA(18)にコンフィグレーションデータ(24a)を書き込むとともに、第2記憶装置(22)に置換用のコンフィグレーションデータ(26a)を書き込む。FPGA(18)は、書き込まれているコンフィグレーションデータ(24a)にビット誤りが生じた場合、コンフィグレーションコントローラ(16)を介して第2記憶装置(22)に保存されている置換用のコンフィグレーションデータ(26a)を取得し、取得した置換用のコンフィグレーションデータ(26a)により、ビット誤りを訂正する。

(もっと読む)

論理装置及びそれを含む半導体パッケージ

【課題】論理装置及びそれを含む半導体パッケージを提供する。

【解決手段】短時間内に他の機能への再構成が可能な論理装置であり、第1機能情報によって定義された第1動作、及び第2機能情報によって定義された第2動作を行う第1機能ブロック;及び第1機能情報によって定義された第3動作、及び第2機能情報によって定義された第4動作を行う第2機能ブロック;を含み、第1機能ブロックは、設定情報を受信して第1機能情報及び第2機能情報のうち一つを選択し、選択された機能情報に基づいて、第1動作または第2動作を行い、第2機能ブロックは、設定情報を受信して第1機能情報及び第2機能情報のうち一つを選択し、選択された機能情報に基づいて、第3動作または第4動作を行うことを特徴とする論理装置を提供する。

(もっと読む)

埋込み浮動小数点構造を有するDSPブロック

【課題】浮動小数点機能を特殊処理ブロックの外に構築する必要性を減少させる、特殊処理ブロックを提供すること。

【解決手段】プログラマブル集積回路デバイス上の特殊処理ブロックであって該特殊処理ブロックは、第一の浮動小数点算術演算子段と、第二の浮動小数点算術演算子段と、該特殊処理ブロック内の構成可能インターコネクトであって、該構成可能インターコネクトは、該第一および第二の浮動小数点算術演算子段の各々に信号をルート付け、各々の外に該信号をルート付ける、構成可能インターコネクトとを含む、特殊処理ブロック。

(もっと読む)

プログラマブル論理の特定用途向け集積回路等価物および関連の方法

【課題】FPGAのASIC等価物をより効率的、経済的に提供すること。

【解決手段】FPGAのASIC等価物の提供は、複数のいわゆるハイブリッド論理素子(HLE)を含むASICアーキテクチャを使用することによって、促進され、より効率的、経済的に実行される。各HLEは、FPGA論理素子(LE)の完全機能の一部を提供可能である。ユーザの論理設計を実装する各FPGA LEの機能は、ユーザの論理を再合成することなく単一または複数のHLEへとマッピング可能である。必要な数のHLEだけが、各LEの関数を実行するために使用される。LE間および(1)単一のHLEまたは(2)HLE群間の1対1の等価性によって、FPGA設計とASIC設計との間のいずれの方向においてもマッピングが(再合成することなく)促進される。

(もっと読む)

プリエンファシス電圧ジッターを減少させる装置および方法

【課題】データ送信における電圧ジッターを減少させる送信器回路を提供すること。

【解決手段】第一の電流源と、該第一の電流源と第一のノードとの間に結合されている第一のフィルタと、該第一の電流源と第二のノードとの間に結合されている第二のフィルタと、第二の電流源と、該第二の電流源と第三のノードとの間に結合されている第三のフィルタと、該第二の電流源と第四のノードとの間に結合されている第四のフィルタと、該第一のノード、該第二のノード、該第三のノードおよび該第四のノードに結合されているドライバースイッチ回路などを含む、送信器回路。

(もっと読む)

部分再構成モジュールを設置およびルーティングするための方法および装置

【課題】標的デバイス上に部分再構成(PR)モジュールを設置し、かつルーティングするための方法および装置を提供すること。

【解決手段】標的デバイス上にシステムを設計するための方法であって、方法は、標的デバイス上のリソースをシステムの静的論理モジュールと部分再構成可能な(PR)モジュールとに割り当てることと、割り当てられたリソースを用いて、標的デバイス上のPRモジュールのうちの1つのインスタンスを並列に設置し、ルーティングすることのうちの1つを行うこととを含む。

(もっと読む)

プログラマブルLSI

【課題】低消費電力で、且つ、動的コンフィギュレーションにも対応できる高速なコンフィギュレーションを可能とし、起動するための時間が短いプログラマブルLSIを提供する。

【解決手段】複数のロジックエレメントと、複数のロジックエレメントに入力するためのコンフィギュレーションデータを記憶するメモリエレメントと、を有し、複数のロジックエレメントそれぞれは、コンフィギュレーションメモリを有し、コンフィギュレーションメモリに記憶されたコンフィギュレーションデータに応じて、異なる演算処理を行い、且つ、ロジックエレメント間の電気的接続を変更し、メモリエレメントは、チャネルが酸化物半導体層に形成されるトランジスタと、当該トランジスタがオフ状態となることによってフローティングとなるノードと、を有する記憶素子を用いて構成する。

(もっと読む)

半導体装置

【課題】耐タンパ性を有する、可変論理機能を実現するための記憶回路を有する半導体装置を提供する。

【解決手段】制御回路24は、記憶回路23の次の読出しアドレスを先に記憶回路23から読出した制御フィールドの情報または外部イベント入力に基づいて自律的に制御することが可能である。正規デコーダ28は、制御回路24から出力されるアドレスをデコードし、デコード結果に基づいて、データフィールドの少なくとも1つの正規メモリセルと、制御フィールドの少なくとも1つのメモリセルを選択する。冗長制御回路51は、イネーブル信号が活性化された場合に限り、制御回路24から出力されるアドレスと、所定の正規メモリセルのアドレスとが一致したときに、正規デコーダ28による選択を禁止し、データフィールドの少なくとも1つの冗長メモリセルと制御フィールドの少なくとも1つの冗長メモリセルを選択する。

(もっと読む)

プログラマブル論理の特定用途向け集積回路等価物および関連の方法

【課題】FPGAのASIC等価物をより効率的、経済的に提供する。

【解決手段】FPGAのASIC等価物の提供は、複数のいわゆるハイブリッド論理素子

(HLE)を含むASICアーキテクチャを使用することによって、促進され、より効率

的、経済的に実行される。各HLEは、FPGA論理素子(LE)の完全機能の一部を提

供可能である。ユーザの論理設計を実装する各FPGA LEの機能は、ユーザの論理を

再合成することなく単一または複数のHLEへとマッピング可能である。必要な数のHL

Eだけが、各LEの関数を実行するために使用される。LE間および(1)単一のHLE

または(2)HLE群間の1対1の等価性によって、FPGA設計とASIC設計との間

のいずれの方向においてもマッピングが(再合成することなく)促進される。

(もっと読む)

プログラマブルロジックデバイスのための特殊処理ブロック

【課題】プログラマブルロジックデバイスのための特殊処理ブロックを提供すること。

【解決手段】プログラマブルロジックデバイスのための特殊処理ブロックは、個々の乗算を計算せずに両方の乗算の部分積を加算して、2つの乗算の合計を実行する基本処理ユニットを組み入れる。そのような基本処理ユニットは、従来の別々の乗算器および加算器より少ない領域を消費する。特殊処理ブロックは、ブロックが様々なデジタル信号処理動作のために構成されることを可能にするために、ループバック機能とともに、入力および出力段を更に有する。

(もっと読む)

リコンフィギュラブルロジックブロック、並びに、これを用いたプログラマブル論理回路装置、及び、テクノロジマッピング方法

【課題】デバイスの小面積化と低消費電力化を実現することが可能なリコンフィギュラブルロジックブロック、並びにこれを用いたプログラマブル論理回路装置、及び、テクノロジマッピング方法を提供する。

【解決手段】最大K入力(x[0]〜x[K−1])のリコンフィギュラブルロジックブロック(K−A2LUT)は、m入力(y[0]〜y[m−1]、ただしmはKよりも小さくyはxに属する)の第1ルックアップテーブル1と、n入力(z[0]〜z[n−1]、ただしnはKよりも小さくzはxに属する)の第2ルックアップテーブル2と、p入力(c[0]〜c[p−1]、ただしpはKよりも小さくcはxに属する)の組み合わせ回路3と、組み合わせ回路3の出力に応じて第1ルックアップテーブル1と第2ルックアップテーブル2のいずれか一方を選択するセレクタ4と、を有する。

(もっと読む)

プログラマブル・ゲートアレイ部を備えたマスクプログラマブル論理装置

【課題】プログラマブルゲートアレイ部を備えるマスクプログラマブル論理装置を提供すること。

【解決手段】集積回路の基板上に配置される複数のマスク−プログラマブル領域と、上記マスク−プログラマブル領域に結合されると共に上記マスク−プログラマブル領域を相互接続するために基板上に配置される複数の相互接続導体と、基板上に配置される複数のゲートアレイ部とからなり、ゲートアレイ部はマスクプログラマブル論理装置上の回路設計の実行を促進する少なくとも一つの機能を達成するようにプログラム可能である集積回路上に配置されるマスク−プログラマブル論理装置。

(もっと読む)

電気回路および/または電子回路に関するコンフィギュレーション方法ならびにデバイス

【課題】同じタイプの特性量を有し、この特性量の値が相互に比例するいくつかの機能ブロックを備える電気回路をコンフィギュレーションする。

【解決手段】機能ブロックは、同様のタイプの少なくとも1組の電気素子(102a〜102d、104a〜104d)と、前記電気素子を互いに接続するおよび/もしくは電気回路100の残部に接続するための手段(106a〜106d、108a〜108d、110a〜110d)とにより構築され、テストされる1組の接続コンフィギュレーションのそれぞれに対して、電気回路のパラメータの値を測定するステップと、テストされる結合コンフィギュレーションの中から、測定されたパラメータの値が、少なくとも1対の機能ブロックの特性量の値間の不整合が最小の1つのコンフィギュレーションを選択するステップと、選択されたコンフィギュレーションに従って、接続する手段をポジショニングするステップとを含む。

(もっと読む)

プログラマブルロジックデバイス集積回路上の高速シリアルデータレシーバ用のデシリアライザ回路網

【課題】多数の異なるプロトコルに対して、および広範囲のデーターレートに対して、シリアル形式のデータをパラレル形式のデータに変換することが可能な、デシリアライザ回路網を提供する。

【解決手段】プログラマブルロジックデバイス(「PLD」)などの高速シリアルデータレシーバ回路網用のデシリアライザ回路網(10)は、シリアルデータを任意の複数のデータ幅を有するパラレルデータに変換するための回路網を含む。該回路網(10)はまた、広範囲の周波数の中の任意の周波数で動作可能である。該回路網(10)は様々な観点において構成可能/再構成可能であり、その構成/再構成の少なくとも1部分はダイナミックに(すなわち、PLDのユーザーモードオペレ−ションの間に)制御され得る。

(もっと読む)

1 - 20 / 257

[ Back to top ]