Fターム[5J043DD09]の内容

Fターム[5J043DD09]に分類される特許

1 - 20 / 25

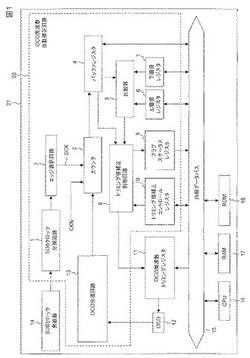

半導体装置

【課題】発振周波数変動の許容範囲を任意に設定可能にする。

【解決手段】半導体装置(21)は、トリミングレジスタ(11)に保持されたトリミング値によって発振周波数が変更される発振器(12)と、発振周波数を補正可能な補正回路(20)とを含む。上記補正回路は、上限値を設定可能な上限値レジスタ(6)と、下限値を設定可能な下限値レジスタ(7)と、発振周波数を分周するための分周回路(13)と、分周回路の出力をカウントするカウンタ(3)とを含む。さらに上記補正回路は、カウンタの出力を保持可能なバッファレジスタ(4)と、バッファレジスタの保持値が、上限値と下限値との間に入っているか否かを判別する比較器(5)と、その判別結果に基づいてトリミング値を補正するトリミング値補正制御回路(8)とを含む。ユーザは、上限値と下限値とによって、発振周波数変動の許容範囲を任意に設定することができる。

(もっと読む)

クロック発振回路

【課題】発振周波数のトリミングを行うクロック発振回路であって、CR発振回路の特性に起因する発振周波数のばらつきを低減することが可能なクロック発振回路を提供する。

【解決手段】クロック発振回路は、周波数調整コードに応じた発振周波数のクロック信号を生成する発振部101と、発振部101の発振周波数をカウントするOSCクロックカウンタ102と、外部接続された水晶発振器の発振周波数をカウントする基準クロックカウンタ103と、両発振周波数の比較を行う比較回路104とを備える。また、周波数調整コードの自動探索を行う探索回路105を備える。探索回路105は、周波数調整動作時において、発振部101に対する周波数調整コードの設定と、比較回路104による比較結果に応じた周波数調整コードの更新とを繰り返し行うことにより、周波数調整コードの自動探索を行う。

(もっと読む)

発振周波数補正装置

【課題】同期信号の検出が困難なときにも正確な発振周波数のクロック信号を生成できるようにした発振周波数補正装置を提供する。

【解決手段】電源投入時の劣化検出タイミングにおいて、定電流源23から抵抗器22に通電して得られたA/D変換器6のAD変換値(抵抗器22の端子電圧VR)に基づいて、CPU2が逓倍数設定値FMULRを補正する。この場合、定電流源20を用いることなく定電流源23が作動して抵抗器22に通電する。CPU2は、抵抗器22の端子電圧を測定することでCR発振器14内の抵抗器R1の抵抗値の経年変化を反映し、この変化に基づいてCR発振回路8のクロック信号CLKの逓倍数設定値FMULRを補正する。

(もっと読む)

電子機器およびクロック補正方法

【課題】 RC発振器によりクロック信号を生成するシステムにおいて、クロック信号の周波数を大きく変動させずに補正して規定の範囲に保つことのできる電子機器およびクロック補正方法を提供することにある。

【解決手段】 RC発振器の抵抗または容量の設定を切り替えてクロック信号の周波数を複数段階に変更可能な周波数変更手段と、この複数段階の変更量を表わしたトリミングテーブルを記憶する記憶手段と、周波数変更手段の設定を切り替えてクロック信号の周波数を補正するクロック補正制御手段とを備えた電子機器およびそのクロック補正方法である。そして、クロック補正制御手段は、トリミングテーブルのデータに基づき、クロック信号の周波数を補正前の周波数から規定の周波数へ次第に近づいていくように周波数変更手段の設定を切り替えて(S7,S8)、クロック信号の周波数を補正する。

(もっと読む)

半導体装置

【課題】CMOSトランジスタによって構成されたVCOを備えた半導体装置において、発振信号の発振振幅のばらつきの抑制および低消費電力化を実現する。

【解決手段】VCO30は、CMOSトランジスタによって構成されたLCタンクVCOと、VCOの発振周波数帯域から一の発振周波数を選択するための周波数選択信号を生成する自動周波数選択回路42と、VCOの制御電圧を生成するPLL32と、周波数選択信号に基づいて差動型のMOSトランジスタのゲートに供給するバイアス電圧を調整するバイアス回路50とを備える。

(もっと読む)

発振周波数補正方法及び発振周波数補正装置

【課題】電子製品の発振周波数を正確に補正するために用いる発振周波数補正方法を提供する。

【解決手段】発振周波数補正方法は、発振周波数に対応するクロック信号を生成するアジャスタブル周波数生成ユニットを有する電子製品の発振周波数を補正するために用いる。発振周波数補正方法は、標準周波数報時局から発信された時間電波信号を受信する上、前記時間電波信号を対応する複数のパルス信号に変換するステップS1と、前記複数のパルス信号及び前記クロック信号を演算し、対応する制御信号を生成するステップS2と、前記制御信号を利用することにより、前記アジャスタブル周波数生成ユニットが生成する前記クロック信号を調整し、対応する前記発振周波数を補正するステップS3と、を含む。

(もっと読む)

データラッチ回路およびそれを用いた試験装置

【課題】多様な信号形式のDUTからのデータを取り込み可能なデータラッチ回路を提供する。

【解決手段】データ入力端子INは、シリアル形式のデータ信号DINが入力される。n個(nは2以上の整数)のクロック入力端子CLK1〜CLKnは、それぞれにクロック信号CLK1〜CLKnが入力される。ある入力フリップフロップFFiは、データ信号DINを対応するクロック信号CLKiに応じたタイミングでラッチする。シリアルパラレル変換器SPiは、シリアル形式のデータ信号DINを対応するクロック信号CLKiを用いてパラレル形式の中間データ信号DINTiに変換する。データセレクタMUX1は、n個の中間データ信号DINT1〜nのうち選択信号SELに応じたひとつを選択する。

(もっと読む)

半導体集積回路

【課題】複数の無線通信チャンネルについて、PLL回路全体の動作特性に基づいて電圧制御発振器の精密なキャリブレーションを行う。

【解決手段】半導体集積回路は、高周波信号を生成する電圧制御発振器を含むPLL回路と、電圧制御発振器のトランジスタに選択的に負荷される複数のキャパシタと、複数の無線通信チャンネルについて電圧制御発振器の発振周波数を補正するためのキャパシタに関する情報を格納する格納部と、キャリブレーションモードにおいて、複数の無線通信チャンネルについてPLL回路のループ特性を測定することにより補正用キャパシタに関する情報を格納部に格納し、通常動作モードにおいて、選択された無線通信チャンネルに従って、格納部に格納されている情報を読み出すことにより補正用キャパシタを決定するキャリブレーション回路とを具備する。

(もっと読む)

基準パルス生成装置

【構成】基準パルスは、HDMIトランスミッタ36のクロック生成動作のために参照される。CPU28は、HDMIトランスミッタ36のクロック作成動作をリセットし、基準パルスのレベルをOS用タイマTM1のオーバフローに応答してLレベルに変更するとともに、フリーランタイマTM2の値を“CAL_START_TIME”として検出するとともに、HDMIトランスミッタ36のクロック作成動作をリセットする。CPU28はさらに、その後のOS用タイマTM1のオーバフローに応答して基準パルスのレベルをHレベルに変更し、これに関連してフリーランタイマTM2の値を“CAL_STOP_TIME”として検出する。“CAL_STOP_TIME”と“CAL_START_TIME”との差分を表す“ΔTM”が既定範囲から外れると、CPU28は、上述の処理を再起動する。

【効果】クロック周波数の精度を確保することができる。

(もっと読む)

デューティ比制御回路、デューティ比制御回路の制御方法、及びプログラム

【課題】小さな回路規模により発光素子の輝度を緩やかに変化させることを可能にする。

【解決手段】デューティ比制御回路は、デューティ比を変更することが可能なパルス信号の変更前のデューティ比である第1のデューティ比と、該パルス信号の変更後のデューティ比である第2のデューティ比とを保持する保持手段と、所定のパルス周期で前記パルス信号を生成するパルス生成回路と、前記パルス生成回路が生成する前記パルス信号のデューティ比を制御することにより、前記パルス生成回路の状態を、前記保持手段により保持された前記第1のデューティ比のパルス信号を生成する状態から、デューティ比の異なるパルス信号を生成する時間の比率を段階的に変化させる状態を経て、前記保持手段により保持された前記第2のデューティ比のパルス信号を生成する状態へ移行させるデューティ比制御手段と、を有する。

(もっと読む)

発振器

【課題】 本発明は、発振器が搭載される電子機器に応じた立ち上がり時間を有する出力信号を生成することができ、従って出力信号を高精度に生成することができる発振器を提供することを目的とする。

【解決手段】 発振部200から出力される中間出力信号に対して、それぞれ異なる波形整形を行う複数の波形整形回路500A〜500Cを有する波形整形部300と、複数の波形整形回路500A〜500Cの中から選択された波形整形回路500に対応するデータを記憶する記憶部400と、記憶部400に記憶されているデータに基づいて、波形整形部300が有する複数の波形整形回路500A〜500Cの中から選択された波形整形回路500によって、中間出力信号に対して波形整形を行わせる制御部450とを備える。

(もっと読む)

パルス発生回路及びパルス発生回路を備えた電子機器

【課題】PVTに依存せずに安定した周波数を出力する。

【解決手段】出力する第1の出力信号Vf1の周波数を第1の制御電圧VC1で制御する第1の電圧制御発振器11と、第1の出力信号Vf1及び基準信号CLKに基づき第1の出力信号Vf1の周波数を一定に維持する第1の制御電圧VC1を生成する制御電圧生成部13と、を含む位相同期回路10と、出力する第2の出力信号Vf2の周波数を第2の制御電圧VC2で制御する第2の電圧制御発振器20と、第1の制御電圧VC1に基づき第2の出力信号Vf2の周波数を一定に維持する第2の制御電圧VC2を生成する制御電圧変換部30と、を含むパルス発生回路1。

(もっと読む)

データ受信装置およびマイクロコンピュータ

【課題】CR発振回路に温度変化や経年変化が生じても正確な周波数を持つクロック信号を生成する。

【解決手段】CR発振器12の温度を示すA/D変換値とCR発振回路8の逓倍数を決める逓倍数設定値FMULRとを対応付けてEEPROM3に記憶し、A/D変換値(検出温度T)に応じた逓倍数設定値FMULRを読み出してCR発振回路8のレジスタに設定する。通信回路7が同期信号を受信するごとにクロック信号CLKを計数して1ビット長を計測し、その計数値XAと正規の1ビット時間に対する基準周期に基づく基準計数値XBとに基づいて逓倍数設定値FMULRを補正し、補正後の逓倍数設定値FMULRを検出温度Tに対応させてEEPROM3に書き込む。

(もっと読む)

発振装置、その調整方法及びメモリ装置

【課題】簡単に発振信号の周期のばらつきを防止することができる発振装置、その調整方法及びメモリ装置を提供することを課題とする。

【解決手段】イネーブル信号に応じて発振信号を生成する発振器(105)と、前記発振信号の発振数をカウントし、第1の信号で指定された発振数でリセットするかしないかの選択を行うことができるカウンタ(106)と、前記カウントされた発振数及びリファレンス数を比較する比較器(107)とを有することを特徴とする発振装置が提供される。

(もっと読む)

発振器

【課題】発振周波数変更機能を備えた発振器において、不揮発性メモリからデータを読み出す際に発振周波数が変更されることなく安定的に読み出すことができる。

【解決手段】LSIの外部に設けられた不揮発性メモリ15に、発振回路13から発振されるクロック信号の周波数を変更するための周波数設定値が記憶されており、その周波数設定値が、発振回路13から発振される初期設定された周波数のクロック信号によって読み出されると、ダミーレジスタ11に格納される。不揮発性メモリ15からデータが全て読み出されてロード動作完了信号が出力されると、ダミーレジスタ11から記憶レジスタ12へ周波数設定値が格納され、発振回路13の発振周波数が周波数設定値とされる。

(もっと読む)

PLL回路を備えた半導体集積回路

【課題】製造条件によるデバイス特性のバラツキや使用温度、電源電圧などの使用環境によるデバイス特性のバラツキがある場合でも、未然にVCO6の発振停止を防止すると共に、安定的に起動を行うことができるPLL回路を備えた半導体集積回路を提供する。

【解決手段】PLL回路2の過渡応答時間とデバイス及び使用環境に応じたチャージポンプ4の電流値を、事前にメモリ10に保存しておき、マイコン9からの制御信号ICPctlに基き、チャージポンプ4は、PLL回路2起動時から発振安定時までの過渡応答期間中は、電流値をメモリ10の設定情報に従って低減させる。

(もっと読む)

半導体装置

【課題】第1の制御クロックに基づいて第1の制御を行う第1の制御部と、第2の制御クロックに基づいて第2の制御を行う第2の制御部とを有する半導体装置に関し、チップサイズの小型化が可能な半導体装置を提供することを目的とする。

【解決手段】本発明は、第1の制御クロックに基づいて第1の制御を行う第1の制御部と、第2の制御クロックに基づいて第2の制御を行う第2の制御部とを有する半導体装置であって、第1のクロックを生成する第1のクロック生成部と、第2のクロックを生成する第2のクロック生成部と、第1のクロック又は前記第2のクロックのいずれかを選択し、出力する選択部と、クロック選択部で選択されたクロックから第1の制御クロックを生成し、第1の制御部に供給するとともに、クロック選択部で選択されたクロックから第2の制御クロックを生成し、第2の制御部に供給する制御クロック生成部とを有することを特徴とする。

(もっと読む)

デューティー・サイクル測定装置、オンチップ・システム及び方法(デューティー・サイクル測定装置及び方法)

【課題】マイクロプロセッサ或いはオンチップ・システムなどの集積回路装置において受験信号のデューティー・サイクルを測定するメカニズムを提供する。

【解決手段】該メカニズムは、該デューティー・サイクルに比例する、ありふれた研究室装置或いは製造装置を用いて測定され得る周波数を生成する。該メカニズムは、必要な面積が非常に僅かで、使用されていないときには給電を止めることのできる標準的な相補型金属酸化膜半導体プロセスで簡単な回路を用いて具体化され得る。該メカニズムは、例えば、ロー・パス・フィルタと、校正基準電圧信号を供給するための分周器と、VF変換器と、周波数信号出力を、該信号の周波数が所定範囲内にあるように割るための分周器と、出力ドライバと出力パッドとを含み得る。該周波数出力信号から、オフチップ装置を用いて受験信号のデューティー・サイクルを計算することができる。

(もっと読む)

ワンショットパルス発生回路

【課題】 状況に応じて直ちにパルス幅を変えることができるワンショットパルス発生回路を提供する。

【解決手段】 レジスタ25にパルス信号OUTの立ち上がりのタイミングを設定し、レジスタ21,22には、このパルス信号OUTのそれぞれ異なる立ち下がりのタイミングを設定する。更に、レジスタ23には、レジスタ21,22のいずれを選択するかの選択信号を設定する。これにより、例えば、エンジン制御部40等の外部から与えられる状況が急変したときに、レジスタ23の選択信号を変更することで、出力部のレジスタ29〜31から出力されるパルス信号OUTのパルス幅を直ちに変えることができる。

(もっと読む)

クロック信号を生成する方法

本発明は、第1クロック信号(SFo)を使用して、受信信号(RS)内の基準イベント(EVT1)の特性を測定する段階と、前記第1クロック信号を使用して、受信信号(RS)内の第2イベント(EVT2、D0)の特性の変動を判定する段階と、前記第2イベントの特性の変動によって、前記測定値(NEVT1、NFC)を訂正する段階と、前記第1クロック信号を使用して、前記訂正する測定値(NFC)によって第2クロック信号(SFC)を生成する段階と、を具備するクロック信号を生成する方法に関する。非接触チップの送受信回路への応用。  (もっと読む)

(もっと読む)

1 - 20 / 25

[ Back to top ]