Fターム[5J049AA15]の内容

Fターム[5J049AA15]に分類される特許

1 - 17 / 17

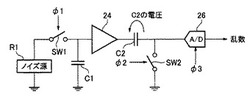

物理乱数生成装置及び物理乱数生成回路

【課題】方法で真正な乱数を簡単に取り出すことができる物理乱数生成装置及び物理乱数生成回路を提供する。

【解決手段】出力レベルがランダムに変動するノイズ源からの信号を所定の周期でサンプリングしてディジタル値に変換するA/D変換手段と、前記A/D変換手段によってサンプリングされたディジタル値を所定期間にわたり保持するディジタル値保持手段と、前記ディジタル値保持手段に保持されている値と、その後にサンプリングされたディジタル値との差を算出する演算手段と、前記演算手段による演算結果を乱数値として出力する出力手段とを具備する。ノイズ源から出力される信号をあるタイミングでサンプリングしたときに、その値から前回サンプリングされた値を差し引いた値が乱数値として出力され、真正度の高い乱数が得られる。

(もっと読む)

ノイズ低減のためのカオス的広帯域周波数変調器

【課題】コンピュータデバイスが他のコンピュータデバイスに及ぼす電磁波干渉(EMI)及び無線周波数干渉(RFI)を低減させる。

【解決手段】装置及び方法は、カオス的広帯域周波数変調を利用して、コンピュータシステムにおける電磁波干渉(EMI)及び無線周波数干渉(RFI)を低減する。カオスノイズ変調器は、非変調基準信号に応じて制御電圧を生成するマスターセルと、ランダムノイズ信号を生成するカオス信号生成器を有し、マスターセルと連結され制御電圧に応じて変調出力信号を生成するスレーブセルとを備える。

(もっと読む)

乱数生成装置

【課題】トラップを利用したランダムノイズ生成素子を用いても、使用回数や使用頻度に関わらず、乱数生成に必要なノイズ信号を初期状態と変わらない状態に保つ。

【解決手段】電圧供給回路20と、半導体基板上に形成されたソース、ドレイン領域と、ソースとドレイン間のチャネルとなるトンネル絶縁膜と、トンネル絶縁膜上の電圧供給回路からの電圧が印加されるゲート電極と、トンネル絶縁膜とゲート電極との間に設けられた電荷トラップ部とを有し、電荷トラップ部に捕獲された電荷に基づいてソースとドレイン間に流れるドレイン電流にランダムノイズが生成されるランダムノイズ生成素子10と、ランダムノイズ生成素子から生成されるランダムノイズを乱数に変換し出力する乱数変換回路30と、乱数変換回路から出力される乱数を検定する検定回路50と、電荷トラップ部内の電荷を半導体基板に引き抜き電荷トラップ部を初期化する初期化回路70とを備えている。

(もっと読む)

乱数生成装置

【課題】良質な乱数を高速に発生させることができる高性能の乱数生成装置を提供することを可能にする。

【解決手段】振幅26mV以上のパルス波形電圧を発生するパルス電圧発生器70と、半導体基板上に離間して形成されたソースおよびドレイン領域と、ソース領域とドレイン領域との間のチャネル領域となる半導体基板上に形成されたトンネル絶縁膜と、トンネル絶縁膜上に形成されパルス電圧発生器からのパルス電圧が印加されるゲート電極とを有し、ソース領域とドレイン領域間に流れる電流にランダムノイズが含まれるランダムノイズ生成素子10aと、ランダムノイズ生成素子から発生されるランダムノイズの大きさに基づいて乱数信号を生成する乱数生成部30と、を備える。

(もっと読む)

パルス生成器、およびそれを備えた送信機

【課題】低消費電力で、複数の周波数帯域に対応するパルスを生成するパルス生成器を提供する。

【解決手段】本発明に係るパルス生成器10は、遅延部3から出力された遅延信号DL0〜DL15に基づいて基準パルスSQA1〜SQA7と基準パルスSQB1〜SQB5とをそれぞれ生成し、基準パルスSQA1〜SQA7を列とした送信パルスAと基準パルスSQB1〜SQB5を列とした送信パルスBをそれぞれ生成する。基準パルスSQA,SQBは、パルス幅がそれぞれ異なるため、送信パルスA,Bの時間幅もそれぞれ異なり、複数の周波数帯域に対応するパルスを生成することができる。

(もっと読む)

半導体集積回路装置

【課題】乱数種の乱数性を向上させることにより、IDタグにおける固体認識率を向上させる。

【解決手段】乱数種を取り込むクロック信号CLK2を生成する際、抵抗19に電流が流れる際に発生する熱雑音を増幅器20,21によって増幅し、参照電圧VREF1,VREF2としてコンパレータ22,23に出力する。コンパレータ22,23は、参照電圧VREF2,VREF1と静電容量素子28の接続部(ノードa)の電圧VCとを比較し、その比較結果をそれぞれ出力する。フリップフロップ24は、コンパレータ22,23からの出力信号によってクロック信号を出力する。参照電圧VREF1,VREF2は、熱雑音によってノイズを含んでいるので電圧レベルが大きく揺れており、フリップフロップ24から出力されるクロック信号CLK2の周期を変動させることができる。

(もっと読む)

物理乱数発生器および物理乱数発生装置および乱数検証方法

【課題】高品位の物理乱数を高速に生成できる安価で信頼性の高い物理乱数発生器を提供する。

【解決手段】2組のノイズ源1a、1bと、これらノイズ源より発生するノイズの直流分を除去して増幅する第1増幅回路2と第2増幅回路3と、第1増幅回路2と第2増幅回路3の出力電圧を比較して0または1を出力する比較回路4と、比較回路4の出力を基準クロックに同期して保持し、物理乱数を得るフリップ・フロップ5と、比較回路4の一方の入力に接続され、比較回路4のオフセット電圧を設定するオフセット電圧回路7と、オフセット電圧回路7を制御する一様化フィードバック回路6とで構成される。

(もっと読む)

乱数発生器

【課題】アナログ入力信号から導き出され、かつ高いエントロピを有するディジタル出力信号を生成できる乱数発生器を提供する。

【解決手段】シグマデルタ変調器を備え、このシグマデルタ変調器は、第1電圧範囲全体にわたってノイズに起因して変化するアナログ入力信号を受け取り、この信号に調節信号を加算して加算出力信号を形成し、この信号を受け取って、その信号に応じてフィルタ処理済み出力信号を生成し、この信号を受け取り、この信号を量子化器しきい値と比較し、比較結果に応じてディジタル出力信号の2つの所定の電圧レベルの一方を選択することによってディジタル出力信号を形成し、ディジタル出力信号を受け取り、任意の所与の瞬時においてこの信号に応じて調節信号を生成することにより、加算出力信号の振幅と量子化器しきい値との間の絶対差が第1電圧範囲よりも小さくなるようにする。

(もっと読む)

パルス信号生成回路

【課題】パルス信号生成回路において、スペクトラム拡散変調とパルス幅変調とを共に実現する。

【解決手段】擬似乱数発生回路10から出力されたデジタルランダム信号S0をD/A変換回路20によりアナログランダム電圧信号S1に変換する。加算器30は、信号S1と中心周波数設定電圧S2とを加算し周波数制御電圧信号S3を出力する。鋸波生成回路40は、信号S3に対応して周波数が変動する鋸波電圧を生成する。コンパレータ50は、鋸波電圧S4とデューテイ比設定電圧S5との大小に応じたパルス信号S6を出力する。このパルス信号S6は、デューテイ比設定電圧に対応するデューテイ比を有し、周波数制御電圧信号S3に対応して周波数が変動する。

(もっと読む)

確率的演算素子及びこれを用いた確率的演算装置

【課題】ノイズを含む信号間の差分絶対値演算を実行可能な確率的演算素子の提供を目的とする。

【解決手段】ノイズを含む信号源3a,3bの出力を比較器5に入力し、比較器5のHigh/Low出力の変化回数を電圧変動測定器10で数えることで、信号電圧1の平均電圧と信号電圧2の平均電圧の差分絶対値に対応する値を得る。

(もっと読む)

半導体集積回路及び擬似乱数発生回路

【課題】ウェハーレベルでのバーンインテストに対応可能であって、テスト用の回路の設計容易化が見込める半導体集積回路を提供することを目的とする。

【解決手段】バーンインテストモードにおいて、PLL回路1の出力クロックを、直接或いは反転回路等のリファレンス入力信号出力回路2を介してPLL回路1のリファレンス入力端子に供給するとともに、セレクタ3を介してスキャンチェーンを構成する初段のフリップフロップFFにデータ入力信号として供給することにより、初段のフリップフロップFFから擬似的な乱数を発生させ、回路全体に適切なストレスを印加する。

(もっと読む)

信号発生装置

【課題】信号発生装置の複数のチャンネルに供給されるクロックを停止することなく、チャンネル間の出力信号位相を制御する。

【解決手段】第1及び第2チャンネル20及び22は、クロック位相シフト回路26及び28と、メモリ、並直列変換回路、DACを有する信号発生ブロック10及び12を具えている。位相比較回路24は、信号発生ブロック10及び12内のメモリから波形データを読み出すための分周クロックを受けて、これらの位相を比較し、位相差信号を生成する。CPUは、この位相差信号を用いてクロック位相シフト回路26及び28を制御し、信号発生ブロック10及び12に供給するクロックの位相シフトを行うことで、第1及び第2チャンネル20及び22の出力信号の位相関係を所望の関係に制御する。

(もっと読む)

クロック生成方法とクロック生成回路

【課題】 簡単な構成で効果的に均一なスペクトラム拡散を実現したクロック生成方法とクロック生成回路を提供する。

【解決手段】 PLL回路と変調器とを用いて、上記PLL回路における帰還用分周器の分周比を上記変調器の変調プロファイルを基に生成された変調データに従って変化させて周波数変調を施してスペクトラム拡散を行う際に、上記変調プロファイルの折り返しポイントを移動させて周波数頻度を分散させて上記拡散スペクトラムを再拡散させる。PLL回路と変調器からなり、上記変調器に多重変調プロファイル生成回路を設けて、変調プロファイルの折り返しポイントを移動させ、周波数頻度を分散させることにより拡散スペクトラムを再拡散させる。

(もっと読む)

乱数生成回路及び半導体集積回路

【課題】 小型化を実現しつつ、高速化を実現することができる乱数生成回路及び半導体集積回路を提供する。

【解決手段】 乱数生成回路1において、ノイズ信号を発生するノイズ発生源2と、ノイズ信号の周波数帯域の一部を抽出するフィルタ3と、ノイズ信号の周波数帯域の一部と参照信号との間の信号差を増幅した乱数信号を生成するコンパレータ4とを備える。半導体集積回路は基板上に乱数生成回路1を搭載する。

(もっと読む)

確率的パルス発生器と差分絶対値演算器及びこれを用いたマンハッタン距離演算装置

本発明の確率的パルス発生器(1)は、ランダムに変動する変動信号(VC)を発生する変動信号発生器(61)と、一方の入力信号と他方の入力信号との大小に応じてHighまたはLowの2値信号(Vout)を出力する比較器(3)とを備え、比較器(3)に変動信号発生器(61)から変動信号(VC)が前記一方の入力信号として入力され、それにより、比較器(3)が前記他方の入力信号(VS)の大きさに対応した数のパルスを確率的に出力する。  (もっと読む)

(もっと読む)

巡回符号回路

【課題】同時に複数のビットを処理する必要があるようなアプリケーションに対しても周波数を増大させる必要のない巡回符号回路を提供する。

【解決手段】本発明の巡回符号回路では、加算数Aと最大次数Bとを用いて表現される生成多項式により表される巡回符号を同時にCビットずつ出力する為に、A*(2B−1−B)で示される個数の排他的論理和回路(XOR)群(11−21)と、初期データ及び排他的論理和回路の出力とを入力して、アドレス信号により選択されたCビットのデータを出力するバレルシフタ23と、アドレス信号を出力するアドレス発生器22とを備えている。

(もっと読む)

PN符号発生器、GOLD符号発生器、PN符号逆拡散器、PN符号発生方法、GOLD符号発生方法、PN符号逆拡散方法、及びコンピュータプログラム

次数が4の線形帰還シフトレジスタの各フリップフロップに与えられる15個のシフトコードパターンを4分割して得られる4個の連続した位相のシフトコードパターンをコードメモリ(11)に記憶させる。また、発生させるPN符号(PN)の位相を4つずらすためのマスクコードパターンを、コードマスクメモリ(12)に記憶させる。そして、コードメモリ(11)から出力したシフトコードパターンと、コードマスクメモリ(12)から出力したマスクコードパターンとを用いて、位相シフト回路(13)で論理演算を行い、符号長が15のPN符号(PN)を任意の位相から発生させるようにする。  (もっと読む)

(もっと読む)

1 - 17 / 17

[ Back to top ]