Fターム[5J055BX44]の内容

電子的スイッチ (55,123) | スイッチの種類、機能 (3,337) | 閾値スイッチ (108)

Fターム[5J055BX44]の下位に属するFターム

複数の閾値を有するもの (37)

Fターム[5J055BX44]に分類される特許

41 - 60 / 71

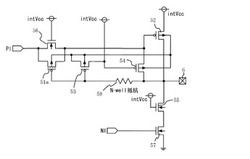

半導体装置の入出力回路

【課題】 pull−down抵抗が端子に設けられている場合においても、

AC特性を改善することを目的とする。

【解決手段】 半導体内部電源電圧よりも高電圧の外部信号線に接続される出力端子部6と、フローティングNウェルを有し複数のPチャネル型トランジスタ52、53、54とアナログスイッチ51aにより構成され半導体内部信号を外部へ出力するハイ側出力回路部と、複数のNチャネル型トランジスタ55、57が直列に接続され半導体内部信号を外部へ出力するロー側出力回路部とを備えた半導体装置の入出力回路において、前記アナログスイッチを構成するPチャネル型トランジスタ51aの閾値電圧を他のトランジスタの閾値電圧より低く設定した。

(もっと読む)

温度検出回路

【課題】温度検出を行う第2及び第3の各電界効果トランジスタに電源供給を行う第1の電界効果トランジスタのソース電圧をZTC点に設定することにより、低電圧動作が可能な温度検出回路を得る。

【解決手段】温度検出を行う各電界効果トランジスタM2,M3に電源供給を行う電界効果トランジスタM1におけるソース電圧を、温度上昇に伴ってしきい値電圧Vthが低下してドレイン−ソース間電流が上昇する効果と、移動度が低下してドレイン−ソース間電流が低下する効果が相殺されるZTC点に設定するようにした。

(もっと読む)

出力回路

【課題】半導体集積回路装置に搭載される出力回路に関し、出力バッファのトランジスタのスレッショルド電圧のばらつきによる外部出力信号のスルーレートのばらつきを抑制できるようにする。

【解決手段】プリバッファ58は、内部出力ノード14とPMOSトランジスタ10のドレインとの間に制御信号電圧変化調整回路59を接続する構成とする。制御信号電圧変化調整回路59は、出力バッファ8のNMOSトランジスタ15のスレッショルド電圧のばらつきによる外部出力信号SC1のスルーレートのばらつきを抑制するように制御信号SB1の電圧変化を調整する。

(もっと読む)

パワーオン電源電位検知回路

【課題】 p型MOSトランジスタのしきい値の温度依存性及び、p型MOSトランジスタのしきい値のばらつきを低減するパワーオン電源電位検知回路を提供する。

【解決手段】 電源電位Vddと電源電位Vddより低い低電位Vssとの間に直列接続されたダイオードD1、第1の抵抗R1及び第2の抵抗R2と、第1の抵抗R1と第2の抵抗R2の接続点の電位VG1をゲートに入力し、ソースを第3の抵抗R3を介して電源電位Vddに接続し、ドレインを第4の抵抗R4を介して低電位Vssに接続したp型MOSトランジスタQ1とを備える。

(もっと読む)

電流スイッチ

【課題】 性能を落とすことなく低電圧化が可能な電流スイッチを提供することを目的にする。

【解決手段】 正電源と負電源の間に基準電流源とバイアス回路を接続し、この接続点を第1のエミッタフォロアに入力して、この第1のエミッタフォロアが、差動入力信号が入力される差動対回路を駆動し、差動対回路の出力を第2のエミッタフォロアに入力して、この第2のエミッタフォロアの出力を電流出力部に入力するようにした。また、これらの回路を構成するトランジスタのエミッタ面積と抵抗の比を所定の比率に調整するようにした。出力部のエミッタ結合対と負電源の間のトランジスタを省略できるので、低電圧化することができる。

(もっと読む)

半導体集積回路及びその受信システム

【課題】 イコライザによるイコライジングのレベル設定を変える必要がなく、また、キャパシタによる面積の増大を解消し微細化に適した半導体集積回路を提供する。

【解決手段】 伝送されてきた信号をイコライズする機能を有する半導体集積回路において、受信した信号を差動増幅するバッファ101と、バッファ101から出力された信号を受信し、増幅するバッファ102と、バッファ101から出力された信号を受信し、バッファ102よりも高いコモンモード電圧で増幅するバッファ103と、バッファ101から出力された信号を受信し、バッファ102よりも低いコモンモード電圧で増幅するバッファ104と、信号の状態からバッファ102、103、104の出力信号の内、少なくとも一つの出力信号を選び出し、選び出された出力信号をサンプリングするサンプラー105を備えることを特徴としている。

(もっと読む)

低電圧VCCを供給される差動トランジスタ対電流スイッチ

本発明は、トランジスタの差動対を用い、かつ低供給電圧Vcc下で動作できる電流スイッチに関する。本発明によれば、共にカスケードされたそれぞれ2つのトランジスタの2つの差動対(T1、T1b;T2、T2b)を含む電流スイッチが提供されるが、第2の対(T2、T2b)は、入力部(E、Eb)の状態によって反転する相補電流出力部(H、Hb)を有する。第1の対(T1、T1b)は、電流源を通して接地(GND)され、値Ioの電流を供給し、電圧Vbiasのバイアスをかけられるトランジスタ(Ts1)を含み、N.Vbe+Vbiasに等しい電圧を供給されるが、ここで、Nは整数(好ましくは1に等しい)であり、Vbeは、トランジスタ(Ts1)のベース−エミッタ電圧である。第2の対(T2、T2b)は、抵抗器(R2)を通して直接接地される。本発明は、サンプルホールド回路、マルチプレクサ、高速低電圧論理回路等のオン−オフ制御に適用することができる。 (もっと読む)

半導体集積回路装置

【課題】

第1の電源系と第2の電源系の間で信号の伝送を行う信号線の電圧上昇を抑制することが可能となり、非常に高い異常電圧が発生した場合においても、回路の破壊を抑止することが可能な半導体集積回路を提供する。

【解決手段】

第1の電源線に接続された第1の回路111を有する第1の電源系11と、第2の電源線に接続された第2の回路121を有する第2の電源系12と、第1の回路111と第2の回路121との間に接続され、第1の回路111と第2の回路121との間で信号を伝送する信号線14と、信号線14とは異なり、第1の電源系11と第2の電源系12の間に異常電圧が発生したときに異常電流が流れる放電経路13と、異常電圧が発生したときに、異常電流が流れている放電経路13内の二点間の電位差に基づいて動作し、信号線14の電圧上昇を抑制する保護回路123と、を備えた半導体集積回路装置

(もっと読む)

半導体回路

【課題】 簡単なバルク電位制御の回路構成で回路面積の増大を防ぐことができ、MOSトランジスタのしきい値電圧の絶対値を調整することができると共にしきい値電圧のばらつき幅を低減させることができ、安定した低電圧動作を行うこと。

【解決手段】 しきい値電圧を制御したいトランジスタT2のバルク端子bを、同しきい値電圧を有し、ゲート端子gとドレイン端子dを短絡したダイオード接続型のトランジスタT1のゲート端子gと接続することで、しきい値電圧に応じたバルク電位を発生させ、しきい値の絶対値及びばらつき幅を抑制することを可能とする。

(もっと読む)

温度保護回路、半導体集積回路装置、電源装置、電気機器

【課題】本発明は、過熱監視対象の近傍に設けられても、高精度の温度保護動作を行うことが可能な温度保護回路を提供することを目的とする。

【解決手段】本発明に係る温度保護回路10は、チップ温度が第1の閾値温度に達したときにイネーブルとされ、第1の閾値温度よりも低い第2の閾値温度を下回ったときにディセーブルとされる信号Aを生成する発熱検出部11と;信号Aが所定の確認期間に亘ってイネーブル状態に維持されたときにイネーブルとされる信号Bを生成するイネーブル制限部12と;信号Bのイネーブルに同期してイネーブルとされ、かつ、少なくとも所定の最短期間については、そのイネーブル状態が維持される温度保護信号Stsdを生成するディセーブル制限部13と;を有して成る構成とされている。

(もっと読む)

電子スイッチ、および電子スイッチの動作方法

【課題】 電子スイッチの強電波による誤動作を抑制できるようにする。

【解決手段】 比較回路COM21の負入力端子に供給される電圧値が電波非検出で、かつ、遊技球非検出を示す電圧値V1である場合、弁別閾値となる電圧値V41を電波非検出で、かつ、遊技球検出を示す電圧値V2と電波検出を示す電圧値V3との中間電圧値V41hiに切り替え、比較回路COM21の負入力端子に供給される電圧値が電圧値V2である場合、弁別閾値となる電圧値V41を電圧値V1と電圧値V3との中間電圧値V41loに切り替えるようにしたので、電波が検出されると、電子スイッチ21により遊技球31は検出されるものの、カウントするための比較回路COM21の動作が保持されることになる。本発明は、パチンコ遊技台に適用することができる。

(もっと読む)

論理ゲートおよび論理回路

【課題】 サブスレッショルドリーク電流を低減した論理ゲートを提供する。

【解決手段】 ソースに第1の電圧が印加され、ゲートに第1の入力信号が入力され、ドレインから第1の出力信号を出力する第1のトランジスタと、ソースに第1の電圧よりも低い第2の電圧が印加され、ゲートに第2の入力信号が入力され、ドレインから第2の出力信号を出力する第2のトランジスタと、第1のトランジスタおよび第2のトランジスタのドレイン間に接続され、第1のトランジスタと第2のトランジスタを接続または切り離す接続切換部とを有する構成である。

(もっと読む)

論理閾値変換方法及びその装置

【課題】電源電圧の全範囲にわたって論理回路の論理閾値を線形に制御可能にする。

【解決手段】論理閾値制御電圧を論理閾値制御回路に入力させ、前記論理閾値制御回路の出力を論理回路の出力端子に接続させ、前記論理回路の論理閾値を電源電圧の全範囲にわたって変換する。

(もっと読む)

半導体装置

【課題】リーク電流遮断回路を備える半導体装置において、別途データ保持回路の配置領域や記憶手段を設けることなく、そのデータが破壊されるのを防止することができる半導体装置を提供する。

【解決手段】データ保持回路を含む内部回路と、電源側およびグランド側のリーク電流遮断回路とを備える。例えば、グランド側のリーク電流遮断回路は、内部回路を構成するグランド側トランジスタのソースとグランドとの間を電気的に接続状態または遮断状態とするスイッチと、グランド側トランジスタのソースの電位がグランドの電位と略等しいことを検出するとスイッチを遮断状態とし、グランド側トランジスタのソースの電位がデータ保持回路にデータを保持するために必要なローレベルの最高電位よりも低い所定の電位まで上昇したことを検出するとスイッチを接続状態とする制御回路とを備える。

(もっと読む)

トレラント入力回路

【課題】 入力回路のしきい値を調整することなく、製造ばらつきに関わらず安定して動作するトレラント入力回路を提供する。

【解決手段】 入力パッド1と入力回路2との間にNチャネルMOSトランジスタにてなる降圧素子Tr3を介在させ、降圧素子Tr3のゲートに入力回路の電源VDDを供給して、入力パッド1に入力される高電圧信号を、電源VDD電圧以下に降圧して入力回路2に供給するトレラント入力回路であって、入力パッド1に高電圧信号が入力されたとき、降圧素子Tr3のバックゲート電圧を上昇させるバックゲート電圧制御回路を備えた。

(もっと読む)

低振幅差動出力回路及びシリアル伝送インターフェース

【課題】 CMOS回路を用いた差動出力回路において、電源・温度・プロセス等の変動による影響により、不所望の大きさのVCM変動が発生している。

【解決手段】 本発明による低振幅差動出力回路は、相互に相補である正相駆動信号MINTと逆相駆動信号MINBとによる差動信号であるメインバッファ駆動信号MINT/MINBを出力するプレバッファ回路1と、プレバッファ1に接続され、メインバッファ駆動信号MINT/MINBに応答して差動出力信号OUTT/OUTBを出力するメインバッファ回路2とを備え、正相駆動信号MINTと逆相駆動信号MINBは、第1の電位VDDと第2の電位GNDとの電位差を振幅とし、正相駆動信号MINBと逆相駆動信号MINBは、前記第1の電位と前記第2の電位との中間の電位と、前記第1の電位との間の電位で同電位となる。

(もっと読む)

レベルシフト回路、それを用いた電気光学装置、および、電子機器

【課題】 論理入力信号やノイズのレベルに適切に対応することが可能なレベルシフト回路を提供する。

【解決手段】 レベルシフト回路において、一端にて論理入力信号が入力される容量素子と、容量素子の他端に接続された入力に対して第1の論理反転レベルを有する第1の論理反転回路および第2の論理反転レベルを有する第2の論理反転回路を含み、第1と第2の論理反転回路の出力極性が一致することで第2の論理振幅を有する論理出力信号を反転する論理出力回路と、容量素子の他端に入力の一端と出力が接続され、前記第1の論理反転レベルよりも低く第2の論理反転レベルよりも高い第3の論理反転レベルを有する第3の論理反転回路と、第1および第2の論理反転回路と第2の論理振幅に対応する電源とを接続し、前記第1の論理反転レベルおよび前記第2の論理反転レベルを設定する論理反転レベル設定手段と、を備える。

(もっと読む)

MOS型トランジスタを備えた半導体装置

【課題】低電圧で高速高精度な動作を行なうことができるMOS型トランジスタを備える半導体装置を提供する。

【解決手段】本発明の半導体装置は、ゲート入力部12およびボディ入力部14を有する少なくとも1つのMOS型トランジスタ10と、ゲート入力部12に第1制御信号(ゲート電圧Vg(t))を送出する第1出力部22、およびボディ入力部14に第2制御信号(ボディ電圧Vb(t))を送出する第2出力部24を有する制御回路20とを備える。制御回路20は、ゲート電圧Vg(t)の印加によってMOS型トランジスタ10をON状態にした後、MOS型トランジスタ10がON状態にある間にMOS型トランジスタ10の閾値を上昇させるように、ボディ電圧Vb(t)のレベルを変化させる。

(もっと読む)

半導体集積回路

【課題】回路の動作スピードを保ちつつリーク電流を削減でき、更に論理ゲートの面積増大を抑えることができる半導体集積回路を提供する。

【解決手段】各論理ゲート内に含まれる同一導電型の複数のトランジスタが共通のしきい値特性を有する。例えば、同一導電型のトランジスタには、同程度のしきい値を有する同一種類のトランジスタを用いる。これにより、これらのトランジスタを同一活性領域に近接して形成することが可能になるため、論理ゲートの面積を小さくすることができる。また、図1に示す半導体集積回路は、p型MOSトランジスタまたはn型トランジスタの一方に高しきい値特性のトランジスタを用いた論理ゲート(G1,G2)を有するため、回路を伝播する2相の信号(立ち上がりおよび立ち下り)のうちの何れか一方の信号経路に高しきい値特性のトランジスタを選択的に挿入することが可能になる。

(もっと読む)

複数のスイッチのオンオフ検出回路

【課題】簡単な構造のスイッチを使用して、複数のスイッチのオンオフをひとつの入力端子の安価なマイコンで検出する。全てのスイッチのオンオフを独立して検出する。

【解決手段】複数のスイッチのオンオフ検出回路は、複数のスイッチ1と、各々のスイッチ1のオンオフを”High”と”Low”の信号に変換する変換回路3と、変換回路3の出力に接続されて、変換回路3から出力される”High”と”Low”をアナログ信号に変換するD/Aコンバータ4と、このD/Aコンバータ4から出力されるアナログ信号を単一の入力端子6に入力するマイコン2とを備える。マイコン2は、入力されるアナログ信号をデジタル信号に変換するA/Dコンバータ5を備え、入力されるアナログ信号をA/Dコンバータ5でデジタル信号に変換し、デジタル信号から各々のスイッチ1のオンオフを検出する。

(もっと読む)

41 - 60 / 71

[ Back to top ]