Fターム[5J055BX44]の内容

電子的スイッチ (55,123) | スイッチの種類、機能 (3,337) | 閾値スイッチ (108)

Fターム[5J055BX44]の下位に属するFターム

複数の閾値を有するもの (37)

Fターム[5J055BX44]に分類される特許

61 - 71 / 71

ドライバ回路、シフトレジスタ及び液晶駆動回路

【課題】 表示部のトランジスタの動作速度を増加させ、かつこのトランジスタを駆動するa−Si TFT用の動作寿命が従来に比較して長いドライバ回路,シフトレジスタ、またこのシフトレジスタを用いた液晶駆動回路を提供する。

【解決手段】 本発明のドライバ回路は、しきい値電圧を制御するバックゲートが設けられており、ゲートに印加された電圧に対応して、ドレインから入力される電圧をソースから出力信号として出力するトランジスタが設けられている。

(もっと読む)

デューティ比補正回路

【課題】パルス発生器等から供給されるパルスのデューティ比を補正する回路において、容量を小量化して応答性を向上する。半導体集積回路のチップ面積を小さくする。

【解決手段】PLLoutがデューティ比50%未満だとクロックパルスのデューティ比は50%を上回る。AVR>Vdd/2となってコンパレータ7の出力CoutがHとなり第2のスイッチング増幅回路8がオンする。コンデンサC2によりバイアス信号BIASが高くなる。FET21の電流制御により出力点Q1の信号のパルス幅が長くなる。クロックパルスのデューティ比が低く補正されて50%に近付く。コンデンサ2により積分した信号はFET21,24へのバイアス信号BIASとなるから小電流で済む。コンデンサC2の容量を小さくできる。チップ面積を小さくできる。応答性が向上する。

(もっと読む)

出力バッファ回路

【課題】高スルーレートでスルーレート変動の少ない出力バッファ回路を実現する。

【解決手段】NMOSトランジスタM3をONすることで容量C1と容量C2との容量比で出力トランジスタであるPMOSトランジスタM1のゲート電圧をしきい値電圧以下に低下させ、PMOSトランジスタM1をONさせ、同時に、電流源I1により最終的にPMOSトランジスタM1のゲート電圧を0Vにし、さらに、PMOSトランジスタM4をONすることで容量C3と容量C4の容量比で出力トランジスタであるNMOSトランジスタM2のゲート電圧をしきい値電圧以下に低下させ、NMOSトランジスタM2をONさせ、同時に電流源I2により最終的にNMOSトランジスタM2のゲート電圧を電源電圧レベルにする構成とし、出力トランジスタのゲート電圧を容量分圧制御で行う。

(もっと読む)

波形整形回路

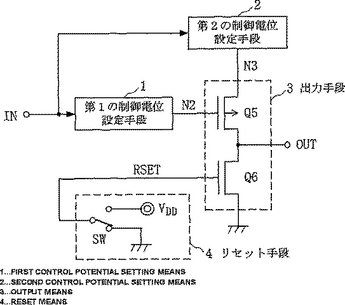

第1の制御電位設定手段(1)は入力信号(IN)が論理閾値の近傍に達したときに第2の制御電位(N3)との大小関係が逆転する第1の制御電位(N2)を生成する。第2の制御電位設定手段(2)は、入力信号(IN)の変化に応じて入力信号(IN)と同方向に変化する第2の制御電位(N3)を生成する。出力手段(3)は、トランジスタ(Q5,Q6)からなり、第1の制御電位(N2)と第2の制御電位(N3)とリセット信号(RSET)とに基づいて所定の電位の出力信号(OUT)を生成する。リセット手段(4)は、波形整形回路の動作時にトランジスタ(Q6)をオフにする。  (もっと読む)

(もっと読む)

シフトレジスタ及びその駆動方法

本発明は、インバータの入力部をインバータの閾値電位にし、インバータの入力部に容量手段を介してCK信号を入力することで、CK信号は増幅され、その増幅されたCK信号をシフトレジスタに用いる。つまり、インバータの閾値電位を取得することで、トランジスタの特性ばらつきに殆ど影響しないシフトレジスタを提供することができる。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】電源ノイズ発生の主要因のひとつである、内部ロジックでのゲートの出力変化による電源電流変動を低減すること。

【解決手段】ゲート回路105−1の出力変化を受けてゲート回路106−1、2の出力が変化するとき、ゲート回路106−1とゲート回路106−2ではスレッショルド電圧が異なるため、出力変化が発生するタイミングが異り、また、ゲート回路106−1、2の出力変化を受けてゲート回路107−1〜4の出力が変化するとき、ゲート回路107−1、3とゲート回路107−2、4ではスレッショルド電圧が異なるため、出力変化が発生するタイミングが異なることにより、電源電流の変化は分散し、各電源ラインに発生する電源電流のピークが低減され、電源ノイズを抑制することができる。

(もっと読む)

電流駆動型D/Aコンバータおよびそのバイアス回路

【課題】 電流スイッチトランジスタの制御電圧によって生じるノイズをより小さくし、また、電流スイッチがオフする際に生じていたグランドもしくは電源電圧のノイズを低減し、高性能な電流駆動型D/Aコンバータを得る。

【解決手段】 NMOSトランジスタM12P,M12N,M22P,M22N,M32P,M32Nがオフするオフ制御電圧(BIAS3)を、オン制御電圧(BIAS2)に近づけた電圧に設定したことにより、NMOSトランジスタの制御電圧振幅(オン制御電圧−オフ制御電圧)が小さくなり、寄生容量を介した電荷注入によるノイズの発生を低減すると共に、オフする際の寄生容量からグランドもしくは電源への放電電流の流れ込みによるグランド電圧もしくは電源電圧のノイズの発生を低減し、高性能な電流駆動型D/Aコンバータを得ることができる。

(もっと読む)

半導体集積回路

【課題】 低電源圧下でも高速動作し、待機時においてはサブスレッショルドリークを抑制し出力データを保持できる半導体回路装置の提供。

【解決手段】 信号入力端子INに共通に入力端が接続され、互いに等しい論理構成の第1及び第2の伝送系1、2を備え、第1の伝送系への入力値がロウレベルのときにオフとなるトランジスタが高しきい値とされ、オンとなるトランジスタが低しきい値とされ、第2の伝送系への入力値がハイレベルのときに、オフとなるトランジスタが高しきい値とされ、オンとなる側のトランジスタが低しきい値とされ、第1及び第2の伝送系は、制御信号に基づき、動作状態と待機状態とに制御され、第1及び第2の伝送系の出力INL、INHを受け、動作時は、低しきい値のトランジスタがオン状態となる側の伝送系から、待機時は、出力が不定状態の一方の伝送系からの出力を遮断し、伝送系から出力する出力選択部3を備えている。

(もっと読む)

電圧発生回路、電圧発生装置及びこれを用いた半導体装置、並びにその駆動方法

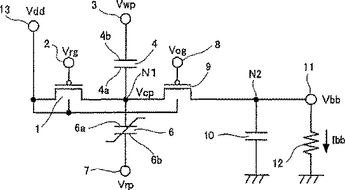

キャパシタ(4)、キャパシタ(4)に直列接続された強誘電体キャパシタ(6)、出力端子(11)、出力端子(11)を接地するキャパシタ(10)、電源電圧供給端子(13)、電源電圧供給端子(13)と2つのキャパシタ(4,6)の接続ノード(N1)とを接続するスイッチ(1)、及び接続ノード(N1)と出力端子(11)とを接続するスイッチ(9)を備え、第1の期間において、スイッチ(1)及び(9)がオフ状態にされた状態で、端子(3)が接地されると共に端子(7)に電源電圧が供給され、第2の期間において、端子(3)に電源電圧が供給され、且つスイッチ(9)がオン状態にされ、第3の期間において、スイッチ(9)がオフ状態にされ、スイッチ(1)がオン状態にされ、且つ端子(7)が接地され、第4の期間において、端子(7)に電源線圧が供給され、前記第1の期間から前記第4の期間までが順に繰り返される、電圧発生回路。  (もっと読む)

(もっと読む)

半導体スイッチの制御装置

【課題】短絡電流と突入電流の識別精度を高めると同時に、短絡電流の発生を検出するまでの判定時間をできるだけ短くすることにより、短絡電流発生時における回路の遮断を早め、半導体素子の電力損失及び温度上昇を最小限とすることのできる半導体スイッチの制御装置を提供する。

【解決手段】直流電源VBと負荷11との間に配置されたMOSFET(T1)を制御することにより負荷11のオン、オフを制御すると共に、短絡電流が流れた際にMOSFET(T1)を保護する機能を具備した半導体スイッチの制御装置において、所定の閾値電圧を設定し、MOSFET(T1)と、直流電源VBとを結ぶ第1の配線に発生する逆起電力E1が閾値電圧よりも大きいか否かを判定する逆起電力検出回路13と、逆起電力検出回路13にて、逆起電力E1の大きさが閾値電圧よりも大きいと判定された際に、MOSFET(T1)をオフとする制御を行う制御回路12とを備える。

(もっと読む)

フェイルセイフな方法で誘導負荷を遮断するための装置および方法

【課題】誘導負荷54の遮断時の誘導電圧の大きさを監視することにより、誘導負荷54をフェイルセイフな方法で遮断する。

【解決手段】入力側の遮断信号20,22または24を受信すれば少なくとも1つのスイッチング素子26により負荷54を遮断する。遮断時に負荷54において誘導電圧Uiが発生するが、この誘導電圧Uiは閾値スイッチ38,40,41,44により制限されている。閾値スイッチ38,40,42,44は、監視回路68,70により監視されており、閾値スイッチ38,40,42,44の1つが故障すれば監視回路68,70において誤差信号が発生する。

(もっと読む)

61 - 71 / 71

[ Back to top ]