Fターム[5J055BX44]の内容

電子的スイッチ (55,123) | スイッチの種類、機能 (3,337) | 閾値スイッチ (108)

Fターム[5J055BX44]の下位に属するFターム

複数の閾値を有するもの (37)

Fターム[5J055BX44]に分類される特許

21 - 40 / 71

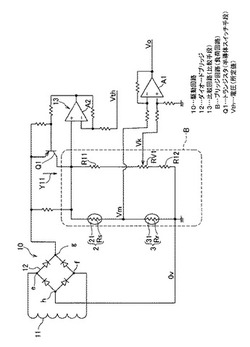

駆動回路

【課題】電力ロスを低減しつつセンサ回路に供給される電圧の安定化を図ることができるセンサ駆動回路を安価に提供する。

【解決手段】ブリッジ回路Bに対して正電圧を供給する方向に導通するトランジスタQ1が、ブリッジ回路Bと図示しない交流電圧源との間に設けられている。ダイオードブリッジ12が、ブリッジ回路Bと図示しない交流電圧源との間に設けられ、ブリッジ回路Bに供給される交流電圧を全波整流する。比較回路13が、ブリッジ回路Bに供給された交流電圧と電圧Vthとを比較して、ブリッジ回路Bに供給される交流電圧の大きさが電圧Vthを越えないようにトランジスタQ1を制御する。

(もっと読む)

受動キーパッドにおける入力範囲間での区別化

【課題】受動キーパッドにおける入力範囲間での区別化をする。

【解決手段】スイッチS1...Snを有する受動回路網100のスイッチ投入を処理する方法および回路。受動回路網100は、スイッチ投入に応じて出力電圧を発生する。この回路は、受動回路網に結合され、出力電圧を基準電圧と比較する比較回路206を備えている。比較回路に結合されたデコーダ212は、出力電圧が所定の範囲内にある場合、スイッチ投入を復号化し、出力電圧が所定の範囲内にない場合、前記スイッチ投入を復号化しない。この回路は、意味あるキープレスの適切な処理ができると同時にうっかりとやったあるいは不注意なキープレスを無視し、それによって電力およびプロセッサ時間を確保する受動回路網キーパッドの入力範囲間で区別する。

(もっと読む)

液晶表示装置

【課題】トランジスタを用いたスイッチ回路を有するデジタル回路において、電源電圧、入力信号の振幅、トランジスタのしきい値電圧の関係に応じて適切に入力信号を補正し、好適な回路動作を可能とする。

【解決手段】電源電位(VDD、VSS)が供給される第1のトランジスタ(32、33)を有するスイッチ回路(31)と、入力信号が印加される入力端(IN)と第1のトランジスタの制御端子(ゲート)との間に接続された補正回路(34、36)とを有し、前記制御端子と入力端との間に接続された容量(C2、C3)と、該容量と前記制御端子との間のノード(N5、N6)と電源電位との間に設けられた、第1のトランジスタと概ね同じしきい値を有するダイオード接続された第2のトランジスタ(35、37)と、第2のトランジスタに直列に接続されたスイッチ(SW2、SW3)とを有するデジタル回路(30)を提供する。

(もっと読む)

双方向スイッチ、及び半導体装置

【課題】オン抵抗を低減することのできる安定したスレッショールド電圧の双方向スイッチ、及び半導体装置を提供すること

【解決手段】本発明にかかる双方向スイッチは、P半導体基板1上に形成され、第1及び第2MOSスイッチM1、M2のドレインとなるNウェル領域2と、Nウェル領域2に設けられた第1トレンチ3内にゲート絶縁膜6を介して形成された第1ゲート電極71aと、Nウェル領域2に第1トレンチ3と離間して設けられた第2トレンチ3内にゲート絶縁膜6を介して形成された第2ゲート電極72aと、第1トレンチ3の側壁においてNウェル領域2の表面にPオフセット領域5を介して形成された第1N+ソース領域9と、第2トレンチ3の側壁においてNウェル領域2の表面にPオフセット領域5を介して形成された第2N+ソース領域10と、を備え、第1トレンチ3と第2トレンチ3との間の領域には、Nウェル領域2が形成されているものである。

(もっと読む)

ノイズ低減回路

【課題】面積効率が高く、応答性およびESD耐性も問題が生じないノイズ低減回路を提供する。

【解決手段】ノイズ低減回路は、電源とグランドとの間に配置された容量素子および抵抗素子を含むデカップリング容量回路と、容量素子と抵抗素子との接続点とグランドもしくは電源との間に接続されたダイオード素子とを備える。電源とグランドとの間の電位差が小さくなった場合、ダイオード素子がオン状態になると、グランドからグランド、または、電源から電源へ向かって電流が流れることで、電源ノイズを瞬時に低減できる。

(もっと読む)

電力供給装置

【課題】配線ショートの発生時とコネクタの接触不良とを区別して回路を保護することが可能な電力供給装置を提供する。

【解決手段】本発明の電力供給装置では、半導体素子T1のドレインの電圧V1が、コンパレータCMP1の同相入力最低電圧を下回る前に半導体素子T1を遮断するので、負荷回路を確実に保護することができる。また、第1判定電圧をL_V1とし、第2判定電圧をV3としたとき、電圧V1が「V1<L_V1」となった場合に、リトライ動作を実行し、「V1<L_V1」となる回数がN1回に達した場合、または、「L_V1<V1<V3」となる回数がN2回に達した場合に、半導体素子T1の遮断状態を保持して負荷回路を保護する。更に、コネクタ11の接触不良に起因して電圧V1が急激に低下した場合には、電圧V1の最低値が安定した値とならず、半導体素子T1の遮断状態は保持されない。

(もっと読む)

入力バッファ回路及びこれを用いた入力装置

【課題】高速低消費電力で閾値制御が可能な入力バッファ回路及び入力装置を提供する。

【解決手段】入力バッファ回路30は、バイアス電圧生成回路100で生成されたバイアス電圧PLV及びこれよりもレベルの高いバイアス電圧NLVにより動作する回路である。この回路30は、バイアス電圧PLVよりも低い第1の電圧が入力されると、オン状態になってその第1の電圧をノードN32から出力するNMOS32と、バイアス電圧NLVよりも高い第2の電圧が入力されると、オン状態になってその第2の電圧をノードN33へ出力するPMOS33と、ノードN32から出力される第1の電圧をラッチして第1の論理の電圧をノードN34へ出力するラッチ回路34と、ノードN33から出力される第2の電圧をラッチして第2の論理の電圧をノードN34へ出力するラッチ回路35とを有している。

(もっと読む)

電気回路、電気光学装置、電子機器、および電気回路の制御方法

【課題】入力信号に必要な振幅を低減する。

【解決手段】電源線L1と出力部N2との間のトランジスタTA1のゲートG1は容量素子C1を介して入力部N1に結合する。電源線L2と出力部N2との間のトランジスタTA2のゲートG2は容量素子C2を介して入力部N1に結合する。トランジスタTB3は、電源線L1からみてゲートG1の方向を順方向として電源線L1とゲートG1との間にダイオード接続される。トランジスタTB4は、ゲートG1からみて電源線L1の方向を順方向として電源線L1とゲートG1との間にダイオード接続される。トランジスタTB3の閾値電圧VT3がトランジスタTA1の閾値電圧VT1を上回り、かつ、トランジスタTB3の閾値電圧VT3とトランジスタTB4の閾値電圧VT4との加算が減少するように、トランジスタTB3およびトランジスタTB4の各々のバックゲートBの電位VBが設定される。

(もっと読む)

ヒートポンプ式給湯装置

【課題】作業ミスによる機器の故障や破損を未然に防止できるヒートポンプ式給湯装置を提供する。

【解決手段】 タンクユニット100とヒートポンプユニット200とを3芯の信号線300で接続し、タンクユニット100に供給された商用交流電源を前記信号線300の第1及び第3の芯線301,301を介してヒートポンプユニット200に供給するとともに、第2及び第3の芯線302,303を介してデータ通信を行い、タンクユニット200に前記信号線の第2及び第3の芯線との間302,303に所定値以上の電圧が印加されたことを検出する検出手段を設けた。

(もっと読む)

直流電源用スイッチ

【課題】オフ状態が長く続いた場合でも開閉制御部を確実に動作させることができる直流電源用スイッチを提供する。

【解決手段】DCスイッチ1は、直流機器102を介して直流電源が接続される入力端子2a,2bと、入力端子2a,2b間に接続されるスイッチ素子3と、スイッチ素子3と並列に接続され、スイッチ素子3のオフ時にスイッチ素子3の両端間に発生する電圧を二次電池6に印加することで二次電池6を充電する第1の電源回路部7と、二次電池6から電源供給を受けて動作し、操作スイッチ4のオン/オフ操作に応じてスイッチ素子3をオン/オフさせる開閉制御部5とを備える。第1の電源回路部7では、スイッチ素子3のオフ時に二次電池6の両端電圧VBが、開閉制御部5の最低動作電圧以上の電圧値に設定された閾値電圧以下になると、スイッチ素子3の両端間に発生する電圧を二次電池6にパルス的に印加して、二次電池6に電荷を蓄電させている。

(もっと読む)

ディスチャージ回路

【課題】ディスチャージトランジスタのゲート電圧が、電源電圧、温度、及びプロセスの変動の影響を受け難く、常に所定の値を保つことができる設計容易なディスチャージ回路を提供する。

【解決手段】一端がディスチャージノードAに接続され、他端がグランドに接続され、ゲートがバイアス電圧Vgに接続されたNMOSトランジスタ11を有するディスチャージ部10と、ゲートにバイアス電圧Vgを供給するバイアス電圧発生部20と、一端とゲートとがディスチャージ部10のNMOSトランジスタのゲートに接続され、他端がディスチャージノードAに接続されたMOSトランジスタ31を有するクランプ部30とを有し、クランプ部30は、ディスチャージ部10のNMOSトランジスタ11のゲートに印加されるバイアス電圧を所定の値にクランプする。

(もっと読む)

パワースイッチIC制御方法

【課題】多電源のうちの所望の電源入力に異常が生じた場合にオフすることができる安価なパワースイッチIC制御方法を提供する。

【解決手段】パワーMOSトランジスタへの電源入力のみ用い、その電源入力以外に制御回路用の電源入力を必要としないので、パワースイッチICの電源ピンの数が増加することがなくICを安価に製造することができ、所望の電源入力をオフすることができる。

(もっと読む)

レベルシフタ

【課題】レベルシフタにおける貫通電流を防止する。

【解決手段】内部ノードn3と接地電位GNDの間に接続されたトランジスタP7,N5によるインバータと、内部ノードn4と接地電位GNDの間に接続されたトランジスタP8,N6によるインバータで構成される保持回路10を設け、これらのインバータをループ状に接続することにより、ノードn1,n2の信号を保持する。これにより、本来相補的である入力信号IN,INBが共にレベル“L”になったときにでも、ノードn1,n2の信号が、その直前のレベルに保持され、トランジスタN3,N4に貫通電流が流れることを防止することができる。

(もっと読む)

電源ノイズ検出機能付き電子制御装置

【課題】正常な電圧印加をノイズとして検出しないようにしつつ、電源ラインにノイズが供給されたことを検出できるようにする。

【解決手段】マイコン8にて分圧回路10の電位V1と平滑化回路9の電位V2の大小を比較し、分圧回路10の電位V1が平滑化回路9の電位V2よりも大きいときには、モータ16の駆動を許可し、平滑化回路9の電位V2が分圧回路10の電位V1よりも大きくなると、モータ16の駆動を禁止する。これにより、万一バッテリ3が外れた場合に、モータ16の動作による電源電圧の低下を防止できる。また、パルス波とされる発電電圧がECU1に印加されたときに、平滑化回路9の電位V2が瞬間的に増加してしまうのではなく、徐々に増加する。このため、クランキング時のように、電源ライン4にパルス状の電圧が一定期間もしくは一定回数印加される状況になっても、それを排除して電源ノイズを検出できる。

(もっと読む)

バッファ回路及びその制御方法

【課題】出力スイッチング素子をオフ状態からオン状態に切り替えるタイミングを制御し、出力特性が不安定になることを抑制することができるバッファ回路及びその制御方法を提供する。

【解決手段】出力スイッチング素子M1、M2を駆動する駆動部20と、出力スイッチング素子M1、M2の制御端子の電圧値が、閾値電圧値を超過したことを検出する検出部30と、駆動部20に接続され、検出部30の検出結果に応じて、出力スイッチング素子M1、M2の駆動能力を変更する補助駆動部40と、を備える。

(もっと読む)

温度センサを組み込んだ電力制御装置及びその製造方法

【課題】温度制御を高感度でおこなえる温度センサを組み込んだ電力制御装置及びその製造方法の提供。

【解決手段】電力制御装置100は、トレンチ型MOSFET12及びトレンチ型ダイオードデバイス13がトレンチ4’,4で区画されている。トレンチ型ダイオードデバイス13は、基板1、エピタキシャル層2、第1バイアス拡散層3、及び低ドープアノード層10がこの順に積層され、第1バイアス拡散層3の一部は低ドープアノード層10を貫通して表面に露出し、その上に第2バイアス拡散層11が形成され、低ドープアノード層10の上に高ドープアノード層7及びカソード層8が形成され、高ドープアノード層7側の表面からエピタキシャル層2に達する位置にトレンチ4が周囲を囲むように形成され、高ドープアノード層7、カソード層8、第2バイアス拡散層11、及びトレンチ4にそれぞれ電極が設けられている。

(もっと読む)

双方向スイッチ及び双方向スイッチの駆動方法

【課題】直列に接続するダイオードが不要で、オン抵抗が低く電力ロスが小さい双方向スイッチを実現できるようにする。

【解決手段】双方向スイッチは、第1のFET11と、第2のFET12と、ドレイン端子同士の間に電気的に接続された双方向電源からの電流が双方向に流れる導通状態と電流が流れない遮断状態とを制御するスイッチ制御部21とを備えている。スイッチ制御部21は、導通状態においては第1のFET11及び第2のFET12のゲート端子に、第1のFET11のソース端子と第2のFET12のソース端子とが接続されたノード13の電位を基準として閾値電圧よりも高い電圧を印加し、遮断状態においては双方向電源と各ゲート端子とを電気的に絶縁された状態とし且つノード13の電位を基準として閾値電圧以下の電圧を印加する。

(もっと読む)

電圧エクスカーション制御システム

【課題】大きな電力潮流を運ぶ回路に適し、比較的小さなサイズおよび高速応答のスナバを有するスナバ構成を提供すること。

【解決手段】電気回路の条件変化に応答して電気回路中の選択された構成要素の両端間に生じ得る、電気回路の過渡電圧ピークを制限する電圧エクスカーション制御システムは、各ダイの各カソード領域が連続体の共通端部に向かうように、連続体として直列に相互接続された複数の炭化珪素ダイオードダイ11を有する。第1の導電性電極および第2の導電性電極は、それぞれが、連続体の両端でダイ11の対応する1つと電気的に相互接続される。

(もっと読む)

差動論理回路

【課題】動作電流を電源電圧に依存しないようにすると共にバイアス配線をなくして回路の物理的配線を容易にすることが可能な差動論理回路を実現する。

【解決手段】定電流で動作する差動論理回路において、出力電圧が一定の供給用電源及びバイアス用電源を発生する電源電圧発生部と、供給用電源及びバイアス用電源が供給され、差動入力信号が入力されると共に第1の差動出力信号を出力する信号レベルレギュレータ部と、供給用電源が供給されると共に第1の差動出力信号が入力され、動作電流が第1の差動出力信号若しくは出力信号の電圧レベルにより決定される定電流動作ロジック部と

を備える。

(もっと読む)

チョッパ型コンパレータ

【課題】インバータの貫通電流を抑制し、かつ高速動作が可能なチョッパ型コンパレータを提供する。

【解決手段】アナログ入力期間に、スイッチ14を閉じて入力信号VINをノードNAに与えると共に、スイッチ17,23,26を閉じてインバータ20に並列にPMOS21とNMOS24を接続する。これにより、インバータ20の駆動能力が増加し、ノードNB,NCの電位は、短時間でインバータの閾値電位に設定される。その後、比較動作期間に、スイッチ14,17,23,26を開くと共に、スイッチ22,25を閉じてインバータ20からPMOS21とNMOS24を切り離す。更にスイッチ13を閉じてノードNAに基準電圧VREFを与えると、基準電圧VREFとアナログ信号VINの電位差が、低消費電力のインバータ20,30で増幅され、比較結果の出力信号OUTが出力される。

(もっと読む)

21 - 40 / 71

[ Back to top ]