Fターム[5J055DX52]の内容

Fターム[5J055DX52]に分類される特許

1 - 20 / 84

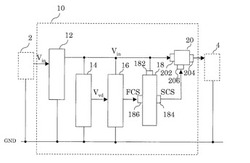

過電圧保護回路

【課題】過電圧保護回路を提供することを課題とする。

【解決手段】過電圧保護回路であって、電圧源とポータブル電子デバイスの間に提供された入力電圧が該ポータブル電子デバイスの許容定格耐電圧を超えないように設計する過電圧保護(overvoltage protection)を提供する。該回路は入力ユニットを通じて該電圧源から発生した入力電圧を受け、該入力電圧が分圧モジュールを通じて分圧電圧を生成することで、電圧安定モジュールが第1のスイッチングユニットを短絡状態、或いは、開路状態に入ることができる第1の制御信号を生成させ、また間接的に第2のスイッチングユニットを該第1のスイッチングユニットと逆の短絡状態、或いは、開路状態に入るよう制御し、該入力電圧が該定格電圧を上回った時、該第2のスイッチングユニットを通じて該入力電圧を該ポータブル電子デバイスに供給停止することで、温度の影響を受けることなく過電圧保護を実現できる。

(もっと読む)

パワーモジュール

【課題】制御電源電圧が低下した場合においても、半導体デバイスの熱破壊を防止することが可能なパワーモジュールを提供する。

【解決手段】パワーモジュール100は、半導体デバイス10のIGBT11を駆動する駆動回路20と、IGBT11のコレクタ電流がトリップレベルに達したときにIGBT11の保護動作を行う保護回路30と、駆動回路20に供給される制御電源電圧VDを検出する制御電源電圧検出回路40とを備える。保護回路30は、制御電源電圧VDが所定値よりも低くなると、センス抵抗を抵抗R1から抵抗R1,R2の直列回路に切り替えることで、トリップレベルを下げる。

(もっと読む)

スイッチング素子の駆動回路

【課題】パワーデバイス(メインスイッチM)のゲートの印加電圧をバッテリ12の正電圧より高い電圧と負電圧との双方の電圧とする場合、電源装置の小型化が困難なこと。

【解決手段】バッテリ12、端子T3、スイッチング素子SW1、コンデンサC、スイッチング素子SW2、逆流防止用ダイオードD1、端子T1および充電用抵抗体14によって、メインスイッチMのゲート充電経路が構成される。また、放電用抵抗体16、端子T2、逆流防止用ダイオードD2、スイッチング素子SW3、コンデンサC,スイッチング素子SW4、および端子T4によって、メインスイッチMのゲート放電経路が構成される。さらに、端子T3、スイッチング素子SW6、逆流防止用ダイオードD4、コンデンサC、逆流防止用ダイオードD3、スイッチング素子SW5および端子T4によって、コンデンサCの充電経路が構成される。

(もっと読む)

光源駆動装置、光源装置、プロジェクタ、及び制御方法

【課題】製造コストを抑制しつつ、カラー発光及び白色発光の双方を行うことのできる光源駆動装置を実現する。

【解決手段】駆動装置10は、LED100、200、及び300に対して電流を供給可能な電流供給部15と、LED100及び200にそれぞれ接続された抵抗13及び抵抗14と、電流供給部15を、上記複数のLEDの何れか1つに対して、抵抗13及び抵抗14を介することなく選択的に接続または遮断するスイッチ部11と、電流供給部15を、上記抵抗が接続された各LEDに対して、上記抵抗を介して接続または遮断するスイッチ部12と、を備えており、第1の発光モードにおいて、上記複数のLEDの何れか1つをスイッチ部11により電流供給部15に接続し、第2の発光モードにおいて、スイッチ部12を接続状態に設定すると共に、上記抵抗が接続されていないLEDをスイッチ部11により電流供給部15に接続する。

(もっと読む)

スイッチング回路

【課題】大電流を制御可能なスイッチング回路において、部品点数を少なくしたコンパクトな構成にて、スイッチング損失を低減するとともにサージ電圧を抑制することができるスイッチング回路を提供する。

【解決手段】高電圧ラインL1と低電圧ラインL2との間においてMOSFET30,31,32,33が並列接続され、ゲート抵抗50,51,52,53の第1の端子がMOSFET30〜33のゲート電極に接続されている。MOSFET30,31,32,33毎に設けられたゲート抵抗50,51,52,53の第2の端子がゲート電圧印加ラインL3を介してパルス発生回路60と接続されている。パルス発生回路60により、ゲート抵抗50〜53を介してMOSFET30〜33のゲート電極にパルス状のゲート電圧が印加される。ゲート電圧印加ラインL3と高電圧ラインL1との間の1箇所にコンデンサ70が接続されている。

(もっと読む)

半導体デバイス駆動回路及び半導体装置

【課題】電源電圧が変動しても半導体デバイスのオン動作及びオフ動作を安定して駆動できる半導体デバイス駆動回路を得る。

【解決手段】ドライブ回路10は、入力回路11より得られる制御信号S11に基づき、インバータG4から電源電圧VCCにより決定される“H”(オンレベル)、あるいは接地電圧GNDにより決定される“L”(オフレベル)の出力電圧VOUT1を駆動信号として半導体デバイスQ1のゲートに出力する。基準電源部14は抵抗R1及びR2の直列接続により、電源電圧VCC,接地電圧GND間の電位差を所定の分圧比率(抵抗R1及びR2による抵抗比)で分圧して得られる電圧が基準電圧VREF1として得られる。バッファ回路8は基準電圧VREF1により決定される基準信号となる出力電圧VOUT2を半導体デバイスQ1のソースに付与する。

(もっと読む)

電力用半導体素子の駆動保護回路

【課題】電力用半導体素子の制御電極の短絡動作時の電圧を通常動作時の電圧と同じ値に制限し、安全で確実な遮断を行うことが可能な電力用半導体素子の駆動保護回路の提供を目的とする。

【解決手段】本発明の電力用半導体素子の駆動保護回路は、電力用半導体素子F1と、その制御電極を駆動する駆動回路と、電力用半導体素子F1の制御電極の電圧Vgeが一定値を超えないよう制限する電圧保護回路とを備える。電圧保護回路は、電力用半導体素子F1の制御電極にエミッタが接続されたゲート放電用トランジスタTr1と、ゲート放電用トランジスタTr1にベース電位を与える電圧発生回路B1とを備え、電圧発生回路B1は、電力用半導体素子F1の駆動正電源電圧VDDから、前記駆動回路における電圧降下ΔV1を超える電圧が電力用半導体素子F1の制御電極に印加されたときに、ゲート放電用トランジスタTr1がオンできる電圧を出力する。

(もっと読む)

負荷駆動装置

【課題】負荷を駆動するための定電流のばらつきを低減することができる負荷駆動装置を提供する。

【解決手段】シャント抵抗20の一端側をオペアンプ34の反転入力端子に接続し、シャント抵抗20の他端側を基準電源32を介してオペアンプ34の非反転入力端子に接続する。シャント抵抗20に流れる電流は、駆動回路30内の第1スイッチング素子35を介して負荷10であるIGBTのゲートに流れるようになっている。これにより、基準電源32の基準電圧の値をVrefとし、シャント抵抗20の抵抗値をRoutとし、負荷10に流れる定電流の値をIcとすると、Vref=Rout×Icとなるようにオペアンプ34が第1スイッチング素子35のゲートをフィードバック制御する。これにより、シャント抵抗20に流れる電流の大きさが一定に制御され、ひいては負荷10に流す定電流のばらつきが低減される。

(もっと読む)

負荷駆動装置の製造方法

【課題】負荷駆動装置において負荷を駆動するためのスルーレートが狙い値となるように負荷駆動装置を製造する。

【解決手段】まず、半導体基板に第1基準電源32、スイッチング素子34、電流生成部35、およびオペアンプ33を備えた駆動回路30を形成する。この場合、第1基準電源32の第1基準電圧を調整することにより、負荷10に流す定電流の大きさを調整する。続いて、電流生成部35で生成されるテール電流が大きくなるようにテール電流のトリミングを行うことでオペアンプ33のスルーレートを調整する。これにより、オペアンプ33がスイッチング素子34を駆動したときに負荷10に流れる定電流が一定値に達するまでの定電流の立ち上がりの傾きを狙い値に調整することができる。

(もっと読む)

減電圧リセット回路及びこれを用いた電源装置

【課題】より確実に安定した減電圧監視を行うことが可能な減電圧リセット回路及び電源装置を提供する。

【解決手段】減電圧リセット回路15は、ドレインがリセット信号出力端子T5に接続されたNチャネル型の第1トランジスタ153と、ドレインがリセット信号出力端子T5に接続されたNチャネル型の第2トランジスタ154と、監視対象電圧V1の供給を受けて動作し、監視対象電圧V1が第1閾値電圧を下回っているときに第1トランジスタ153をオンさせる第1監視部151と、監視対象電圧V1とは異なる駆動電圧V0の供給を受けて動作し、監視対象電圧V1が第1閾値電圧よりも低く第1監視部151の下限動作電圧よりも高い第2閾値電圧を下回っているときに第2トランジスタ154をオンさせる第2監視部152と、を有する。

(もっと読む)

半導体集積回路装置および高周波モジュール

【課題】高次高調波歪またはIMDを低減可能な半導体集積回路装置および高周波モジュールを提供する。

【解決手段】例えば、アンテナ端子ANTと複数の信号端子Txa,Rxb,Rxcとの間にそれぞれ複数のトランジスタQa,Qb,Qcを備えた所謂アンテナスイッチに対して、電圧供給回路VD_BKを設ける。電圧供給回路VD_BKは、電圧供給端子Vddから前述した複数の信号端子Txa,Rxb,Rxcの中の少なくとも2つの信号端子(例えばRxb,Rxc)に向けてそれぞれ抵抗素子Radd1,Radd2を介して電圧を供給する回路である。これによって、リーク等によって低下したアンテナ電圧Vantを上昇させることが可能となり、例えばオフ状態となっているトランジスタQb,Qcを深いオフ状態にすることが可能となる。

(もっと読む)

スイッチングトランジスタの制御回路

【課題】イネーブル信号をHIGHにしてから急速にスイッチングトランジスタをオンし、かつ突入電流を防止することが可能なスイッチングトランジスタの制御回路を提供すること。

【解決手段】イネーブル信号によりトランジスタM2はオフする。トランジスタM8はオフし、ノードCTの電位はグラウンドと等電位になり、反転器の出力ACTはHIGHとなり、トランジスタM9はオンする。イネーブル信号の反転信号によりトランジスタM5はオフし、トランジスタM3、M4、M6のゲート電位はM4とIBIASで決まる電位VBIASと等電位となってトランジスタM3、M4、M6はオンとなり、並列接続されたトランジスタM3、M6の能力に応じたIGD(大)が流れる。トランジスタM1、M7は、電流IGD(大)によって急速にゲート容量へ電荷が蓄えられて急速にオンになり、電流IOUT、IDETが流れる。

(もっと読む)

半導体素子の駆動装置

【課題】半導体素子のスイッチング時において、スイッチング損失の増加を抑制しつつ、サージ電圧を低減すること。

【解決手段】電子回路1の半導体素子駆動回路13は、ゲート抵抗21と、電圧源22と、di/dt帰還部23と、バッファ111と、を備えている。バッファ111は、従来良く使われる方式であるトランジスタ111ta,111tbで構成されるIGBT駆動用のバッファ回路の少なくとも一部である。di/dt帰還部23は、トランス121と、抵抗122と、を備えている。即ち、トランス121が、di/dt検出部及びゲイン部に対応する。なお、電圧源22とバッファ111とを結ぶ経路に抵抗122が直列接続され、抵抗122の両端が、トランス121の2次側に接続されており、当該経路上の抵抗122の両端の間が、電圧源に対応する。

(もっと読む)

半導体集積回路装置

【課題】出力トランジスタの過電流を簡略な回路構成で抑制する。

【解決手段】半導体集積回路装置70の過電流保護回路30には、過電流検出部1と過電流制御部2が設けられる。過電流検出部1には、電流源11乃至13、NPNトランジスタQ1乃至Q3が設けられる。NPNトランジスタQ1及びNPNトランジスタQ2は第1のカレントミラー回路を構成し、NPNトランジスタQ2のコレクタ側から過電流検出信号Skkを出力する。NPNトランジスタQ1及びNPNトランジスタQ3は、第2のカレントミラー回路を構成し、NPNトランジスタQ3のコレクタ側から過電流制御信号Sksを過電流制御部2に出力する。過電流保護回路30は、出力トランジスタMDT1に流れる過電流を出力トランジスタMDT1のソースと抵抗R1の間で検出して、過電流を抑制する。

(もっと読む)

スイッチング回路

【課題】スイッチング素子の発熱をおさえ、高効率のスイッチング回路を提供する。

【解決手段】入力端子2と出力端子3の間に設けたスイッチング回路1において、入力端子側に設けられた第1のスイッチング素子4と、第1のスイッチング素子の入力側に接続された第2のスイッチング素子5と、第2のスイッチング素子の入力側に接続された第3のスイッチング素子8と、を備え、第2のスイッチング素子5にて、第1のスイッチング素子4の入力信号の電流を強制的に引き抜き、更に、第3のスイッチング素子8にて、第2のスイッチング素子ゲート端子5に入力される電流を高速に引き抜くことによって、第1のスイッチング素子5の発熱量をおさえ、スイッチング回路1の効率を高めることができる。

(もっと読む)

半導体装置及びその制御方法

【課題】プルアップ回路(バスホールド回路)の電源電圧Vcc及び入力端子INに電位差が生じる場合でもリーク電流を発生させない手段を提供する。

【解決手段】パスホールド回路に制御端子CNTを設ける。この制御端子CNTの反転出力で動作するスイッチとしてMOSFET13を備える。一方入力端子INと制御端子CNTの入力はNORゲート31に入力され、このNORゲート31の出力がパスホールド回路の入力端子・電源電圧間の接続を制御するMOSFET12のゲート端子に入力される。MOSFET12及びMOSFET13を直列に接続することで、入力端子・電源電圧間の接続をより制度よく制御し、リーク電流の発生を抑止する。

(もっと読む)

5以上の電圧レベルを切り換えるためのスイッチギア

【課題】簡単な方法で5以上の電圧レベルを切り換えることができるスイッチギアセルを提供する。

【解決手段】n=5、7、9,...,であるn個の電圧レベルを切り換えるスイッチギアセルの第1及び第2の分岐回路1、2は、n−1の直列接続された電力半導体スイッチと、直列接続された電力半導体スイッチ間のp=n−2電力半導体スイッチ接合点を有している。分岐回路1、2のカウント数x<(p+1)/2を有する電力半導体スイッチ間の接合点に接続された中間回路5の電力半導体スイッチ9は第1のキャパシタンス6に接続され、さらに第1又は第2の分岐回路1、2のカウント数x<(p+1)/2を有する電力半導体スイッチ間の接合点で第1のキャパシタンス6に接続される。中間回路5のさらに別の電力半導体スイッチ10は第2のキャパシタンス7に接続され、第2のキャパシタンス7は第2の分岐回路2の電力半導体スイッチ接合点に接続される。

(もっと読む)

サンプルホールド回路、ドライバ、電気光学装置、及び電子機器

【課題】回路の大規模化を抑えながら適正な位相補償を実現する。

【解決手段】演算増幅器OP1と、サンプルホールド回路の入力ノードNIと、接続ノードNSとの間に設けられたサンプリング用スイッチ素子SSと、接続ノードと、演算増幅器の第1の入力端子のノードであるサミングノードNEGとの間に設けられたサンプリング用キャパシタCSと、演算増幅器の出力端子とサミングノードとの間に設けられた帰還用スイッチ素子SFと、接続ノードと、演算増幅器の出力端子との間に設けられたフリップアラウンド用スイッチ素子SAと、サンプリング用キャパシタのサミングノード側の端子NCと演算増幅器の出力端子との間に設けられた位相補償用抵抗素子RPと、を含む。

(もっと読む)

半導体装置

【課題】外部端子がオープン又は接地電圧Vssに接続されてしまった場合でも、回路の発熱を防止でき、電流供給先である負荷回路の不具合の発生を防止することができる半導体装置を得る。

【解決手段】外部端子T1と抵抗R1との接続が遮断された場合、抵抗R1と接地電圧Vssとの接続が遮断された場合、又は外部端子T1が接地電圧Vssにショートした場合は、端子電圧検出回路3は、ローレベルの信号を出力してPMOSトランジスタM11をオンさせ、発振回路4に対して発振を停止させて出力端からハイレベルの信号を出力させるようにした。

(もっと読む)

スイッチング回路、及びトランジスタの駆動回路

【課題】トランジスタのゲート電位をスレショルド電位未満に維持するための構成を備えるスイッチング回路において、ゲート電位の立ち上がりの遅延を抑制すること等。

【解決手段】電圧制御される主トランジスタと、グランド端子に接続され、前記主トランジスタのゲートスレショルド電圧よりもオン時ドレインーソース間電圧が低い副トランジスタと、第1の抵抗が設けられ、電源装置に接続される端子と前記主トランジスタのゲートとを接続する第1の電力ラインと、前記主トランジスタのゲートから前記副トランジスタへ流れる電流を選択的に許容する第2の電力ラインと、第2の抵抗が設けられ、前記端子と前記副トランジスタとを接続する第3の電力ラインと、を有し、前記第2の抵抗の抵抗値は、前記主トランジスタの容量と前記第1の抵抗の抵抗値の積を前記副トランジスタの容量で除した値よりも小さい値である、スイッチング回路。

(もっと読む)

1 - 20 / 84

[ Back to top ]