Fターム[5J056EE14]の内容

Fターム[5J056EE14]に分類される特許

1 - 20 / 61

半導体装置

【課題】より少ない調整ステップでキャリブレーションを完了する。

【解決手段】出力端子(DQに相当)と、出力端子と接続され、出力端子を調整可能なインピーダンスで駆動する出力回路(210に相当)と、出力回路のインピーダンスを段階的に調整するキャリブレーション回路(100)と、を備え、キャリブレーション回路は、キャリブレーション動作の実行を指示するコマンドを受けて、インピーダンスの調整を開始し、インピーダンスを変化させる変化幅を、開始直後に対し以降においてより狭めるように調整する。

(もっと読む)

半導体装置

【課題】適宜繰り返し行われるキャリブレーションに要する時間を短縮する。

【解決手段】半導体装置は、入力コマンドに応じ、出力ドライバーのインピーダンスを調整するキャリブレーションを、設定値を用いて行うキャリブレーション回路と、温度センサーと、前記出力ドライバーの温度特性情報を記憶する記憶回路と、前記温度センサーからの検出信号と前記記憶回路から読み出した前記温度特性情報とに基づいて前記設定値を変更する設定信号を生成し、前記キャリブレーション回路へ出力する設定回路と、を備える。

(もっと読む)

半導体装置、及び出力バッファのインピーダンスを調整する方法

【課題】出力バッファのインピーダンスを制御する複数の制御ビットを転送するデータバスの配線面積を削減できる半導体装置、及び出力バッファのインピーダンスを調整する方法を提供する。

【解決手段】インピーダンス制御情報を生成するZQ回路(ZQ回路40)と、前記インピーダンス制御情報を受けて自身のインピーダンスが制御される出力バッファ(出力回路80)と、を備え、前記インピーダンス制御情報を構成する複数の制御ビット情報は前記ZQ回路からシリアルに転送される。

(もっと読む)

半導体装置

【課題】出力回路のインピーダンス調整の精度を向上する半導体装置を提供する。

【解決手段】各々が調整可能なインピーダンスを備える複数の単位バッファを含む出力回路(出力バッファ101)と、複数の単位バッファ回路のうちの1または複数個の単位バッファ回路を選択的に活性化する制御回路(出力制御回路150)と、複数の単位バッファのそれぞれのインピーダンスを調整するインピーダンス調整部であって、当該インピーダンス調整部は、制御回路によって選択的に活性化された1又は複数個の単位バッファ回路の個数が変化することに応じて複数の単位バッファのそれぞれのインピーダンスを調整する、インピーダンス調整部(インピーダンス調整部30)と、を備える。

(もっと読む)

表示装置、表示モジュール及び電子機器

【課題】回路を構成するトランジスタ数を少なくし、且つレベルシフタを配置することな

くシフトレジスタとして正確に動作を行う半導体回路の提供することを課題とする。

【解決手段】第1端子が高電位電源に接続されたpチャネル型トランジスタと、第1端子

が低電位電源に接続されたnチャネル型トランジスタと、を含む回路群と、インバータ回

路と、をm段(mは任意の正の整数であり、m≧3)有し、第2n−1段目(nは任意の

整数であり、m≧2n≧2)の回路群の前記nチャネル型トランジスタのゲートにはクロ

ック信号が入力され、第2n段目(nは任意の整数であり、m≧2n≧2)の回路群の前

記nチャネル型トランジスタのゲートには反転クロック信号が入力される。

(もっと読む)

半導体装置

【課題】ウエハーテストにおいて、キャリブレーション動作の評価を、容易、かつ高精度に行うことができる半導体装置を提供する。

【解決手段】キャリブレーション端子ZQを駆動するレプリカバッファ(131)と、レプリカバッファの出力インピーダンスを変化させる際に目標となるインピーダンスが設定され、キャリブレーション端子ZQに接続される可変インピーダンス回路(170)と、を備える。

(もっと読む)

差動出力バッファ

【課題】送信状態とスタンバイ状態との間の遷移時間の増大を抑制しつつ、電流の変動を低減する。

【解決手段】メインドライバ1は、差動信号PREP、PRENのレベル変換を行い、バイパス回路2は、メインドライバ1の動作状態とスタンバイ状態との間の遷移時に高電源電位VDDから低電源電位VSSに流れる電流I5の変化量が一定の範囲内に収まるようにメインドライバ1に流れる電流I5をバイパスさせる。

(もっと読む)

半導体回路および半導体装置

【課題】簡易な構成で電荷の再利用効率を高め、複数のLSIを搭載したシステム全体のエネルギー効率を向上することが可能な半導体回路および半導体装置を提供する。

【解決手段】入力端子20にLレベルの信号が入力されたとき、回路素子10の出力端子22に接続される信号線24の配線容量Cpに正の電荷が充電される。入力端子20にHレベルの信号が入力されたとき、NMOSトランジスタNr1は、論理素子のNMOSトランジスタN1が導通するのと同時に導通する。これにより、信号線24から放電される電荷の一部が、NMOSトランジスタNr1およびダイオードD1を介して、電荷回収線2に移動する。電荷回収線2が回収した電荷は、電荷再利用端子3を介して半導体チップ1Aの外部に放出されると、電荷再利用線30に接続された電荷回収用の容量素子Cextに蓄積される。蓄積され電荷は、他の半導体回路等の電源端子に供給される。

(もっと読む)

半導体装置のトリミング方法、及びトリミング制御回路

【課題】スイッチ素子の製造バラツキを排除し、より均一で確実な溶断が行える半導体装置のトリミング方法、及びトリミング制御回路を提供すること。

【解決手段】電位が異なる第1電源(電源端子c)と第2電源(接地端子d)との間にて直列接続された第1スイッチ素子S1〜S3およびフューズF1〜F3を内蔵した半導体装置101における第1スイッチ素子S1〜S3をオン制御することでフューズF1〜F3に電圧を印加してフューズF1〜F3を溶断する半導体装置101のトリミング方法であって、第1スイッチ素子S1〜S3をターンオン制御することにより、第1電源(電源端子c)からフューズF1〜F3を溶断させない第1電圧値を所定時間印加するステップと、第1電圧値の印加が完了した後、第1電源(電源端子c)からフューズF1〜F3を溶断させる第2電圧値を印加するように切り替えるステップと、を含む。

(もっと読む)

電流消耗を減らす構造を有する半導体装置及びそのターミネーション方法

【課題】電流消耗を減らすオン・ダイ・ターミネーション(ODT)構造を有する半導体装置及びそのターミネーション方法を提供する。

【解決手段】基準電圧と外部抵抗とが連結されたキャリブレーション端子の電圧に応答してキャリブレーションコードを発生させるキャリブレーション回路と、キャリブレーションコードとODT制御信号とに応答して、データ入出力パッドのターミネーション抵抗値を制御するODT装置と、を備え、データ入出力パッドのターミネーション抵抗値は、キャリブレーション端子の抵抗値より大きい半導体装置である。

(もっと読む)

半導体装置及び情報処理システム

【課題】電源電圧を低下させた場合であっても、正しくデータ転送が可能な半導体装置を提供する。

【解決手段】出力ドライバ100と、出力ドライバ100の特性を切り替える特性切替回路18を備える。特性切替回路18は、電源ラインに供給される電源電圧VDDQが第1の電圧VDDQ1である場合における出力ドライバ100の出力信号の立ち上がり時間及び立ち下がり時間と、電源ラインに供給される電源電圧VDDQが第2の電圧VDDQ2である場合における出力ドライバ100の出力信号の立ち上がり時間及び立ち下がり時間を互いに一致させる。これにより、電源電圧を低下させても高調波成分やクロストークによる影響が増大することがない。また、電源電圧を低下させてもレシーバ側における受信条件が変化しないことから、電源電圧にかかわらず信号の送受信を正しく行うことが可能となる。

(もっと読む)

レベルシフタを備える半導体装置、ディスプレイ装置及びその動作方法

【課題】レベルシフタを備える半導体装置、ディスプレイ装置及びその動作方法を提供する。

【解決手段】第1論理状態を有する一つのビット及び第2論理状態を有する少なくとも一つのビットを含むコードを生成するコード生成部と、複数の電圧制御部及び複数の電圧変換部を備え、コードに応答して複数の出力端から第1電圧レベルまたは第2電圧レベルを有する出力信号を出力するレベルシフタと、を備え、複数の電圧制御部のうち一つの電圧制御部を除いた残りの電圧制御部は、出力端のうち一つの出力端を除いた残りの出力端を通じて出力される第1信号を、少なくとも一つのビットに応答して第1電圧レベルに制御し、複数の電圧変換部のうち一つの電圧変換部は、除いた一つの出力端を通じて出力される第2信号を、第1信号に応答して第2電圧レベルに制御する半導体装置である。

(もっと読む)

スプリット−バイアス電流のスケーラブル・バッファ

集積回路を渡る伝達のために、高周波数信号(IN)をバッファリングするための回路、技術、方法が開示される。ある特別の実装において、複数の増幅回路(M1,M2)は、電圧制御発振器および/またはデジタル制御発振器からの信号を増幅するために個別にバイアスされ、デバイス上の局所発振器の信号を提供する。 (もっと読む)

レベルシフト回路、表示装置および電子機器

【課題】貫通電流を抑えつつ大振幅のレベル変換を実現可能なインバータ型のレベルシフト回路を提供する。

【解決手段】インバータ型のレベルシフト回路10において、初段のCMOSインバータ回路11のnチャネルトランジスタ112のサイズを、pチャネルトランジスタ111のサイズのa倍(例えば、100倍)以上の極端なサイズ差に設定する。このサイズ比により、貫通電流を抑えつつ、例えば0−3V振幅から0−12V振幅にレベル変換する場合のような大振幅のレベル変換を実現する。

(もっと読む)

レベルシフト回路、表示装置および電子機器

【課題】貫通電流を抑えることができるとともに、トランジェントの制御の自由度が高いレベルシフト回路を提供する。

【解決手段】第1,第2のトランジスタ(111,112/121,122)およびこれらのトランジスタ間に接続された第3のトランジスタ(113/123)を有する第1,第2の回路部11,12は、第1電源vddと第2電源vssとの間に並列に接続されている。第1の回路部11の第3のトランジスタ113のゲート電極は第2の回路部12の出力ノードに、第2の回路部12の第3のトランジスタ123のゲート電極は第1の回路部11の出力ノードにそれぞれ接続されている。このレベルシフト回路において、第2の回路部12の入力ノードNin2に入力される第1振幅のパルス信号in1を第2振幅のパルス信号outにレベルシフトする際に、第1の回路部11の入力ノードNin1の電圧値によって第2振幅のパルス信号outのトランジェントを制御する。

(もっと読む)

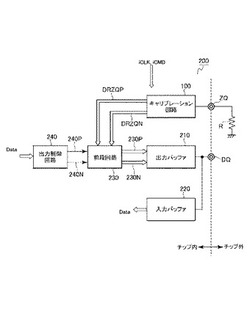

半導体装置

【課題】出力バッファのインピーダンス調整を行う半導体装置を提供する。

【解決手段】制御回路1は、外部からの読み出しまたは書き込みコマンドに応じてDQイネーブル信号を発生する。コマンドラッチ回路2Aは、外部からのコマンド信号(ZQコマンド)に応じて、ZQEnable信号を発生する。ZQ調整回路3は、ZQEnable信号が入力されると、内部に設けられたレプリカ回路のインピーダンス調整を始める。ZQ調整回路3は、DQイネーブル信号が入力される期間中は、インピーダンス調整結果であるドライバコードのDQ回路4への出力を禁止する。

(もっと読む)

電流駆動型D/Aコンバータのバイアス回路

【課題】電流スイッチトランジスタの制御電圧によって生じるノイズをより小さくし、また、電流スイッチがオフする際に生じていたグランドもしくは電源電圧のノイズを低減し、高性能な電流駆動型D/Aコンバータを得る。

【解決手段】NMOSトランジスタM12P,M12N,M22P,M22N,M32P,M32Nがオフするオフ制御電圧(BIAS3)を、オン制御電圧(BIAS2)に近づけた電圧に設定したことにより、NMOSトランジスタの制御電圧振幅(オン制御電圧−オフ制御電圧)が小さくなり、寄生容量を介した電荷注入によるノイズの発生を低減すると共に、オフする際の寄生容量からグランドもしくは電源への放電電流の流れ込みによるグランド電圧もしくは電源電圧のノイズの発生を低減し、高性能な電流駆動型D/Aコンバータを得ることができる。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

半導体集積回路装置

【課題】 高速及び長距離のデータ転送のためには多タップ(Tap)、高精度かつ設定範囲の広い電流モード出力回路(CML)が必要だが、エンハシス量の設定を単位ソース結合対回路の付加により実現する方式の場合、電流モードロジック出力容量が増大し、高速化に問題が生じていた。

【解決手段】 電流モード出力回路(CML)をm分割した単位ソース結合対回路101、終端抵抗102及びデータセレクタ107により出力回路を構成する。各タップ(Tap)のエンハシス量はm分割した単位ソース結合対回路の比で割り振られるため、出力振幅1のサイズのままでエンハシス量を任意に設定できる。その結果、伝送速度を向上し、伝送距離を延長することができる。

(もっと読む)

ドライバ回路、立ち上がり電圧及び立ち下がり電圧の制御方法

【課題】オーバーシュート及びアンダーシュートが大きく発生する。

【解決手段】(1)並列接続されている第1のCMOS回路及び第2のCMOS回路と、(2)(2A)入力電圧が第1の電圧から第2の電圧に切り換わる場合、(2Aa)駆動電圧が制御部の第1の閾値に到達する以前には、第1のP型FET及び第2のP型FETを導通させ、(2Ab)駆動電圧が制御部の第1の閾値に到達した以後には、第2のP型FETのみを導通させ、(2B)入力電圧が第2の電圧から第1の電圧に切り換わる場合、(2Ba)駆動電圧が制御部の第2の閾値に到達する以前には、第1のN型FET及び第2のN型FETを導通させ、(2Bb)駆動電圧が制御部の第2の閾値に到達した以後には、第2のN型FETのみを導通させる制御部と、を含む。

(もっと読む)

1 - 20 / 61

[ Back to top ]