Fターム[5J064BB07]の内容

圧縮、伸長、符号変換及びデコーダ (21,671) | 主要(機能)構成 (1,931) | 雑音除去 (141)

Fターム[5J064BB07]に分類される特許

1 - 20 / 141

音声復号装置及び音声復号方法

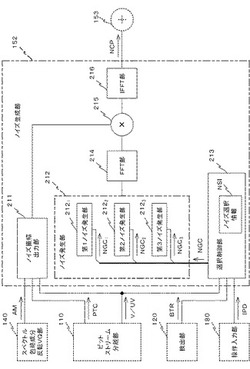

【課題】

復号を行った音声信号に対応する音質を維持しつつ、復号のための演算負荷を適正化する。

【解決手段】

検出部120が、音声信号のビットレートBTRを検出し、検出結果を選択制御部213へ送る。選択制御部213は、ノイズ選択情報NSIを参照して、検出されたビットレートBTRに予め関連付けられた個別のノイズ発生部212j(j=1〜3)を選択し、当該選択されたノイズ信号発生部212jに対して、ノイズ信号を発生すべき旨の選択制御信号NGCを送る。そして、選択されたノイズ発生部212j が、ノイズ信号を発生させる。引き続き、ビットレートBTRに対応して選択されたノイズ信号を反映した加算用ノイズ信号NCPと、ハーモニック合成部から送られた信号とが、加算部153において加算され、当該加算結果に基づく復号音声信号が外部に出力される。

(もっと読む)

オーバサンプリングされたアナログ・デジタル変換を備えるリード・チャネル

【課題】オーバサンプリングされたアナログ・デジタル変換を使用して、リード・チャネルの中の信号を処理するための方法および装置を提供すること。

【解決手段】アナログ入力信号に対してオーバサンプリングされたアナログ・デジタル変換を実行して、所与のビット間隔についてアナログ入力信号に対応する複数のデジタル・サンプルを生成する。次いで、デジタル・サンプルのうちの1つまたは複数に対してデータ検出アルゴリズムを適用して、検出された出力を取得することができる。オーバサンプリングされたアナログ・デジタル変換は、等化処理および/またはフィルタリング処理の少なくとも一部をデジタル領域に移すことにより、アナログ設計を簡略化する。

(もっと読む)

量子化装置

【課題】 回路規模の増加を抑制しつつ、複数ビットの量子化信号を生成する。

【解決手段】 量子化装置は、第1クロックの1周期前の量子化信号に基づく量子化誤差と第1信号とに基づいて、第2信号を生成する信号処理部と、第1クロックより高速の第2クロックに同期して動作し、第2信号を第1クロックの1周期以内に量子化し、量子化信号を生成する量子化部とを有している。

(もっと読む)

高速データ加重平均

【課題】最小ループ遅延を有し、改善された安定性をサポートする高速データ加重平均(DWA)2重サンプリング変調器のための方法および装置が提供される。

【解決手段】量子化およびDEMは非オーバーラップ時間内に行われる。この時間遅延の低減によって、アナログ積分器に関して電力を節約することができる。基準電圧の交番によって、分割DWAのDC信号は除去され、また、交番が比較器の入力において行われるので、追加の遅延はない。実施形態は、8倍のオーバーサンプリング比(OSR)および15レベル量子化器を使用する。

(もっと読む)

信号処理装置

【課題】シグマデルタA/D変換器を用いた場合におけるインパルス状ノイズの耐性を高めることができるとともに、回路の消費電流も低減できる信号処理装置を提供すること。

【解決手段】温度測定信号をシグマデルタA/D変換器でデジタル信号に変換するように構成された信号処理装置において、前記シグマデルタA/D変換器で高速サンプリングすることにより得られる前記温度測定信号の複数の測定データの中央値を検出する手段を設けたことを特徴とするもの。

(もっと読む)

デジタル−アナログ変換器及びデジタル−アナログ変換装置

【課題】 簡単な回路構成で、スイッチのオン抵抗値によるアナログ出力信号の歪みやノイズの発生を防止することができるデジタル−アナログ変換器を提供する。

【解決手段】 サンプリング容量素子Ciの一方の端子と対応する入力端子Diとの接続及び切断並びにサンプリング容量素子Ciの他方の端子と第1基準電圧源B1との接続及び切断を切り替える第1のスイッチユニットSU1と、第1のスイッチユニットSU1の切り替えにおける切断及び接続に応じて、サンプリング容量素子Ciの他方の端子と演算増幅器2の反転入力端子との接続及び切断、複数のサンプリング容量素子Ciの一方の端子の相互の接続及び切断、並びに一方の端子が相互に接続されたサンプリング容量素子Ciの電圧に応じた電圧を演算増幅器2の出力端子に出力する電気経路の閉成及び開放を切り替える第2のスイッチユニットSU2と、電気経路に設けられた抵抗素子Rsとを備えている。

(もっと読む)

サブサンプリング技法を利用する受信器のデジタル処理構造

【課題】無線通信の送受信システムに係わるデジタル方式の受信器を提供する。

【解決手段】RF信号をIF信号又はDC信号に変換するサブサンプリングの際、要する信号帯域に対してはオーバーサンプリングして要らない信号もデジタル信号に変換させた後、デジタルブロックから効果的に除去する。本発明によると一般的なアナログ設計方式の受信器に比べて、フィルタ、LNA、そして、ADCだけでアナログ設計部が構成されるので、アナログ構成ブロックの構造が簡単になる。従って、ADCの後端に設置されるデジタル構成ブロック等の構造も最適化してデジタル方式の受信器を構成することができる。

(もっと読む)

ディジタルアナログ変換器

【課題】低消費電力で、素子の相対的なばらつきによって発生する信号歪みやSNR劣化が少ないディジタルアナログ変換器を提供する。

【解決手段】1ビットレジスタ103と、1ビットディジタルΔΣ信号及び、1ビットレジスタ103の出力信号を一対の入力信号とし、一対の出力信号を出力するスイッチ回路104、この一対の出力信号を入力し、ノイズを除去して第1出力信号、第2出力信号を出力する2端子対インピーダンス素子105、反転入力端子108a、非反転入力端子108b、出力端子108cを有する演算増幅器108、反転入力端子108aと出力端子108cとの間に接続されるインピーダンス素子106、非反転入力端子108bに一端が接続され、他端に基準電圧が与えられるインピーダンス素子107によってディジタルアナログ変換器を構成する。

(もっと読む)

A/Dコンバータ及びD/Aコンバータ

【課題】A/Dコンバータ及びD/Aコンバータにおいて、比較的簡単な構成でノイズを低減可能にすることを目的とする。

【解決手段】ΣΔ変調器が出力するΣΔ変調データの変化量とダミーデータの変化量の合計を一定に調整する調整回路と、前記ΣΔ変調データを供給されるレベル変換部を備え、前記レベル変換部は、前記ΣΔ変調データのレベルを変換して出力する第1のレベルコンバータと、前記調整回路からのダミーデータを供給されてダミーノイズを補間する第2のレベルコンバータを有し、前記第2のレベルコンバータにより前記ΣΔ変調データに対するノイズの周波数依存性をキャンセルするように構成する。

(もっと読む)

ΔΣ型アナログデジタル変換器およびそれを用いた電子機器

【課題】ノイズ特性を改善することが可能なΔΣ型アナログデジタル変換器を提供する。

【解決手段】ΔΣ型A/D変換器100は、アナログの入力信号Sinをデジタルの出力信号Soutに変換する。D/A変換器40は、デジタルの出力信号Soutをアナログの帰還信号Sfbに変換する。差分演算回路10は、入力信号Sinに応じた信号Sin’と、帰還信号Sfbに応じた信号Sfb’の差分に応じた差分信号Sdを生成する。フィルタ回路20は、直列に接続された複数の積分器INTを含み、差分信号Sdをフィルタリングする。量子化器30は、フィルタ回路20の出力信号Sfを量子化し、出力信号Soutを生成する。フィルタ回路20は、ある積分器INT3の出力信号に所定の係数を乗じそれより前の積分器INT2の入力へと帰還する少なくともひとつの帰還係数回路CO9を含み、当該帰還係数回路CO9の係数は調節可能に構成される。

(もっと読む)

信号処理装置

【課題】無信号時にノイズシェーパを巡回する量子化誤差ノイズを除去する際に、可聴帯域に発生するノイズを抑圧する。

【解決手段】信号処理装置100は、乗算器22-0〜22-3を有するノイズシェーパ20A、PCMデータDinの無信号状態を検出する無信号状態検出回路30、および係数設定回路40を備える。係数設定回路40は、無信号状態が検出されると、ノイズシェーパ20Aの次数を、4次から0次に向けて順次減少させるように係数a0〜a3を設定する。これにより、高域周波数成分が段階的に減少するので、第2データD2の振幅は段階的に減少する。

(もっと読む)

信号処理装置

【課題】非線形処理で生じる高調波の折り返しノイズを低減する。

【解決手段】信号処理装置100は、サンプリング周波数FsでサンプリングされたPCMデータDinにオーバーサンプリング処理を施すオーバーサンプリング回路20と、補間処理によってサンプリング周波数を128Fsまで高める補間回路30と、補間回路30の出力信号にスライス処理を施すスライス回路40と、ノイズシェーパ50と、PWM回路60とを備える。

(もっと読む)

アナログデジタル変換回路及び光結合型絶縁回路

【課題】演算増幅器のオフセット電圧を低減し、かつ容量雑音を低減して小型化可能としたアナログデジタル変換回路及び光結合型絶縁回路を提供する。

【解決手段】アナログ信号を入力し、第1の期間は前記アナログ信号を逆相で出力し、第2の期間は正相で出力する第1のスイッチ回路と、前記アナログ信号をクロスカップルに入力して積分するスイッチトキャパシタ型の第1の積分回路と、前記第1の積分回路の出力及び同相出力電位を出力する第2のスイッチ回路と、前記第2のスイッチ回路の出力をサンプリング及び積分する第2の積分回路と、前記第2の積分回路の出力を1ビット出力する量子化回路と、前記量子化回路の出力をアナログ信号とするデジタルアナログ変換回路と、を備え、前記第1及び第2の積分回路は、前記デジタルアナログ変換回路の出力をそれぞれクロスカップルに入力して積分する。

(もっと読む)

EEGモニタリング・システムのための入力変換器,信号変換方法およびモニタリング・システム

モニタされるべき人物によって連続して持ち運ばれることができるEEGモニタリング・システム(40)における雑音および電流消費を最小化するために,EEGモニタリング・システム用の入力変換器(44)が案出される。上記入力変換器のアナログ−ディジタル変換器は,入力段,出力段およびフィードバック・ループを備え,上記入力段は増幅器(QA)および積分器(RLF)を備える。変圧器(IT)が上記入力変換中の上記入力段の上流に配置される。上記変圧器(IT)の変換比はその入力電圧よりも大きな出力電圧を供給する変換比を持ち,これにより,上記入力段についての信号電圧に固定係数が乗算される。上記変圧器(IT)は少なくとも2つのキャパシタ(Cx,Cy,Cz)を有するスイッチング・キャパシタ変圧器である。この発明はさらにアナログ信号を変換する方法,および上記入力変換器(44)を備えるEEGモニタリング・システムを提供する。  (もっと読む)

(もっと読む)

信号処理装置

【課題】複数の入力アナログ信号に対応する複数の入力部を備える構成を採用した場合に、フィルタを用いて特定周波数成分を除去するに当たって、コスト削減を図ることが可能な信号処理装置を提供する。

【解決手段】複数の入力アナログ信号に対応する複数の入力部で前記入力アナログ信号をデジタル信号に各々変換し、前記デジタル信号を演算部に受け渡して所定の信号処理を行う信号処理装置において、前記入力部及び演算部は、特定周波数成分を共同して所定量だけ減衰させるフィルタを各々備える。

(もっと読む)

信号処理装置および信号処理方法

【課題】 使用設定を変化させた場合でも、ノイズサプレッサが十分な機能を発揮し、高品質な音声を送受信することを可能とする。

【解決手段】 音声符号化器120は、互いに異なるアルゴリズムにより音声データを符号化する3つの回路として、A方式符号化部121、B方式符号化部122、C方式符号化部123を備える。ノイズサプレッサ110は、互いに異なるアルゴリズムにより背景雑音を抑圧する3つの回路として、X方式ノイズサプレス部111、Y方式ノイズサプレス部112、Z方式ノイズサプレス部113を備える。サプレス方式切換制御部114は、符号化方式切換制御部124からの情報に基づいて、音声符号化器120にて機能する符号化部(121,122,123のいずれか)に合わせて、最適なノイズサプレス部(111,112,113のいずれか)を機能させるようにしたものである。

(もっと読む)

信号処理装置および信号処理方法

【課題】 使用設定を変化させた場合でも、ノイズサプレッサが十分な機能を発揮し、高品質な音声を送受信することを可能とする。

【解決手段】 音声符号化器120は、互いに異なるアルゴリズムにより音声データを符号化する3つの回路として、A方式符号化部121、B方式符号化部122、C方式符号化部123を備える。ノイズサプレッサ110は、互いに異なるアルゴリズムにより背景雑音を抑圧する3つの回路として、X方式ノイズサプレス部111、Y方式ノイズサプレス部112、Z方式ノイズサプレス部113を備える。サプレス方式切換制御部114は、符号化方式切換制御部124からの情報に基づいて、音声符号化器120にて機能する符号化部(121,122,123のいずれか)に合わせて、最適なノイズサプレス部(111,112,113のいずれか)を機能させるようにしたものである。

(もっと読む)

デジタルオーディオ信号におけるプリエコーの減衰

変換符号化に基づいて生成されたデジタルオーディオ信号において、デジタルオーディオ信号の現在のフレームに関して復号化するときに、プリエコーを減衰させる方法であり、少なくとも現在のフレームの再構成された信号に基づいて連結された信号を定義するステップ(CONC)と、連結された信号を確定した長さのサンプルのサブブロックに分割するステップ(DIV,101)と、連結された信号の時間的なエンベロープを計算するステップ(ENV,102)と、時間的なエンベロープの高エネルギーゾーンへの遷移を検出するステップ(DETECT,104)と、遷移が検出されたサブブロックに先行する低いエネルギーのサブブロックを判定するステップ(DETECT,104)と、判定されたサブブロックにおける減衰のステップ(ATT)とを含む方法に関係する。減衰は判定されたサブブロックの各々に関して連結された信号の時間的なエンベロープの関数として計算された減衰係数に従って遂行される。  (もっと読む)

(もっと読む)

整合された量子精密フィードバックDACのための方法および装置

アナログ信号を受信するための入力と、入力に結合された第1の積分器と、第1の積分器と縦続接続された第2の積分器と、第2の積分器からの出力をデジタル化する量子比較器とを有する、二次超電導体デルタシグマアナログ/デジタル変調器は、量子比較器からの出力と第1の積分器への入力との間のフィードバックループ内に整合された量子精密DACを提供することによって、量子化雑音を低減させる。整合された量子精密フィードバックDACは、同様に再現可能な電圧パルスを生成し、マルチビット出力のために構成され得、より高速な刻時速度を可能にするように時間的にインタリーブされ得、平衡双極性構成として採用され、誘導性入力結合を可能にし得る。双極性フィードバックは、第1のDACの増幅率が、比較器から第2の積分器への暗黙的フィードバックの量だけ整合された逆向きのDACの増幅率を上回るときに平衡化される。  (もっと読む)

(もっと読む)

デジタルオーディオ信号をアナログオーディオ信号に変換する変換装置及びその変換方法

【課題】デジタルオーディオ信号をアナログオーディオ信号に変換する変換装置を提供する。

【解決手段】変換装置は、第一回路、マルチプレクサ、ローパスフィルタ及びD/A変換回路を含む。第一回路は、前記デジタルオーディオ信号を受信し、前記デジタルオーディオ信号をNビットΣΔ変調信号に変換し、前記マルチプレクサは、選択信号に基づいて選択的に前記NビットΣΔ変調信号若しくは純ゼロ信号を出力して、出力信号とし、前記ローパスフィルタは前記出力信号に基づいてフィルタリングされた出力信号を生成し、及び前記D/A変換回路は、前記フィルタリングされた出力信号により前記アナログ出力信号を生成する。

(もっと読む)

1 - 20 / 141

[ Back to top ]