Fターム[5J064BC19]の内容

圧縮、伸長、符号変換及びデコーダ (21,671) | 細部(回路)構成 (8,519) | 増幅器(減衰器) (106)

Fターム[5J064BC19]に分類される特許

1 - 20 / 106

A/D変換器

【課題】任意のコモンモード電位の差動アナログ信号を入力でき、かつ任意のリファレンス電圧を設定可能なΔΣA/D変換器を提供する。

【解決手段】ΔΣA/D変換器のΔΣ変調器が有する(1ビットDAC+加算+積分)演算回路にて、オペアンプの正側入力ノード及び負側入力ノードに対してそれぞれ2つのリファレンス容量を設け、入力信号に変調器出力に応じた信号を加算又は減算する場合に、リファレンス容量の接続を正側入力ノード及び負側入力ノードにおいて相補的に切り替えることで、リファレンス電圧にかかわらずオペアンプの入力ノードに加算される電荷量を常に同一にして、オペアンプの入力ノードの電位が回路のコモンモード電位に収束するようにし、任意のコモンモード電位の差動アナログ信号を入力可能、かつ任意のリファレンス電圧を設定可能にする。

(もっと読む)

パラメータ復号装置およびパラメータ復号方法

【課題】予測量子化において主観品質の劣化を抑えるようにパラメータの補償処理を行うこと。

【解決手段】増幅器(305−1〜305−M)は入力した量子化予測残差ベクトルxn-1〜xn-Mに重み付け係数β1〜βMを乗算する。増幅器(306)は前フレームの復号LSFベクトルyn-1に重み係数β-1を乗算する。増幅器(307)はコードブック(301)から出力されたコードベクトルxn+1に重み係数β0を乗算する。加算器(308)は増幅器(305−1〜305−M)、増幅器(306)および増幅器(307)から出力されたベクトルの総和を計算する。切替スイッチ(309)は、現フレームのフレーム消失符号Bnが「第nフレームは消失フレームである」ことを示し、かつ、次フレームのフレーム消失符号Bn+1が「第n+1フレームは正常フレームである」ことを示す場合には、加算器(308)から出力されたベクトルを選択する。

(もっと読む)

AD変換装置および信号処理システム

【課題】ダイナミックレンジが歪みで制限されるAD変換の特性を大幅に改善することが可能なAD変換装置および信号処理システムを提供する。

【解決手段】入力アナログ信号をデジタル信号に変換する第1のアナログデジタル(AD)変換器11と、入力アナログ信号を係数αでα倍したアナログ信号をデジタル信号に変換する第2のAD変換器12と、第1のAD変換器の出力信号に係数αを2乗した値α2を掛け合わせる第1の演算器14と、第2のAD変換器の出力信号に係数αを−1乗した値α−1を掛け合わせる第2の演算器15と、第1の演算器の演算結果と第2の演算器の演算結果との差分をとり、入力信号のAD変換結果として出力する第3の演算器16とを有する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】デルタシグマ型A/D変換器のアナログ入力信号の切り換えが実行される際の安定化時間を短縮すること。

【解決手段】半導体集積回路のデルタシグマ型A/D変換器(12)のA/D変換動作は、制御回路(13)から供給される制御信号(Cnt2)によって制御される。アナログ入力信号(Vin)の切り換え実行時には、制御信号(Cnt2)に応答して積分器(1211)の演算増幅器(OPA)の出力電圧振幅が制限される振幅制限動作が実行される。例えば、信号切り換え実行時には、積分器(1211)の入力の信号伝達量または入力から出力への信号伝達量が、信号切り換え後の定常状態の信号伝達量よりも小さな値に設定される。半導体集積回路は、複数のアナログ入力端子に接続されたアナログマルチプレクサー(11)と、バスを介して制御回路(13)に接続された中央処理ユニット(21)を更に具備する。

(もっと読む)

デジタルアナログ変換装置

【課題】デジタル信号をアナログ信号に変換するデジタルアナログ変換装置を構成する素子にバラツキがあった場合においても、高い品質のアナログ信号を生成することができ、高分解能を有し、かつ、回路規模の小さいデジタルアナログ変換装置を実現する。

【解決手段】入力信号のビット数を低減するΔΣ変調器と、前記ΔΣ変調器の出力信号のフォーマットを変換するデータ変換器と、前記データ変換器の出力信号を遅延させる遅延器と、それぞれが3値信号を出力するスイッチング増幅器を有する複数の出力ユニットと、前記複数の出力ユニットの出力する3値信号それぞれを物理的な変位力に変換する複数の素子それぞれに供給し前記物理的変位力を合成して出力する電気−音響信号変換器と、前記複数の出力ユニットの選択の履歴に応じて選択する前記複数の出力ユニットへ前記遅延器の出力信号を出力する選択器を有する、音声再生用データ変換装置を提供する。

(もっと読む)

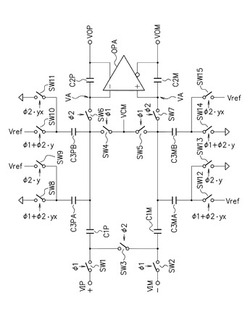

差動ΔΣ型AD変換器

【課題】キャパシタに矩形波を入力して減算する方式でありながら、差動入力ΔQが負の場合であっても測定可能な使い勝手の良い差動ΔΣ型AD変換器を提供すること。

【解決手段】この差動ΔΣ型AD変換器は、全差動回路1と、全差動回路の入出力端間に設けられた積分用キャパシタCi1,Ci2と、全差動回路1の後段に設けられたコンパレータ2と、全差動回路1の反転入力端子に接続された減算用キャパシタCaと、全差動回路1の非反転入力端子に接続された減算用キャパシタCbと、全差動回路1への差動入力のΔQが正の場合は、矩形波を反転せずに減算用キャパシタCaへ入力すると共に矩形波を反転させて減算用キャパシタCbへ入力し、ΔQが負の場合は、、矩形波を反転させて減算用キャパシタCaへ入力すると共に矩形波を反転せずに減算用キャパシタCbへ入力する。

(もっと読む)

符号化装置、復号化装置、およびこれらの方法

【課題】広帯域信号のスペクトルを符号化する際に、低ビットレート化を実現しつつ、原信号の高域スペクトルと新たに生成されるスペクトルとの類似度を向上させること。

【解決手段】取得手段は、少なくとも低域と高域とに分けられたスペクトルを取得し、第1の符号化手段は、低域のスペクトルを符号化して第1符号化情報を生成する。第1の復号手段は、第1符号化情報を復号して復号低域スペクトルを生成し、生成手段は、復号された低域スペクトルを複製して高域のスペクトルの形状を生成する。ゲイン算出手段は、高域のスペクトルを複数のサブバンドに分割し、各サブバンドのゲインを算出し、第2の符号化手段は、高域のスペクトルのサブバンドの内、少なくとも前記低域スペクトルに隣接する前記高域スペクトルのサブバンドを含む特定のサブバンドのゲインのみを符号化する。

(もっと読む)

デルタシグマ変調装置

【課題】消費電流及びノイズをバランス良く抑制しつつオフセット電圧の補正を行う。

【解決手段】サンプリング用キャパシタ(C1P、C1N9)への入力電圧(vin1、vin2)に応じた電荷の充電とサンプリング用キャパシタに蓄積された電荷の放電とを交互に繰り返すサンプリング回路(111a、111b)と、可変キャパシタ(C3P、C3N)への参照電圧に応じた電荷の充電と可変キャパシタに蓄積された電荷の放電とを交互に繰り返すオフセット補正電圧生成回路(102a、102b)と、サンプリング用キャパシタに蓄積された電荷並びに可変キャパシタに蓄積された電荷が積分用キャパシタ(C2P、C2N)に蓄積される積分回路113と、積分回路の出力電圧を量子化する量子化器と、量子化器から出力される量子化信号をデジタルアナログ変換して積分回路の入力に帰還させるデジタルアナログ変換器(105a、105b)と、制御回路と、を備えるデルタシグマ変調装置。

(もっと読む)

デジタル−アナログ変換器及びデジタル−アナログ変換装置

【課題】 簡単な回路構成で、スイッチのオン抵抗値によるアナログ出力信号の歪みやノイズの発生を防止することができるデジタル−アナログ変換器を提供する。

【解決手段】 サンプリング容量素子Ciの一方の端子と対応する入力端子Diとの接続及び切断並びにサンプリング容量素子Ciの他方の端子と第1基準電圧源B1との接続及び切断を切り替える第1のスイッチユニットSU1と、第1のスイッチユニットSU1の切り替えにおける切断及び接続に応じて、サンプリング容量素子Ciの他方の端子と演算増幅器2の反転入力端子との接続及び切断、複数のサンプリング容量素子Ciの一方の端子の相互の接続及び切断、並びに一方の端子が相互に接続されたサンプリング容量素子Ciの電圧に応じた電圧を演算増幅器2の出力端子に出力する電気経路の閉成及び開放を切り替える第2のスイッチユニットSU2と、電気経路に設けられた抵抗素子Rsとを備えている。

(もっと読む)

サブサンプリング技法を利用する受信器のデジタル処理構造

【課題】無線通信の送受信システムに係わるデジタル方式の受信器を提供する。

【解決手段】RF信号をIF信号又はDC信号に変換するサブサンプリングの際、要する信号帯域に対してはオーバーサンプリングして要らない信号もデジタル信号に変換させた後、デジタルブロックから効果的に除去する。本発明によると一般的なアナログ設計方式の受信器に比べて、フィルタ、LNA、そして、ADCだけでアナログ設計部が構成されるので、アナログ構成ブロックの構造が簡単になる。従って、ADCの後端に設置されるデジタル構成ブロック等の構造も最適化してデジタル方式の受信器を構成することができる。

(もっと読む)

ディジタルアナログ変換器

【課題】低消費電力で信号の歪みやSNR劣化が少ないディジタルアナログ変換器を提供する。

【解決手段】シフトレジスタSREG、1ビットディジタルΔΣ信号を入力し、一対の信号を出力するスイッチ回路SW1〜SW(N)、出力された一対の信号を入力して一対の信号として出力するインピーダンス素子IMP1〜IMP(N)、出力された一対の信号の一方を入力する反転入力端子OPAa、他方を入力する非反転入力端子OPAb、1ビットディジタルΔΣ信号をディジタルアナログ変換した信号を出力する出力端子102を備える演算増幅器OPA、反転入力端子OPAaと出力端子102とに接続されるインピーダンス素子IMP0−N、非反転入力端子OPAbに一端が接続され、他端に基準電圧が与えられるインピーダンス素子IMP0−Pによりディジタルアナログ変換器を構成する。

(もっと読む)

シグマデルタ変調器

【課題】DAC部の抵抗の寄生容量と電源回路との間で移動する電荷量を小さくするデルタシグマ変調器を提供する。

【解決手段】第1端子と第2端子とを有し前記第1端子を介して供給される電圧を積分する積分回路と、第1参照電圧を第1抵抗の一端に供給してその他端に得られる第1電圧を、前記第1端子または前記第2端子へ交互に供給する第1DAC部と、第2参照電圧を第2抵抗の一端に供給してその他端に得られる第2電圧を、前記第2端子または前記第1端子へ交互に供給する第2DAC部とを備え、前記第1DAC部が前記第1電圧を前記第1端子に供給するときには、前記第2DAC部は前記第2電圧を前記第2端子に供給し、前記第1DAC部が前記第1電圧を前記第2端子に供給するときには、前記第2DAC部は前記第2電圧を前記第1端子に供給するシグマデルタ変調回路を提供する。

(もっと読む)

部分的な複素変調フィルタバンク

【課題】高品質の操作を可能にする信号を出力するための効率的な概念と、歪が少ない状態で信号を削減するための効率的な概念とを提供する。

【解決手段】第1の実数サブバンド信号と第2の実数サブバンド信号とを含む複数の実数サブバンド信号を処理して少なくとも1つの複素サブバンド信号を提供する装置210であって、この装置は、実数中間サブバンド信号を出力するためのマルチバンドフィルタ204と、上記複数の実数サブバンド信号からの実数サブバンド信号と上記中間サブバンド信号とを結合することによって複素サブバンド信号を出力するための計算器215と、を備える。上記実数サブバンド信号の各信号に対し、その実数サブバンド信号に関連する中心周波数に従って指数mを割り当て、この指数mが増大するにつれて上記実数サブバンド信号をその信号に関連する中心周波数に従って配置する。

(もっと読む)

画像符号化復号化方法及び装置

【課題】安価で高速なDCTチップをそのまま使ってロッシー・ロスレス統合符号化を実現する。

【解決手段】ブロックと同じ大きさのゼロ行列であるサイド情報ブロックSxを準備する。リフティング構造の変換処理部25で、最初のブロックの入力信号X0をDCT-IIで変換し、サイド情報ブロックSxをDCT-IIIで変換する。次段のリフティング構造の変換処理部26で次のブロックの入力信号X1をDCT-IIで変換し、変換処理部25のサイド情報ブロックに対応する出力信号をDCT-IIIで変換する。以下順次同様の処理を実行し、各ブロックに対応する入力信号X0〜Xn-1をDCT-IIで変換したY0〜Yn-1を出力するとともに、サイド情報ブロックSxを繰り返しDCT-IIIで変換した信号Syを出力する。Syも用いて逆変換するとロスレスとなり、用いないとロッシーとなる。

(もっと読む)

積分器

積分器(100)が、増幅および位相シフト要素(170)を備え、フィードバック経路(130)がループを形成し、容量性素子(140)を含む。ループ内に入力信号が加算され、ループは、入力信号の着目する周波数より高い発振周波数で発振するように配設される。ループは、増幅および位相シフト要素(170)が入力信号に増幅を確実に与えうるように、発振信号を減衰するためのフィルタ(160)を含む。入力信号は積分され、積分された信号は発振信号のゼロ交差を摂動する。  (もっと読む)

(もっと読む)

量子化装置、再生装置、量子化方法およびプログラム

【課題】量子化処理の時間を削減する。

【解決手段】量子化装置15の量子化部43は、量子化パラメータを用いて、信号のサンプリングデータから量子化データを生成し(ST18)、量子化データを符号化した符号化データのビット数をカウントし(ST20)、カウント値と量子化の目標ビット数とを比較し(ST21,ST24)、量子化部が量子化に用いる量子化パラメータを修正し(ST22,ST25)、カウント値が目標ビット数に対して所定の収束状態になるまで、量子化パラメータを修正して一連の量子化処理を繰り返す。また、量子化部43は、新たな信号のサンプリングデータについての量子化処理を開始する場合に、量子化部43が以前の信号のサンプリングデータの量子化処理において用いた旧量子化パラメータを、量子化パラメータの初期値として用いる(ST13)。

(もっと読む)

データ変換処理装置およびデータ変換処理方法

【課題】 画像データの符号化及び復号の両方に共通して使え、ロッシ−・ロスレス符号化復号半2重システムを低コストで実現する。

【解決手段】 N個の入力データを、N次元空間上で回転変換する装置であって、特定の1つのデータを除くN−1個のデータ毎に第1と第2の重み係数が定められており、前記特定の1つの入力データにN−1個の第1の重み係数を乗じた結果を、対応するN−1個の入力データに加減算する第1群リフティング演算部1010と、第2の重み係数を、第1群リフティング演算出力のN−1個のデータに乗じ、N−1個の乗算結果を前記特定の1つのデータに加減算する第2群リフティング演算部1020と、第1の重み係数を、第2群リフティング演算出力の特定の1つのデータに乗じ、N−1個の乗算結果を対応するN−1個のデータに加減算する第3群リフティング演算部1030を有する。

(もっと読む)

ΔΣ変調器

【課題】量子化器入力部での信号振幅の増大を抑えつつ補正することができ、内部DA変換器を省略することができ、回路全体の低消費電力化を達成することが可能なΔΣ型変調器を提供する。

【解決手段】少なくとも一つの積分器INT11と、積分器INT11の出力信号を量子化してデジタル信号を出力する量子化器Quan11と、内部のループ遅延に起因して発生する非理想的特性を補償する補償部と、補償部が、量子化器Quan11の出力端子から量子化器直前の積分器INT11の入力端子に周波数特性を持たない帰還経路により形成されている。補償部は、量子化器Quan11によるデジタル信号をアナログ信号に変換するデジタルアナログ(DA)変換器DAC11と、DA変換器の出力端子に直列に接続された容量CDACと、を含み、ループ遅延に起因する入出力間伝達特性の非理想性を補償する機能を有する。

(もっと読む)

EEGモニタリング・システムのための入力変換器,信号変換方法およびモニタリング・システム

モニタされるべき人物によって連続して持ち運ばれることができるEEGモニタリング・システム(40)における雑音および電流消費を最小化するために,EEGモニタリング・システム用の入力変換器(44)が案出される。上記入力変換器のアナログ−ディジタル変換器は,入力段,出力段およびフィードバック・ループを備え,上記入力段は増幅器(QA)および積分器(RLF)を備える。変圧器(IT)が上記入力変換中の上記入力段の上流に配置される。上記変圧器(IT)の変換比はその入力電圧よりも大きな出力電圧を供給する変換比を持ち,これにより,上記入力段についての信号電圧に固定係数が乗算される。上記変圧器(IT)は少なくとも2つのキャパシタ(Cx,Cy,Cz)を有するスイッチング・キャパシタ変圧器である。この発明はさらにアナログ信号を変換する方法,および上記入力変換器(44)を備えるEEGモニタリング・システムを提供する。  (もっと読む)

(もっと読む)

音信号加工装置及び音信号加工方法

【課題】量子化雑音などの劣化音を含む入力音信号に対して、主観的に劣化音を感じにくく加工する音信号加工方法および音信号加工装置を提供する。

【解決手段】入力音信号としての復号音声の聴覚重み付け後のスペクトルを変形強度制御部で算出、その振幅の大きさ、スペクトルの連続性に基き、変形強度を算出する。信号変形部で、復号音声のスペクトルを求め、変形強度に基き振幅平滑化、位相擾乱付与を行い、信号領域に戻して変形復号音声とする。信号評価部で、復号音声を分析し背景雑音らしさを求め、これを加算制御値とする。重み付き加算部で、加算制御値が背景雑音らしいことを示す場合には、復号音声への重みを減らし、変形復号音声への重みを増やして加算し、出力音声とする。

(もっと読む)

1 - 20 / 106

[ Back to top ]