Fターム[5J079FB12]の内容

電気機械共振器を用いた発振回路 (23,106) | 回路要素 (2,263) | 共振回路、共振器(振動子以外) (37)

Fターム[5J079FB12]に分類される特許

1 - 20 / 37

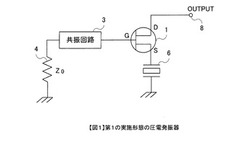

圧電発振器

【課題】 反射素子の反射特性を用いて高周波化、周波数安定化を図ることができる圧電発振器を提供する。

【解決手段】 電界効果型のトランジスタ1のゲートに共振回路3が接続され、ドレインに出力端子7が接続されると共に、電源電圧Vが印加され、ソースに反射素子として圧電共振器6が接続され、共振回路3の共振周波数と反射素子の圧電共振器6の発振周波数とを略同じにした圧電発振器であり、共振回路3とゲートとの間に第1のマッチング回路2と、ドレインと出力端子8との間に第2のマッチング回路7と、ソースと反射素子との間に第3のマッチング回路5を設けるようにしてもよいものである。

(もっと読む)

発振器

【課題】消費電流を増大させることなしに高速起動可能なMEMS発振器の提供。

【解決手段】ドライバアンプと、LC共振回路を備える第1共振器と、MEMS共振器を備える第2共振器と、接続および開放を切り換え可能なスイッチ回路と、スイッチ回路を制御するスイッチ制御部と、を有するMEMS発振器であって、ドライバアンプ、第1共振器、および、スイッチ回路は、ドライバアンプの出力信号の少なくとも一部をドライバアンプへ帰還させる第1閉ループ回路を形成し、ドライバアンプ、および、第2共振器は、第1閉ループ回路とは別の、ドライバアンプの出力信号の少なくとも一部をドライバアンプへ帰還させる第2閉ループ回路を形成し、スイッチ制御部は、MEMS発振器の起動期間の少なくとも一部においてスイッチ回路を接続し、所定の条件が満たされる場合に、スイッチ回路を開放する、MEMS発振器。

(もっと読む)

発振器

【課題】純度の高い正弦波を出力するようにして、位相雑音を低減できる発振器を提供すること。

【解決手段】トランジスタ3を増幅部として用いたコルピッ型発振回路において、発振ループの外または中に波形整形用の水晶振動子5を設ける。そして発振用の水晶振動子1と波形整形用の水晶振動子5とは、共通の水晶片10に、電極対(11、12)及び電極対(51、52)を設けて構成する。水晶振動子1の電極11(12)と水晶振動子5の電極51(52)とは離間距離を大きくして互に弾性的に結合しないか、結合してもその程度が弱いようにすると共に、水晶振動子5の並列容量に対して並列共振を起こすインダクタを設ける。水晶振動子5と波形整形用の水晶振動子1とを、共通の圧電片を用いたSAW共振子として入れ替えた構成としてもよい。

(もっと読む)

発振器

【課題】 MEMS共振器を用いた発振器において、TIAの雑音の影響を低減し、発振器出力の位相雑音特性を改善することができる発振器を提供する。

【解決手段】 MEMS共振器7と、TIA5と、バッファアンプ9とを備えた発振器において、MEMS共振器7の出力をTIA5に入力する配線15に、電磁誘導により結合して、当該配線15を流れる電流を電圧に変換してバッファアンプ9に出力する電流/電圧変換器を備え、発振器出力を電流/電圧変換器から取り出すようにした発振器であり、また、当該電流/電圧変換器を、配線15を非接触に取り囲むように形成され、一端が接地され他端がバッファアンプ9に接続する発振出力コイル11とした発振器である。

(もっと読む)

圧電発振回路

【課題】 高周波領域で少ない部品数で大きな負性抵抗が得られ、安定した発振を実現できる圧電発振回路を提供する。

【解決手段】 第1のトランジスタQ1のベースに水晶振動子X1が接続され、第1のトランジスタQ1のコレクタに第2のトランジスタQ2のエミッタを接続してカスケード接続を構成し、更に第2のトランジスタQ2のコレクタから第1のトランジスタQ1のエミッタにコンデンサC3又は抵抗R7を介して帰還接続し、第2のトランジスタQ2のコレクタには電源電圧Vccが負荷抵抗R6を介して印加される圧電発振回路である。

(もっと読む)

高周波コルピッツ回路

【課題】 高周波においても安定した発振を実現でき、回路規模を小さくできる高周波コルピッツ回路を提供する。

【解決手段】 発振用のトランジスタQ1に加え、帰還用のトランジスタQ2を設け、トランジスタQ1のコレクタがトランジスタQ2のベースに接続し、トランジスタQ2のコレクタには電源電圧が抵抗R5を介して印加されると共に出力端子に接続され、当該コレクタが帰還抵抗Rfを介してトランジスタQ1のベースに接続され、当該ベースには、水晶振動子、直列接続のコンデンサC1とコンデンサC2の一端が接続され、他端が接地され、トランジスタQ1のエミッタには、コンデンサC1とコンデンサC2との間の点が接続されると共に、抵抗R4を介して接地される高周波コルピッツ回路である。

(もっと読む)

副振動抑圧型の水晶発振回路

【課題】特にSCカットでのBモードを抑圧してCモードでの発振を確実にし、しかも部品点数を少なくした水晶発振回路を提供する。

【解決手段】水晶振動子3と第1及び第2コンデンサC1、C2とからなる発振用共振回路1と発振用トランジスタ2とを有し、ベース・コレクタ間に水晶振動子3を、エミッタ・コレクタ間に第1コンデンサC1を、エミッタ・ベース間に第2コンデンサC2を接続したコルピッツ型で、発振用トランジスタ2のエミッタ・コレクタ間又はエミッタ・ベース間は第1又は第2コンデンサC1、C2にLC直列回路4を並列接続したリアクタンス並列回路5からなり、リアクタンス並列回路5は主振動モードによる発振周波数f1oでは容量性となる共振特性を有し、LC直列回路4の共振周波数frは副振動モードによる振動周波数fo2に一致した構成とする。

(もっと読む)

水晶発振回路

【課題】 複数の異なる周波数信号を出力可能で、消費電力を低減し、構造が簡易で小型化できる水晶発振回路を提供する。

【解決手段】 電圧制御水晶発振器(VCXO)2からの出力を分周比に応じて分周器3で分周し、分周された信号とVCXO2から出力された信号を合成器4で合成し、予め分周比に応じて通過帯域が定められた複数のBPF5に出力し、該当するBPFのみが特定の周波数帯域の信号を通過させ、PLL6で位相制御が為されて、所望の周波数信号を出力する水晶発振回路である。

(もっと読む)

電圧制御型発振器

【課題】許容される制御電圧の調整範囲に対応した発振周波数可変域の範囲を拡大した電圧制御型発振器を提供する。

【解決手段】圧制御型発振器は、振動子1と、該振動子の振動出力を入力として所定周波数で発振する発振回路3と、一端に電圧制御端子6を有し、他端を振動子1に直列接続した周波数制御回路2を備える。周波数制御回路2は、電圧制御端子6に接続された抵抗素子Rと、該抵抗素子と振動子の間に一端が接続された振動域伸張用コイルLと容量素子Cvで構成された並列共振回路と、並列共振回路の他端と抵抗素子Rの接続部にカソードを接続し、アノードを接地に接続した可変容量ダイオードDとを有する。電圧制御端子6に印加する制御電圧に応じた可変容量ダイオードDの容量変化による振動子1から見た並列共振回路の回路容量の変化を用いて発振回路3に入力する周波数範囲を可変する。

(もっと読む)

圧電発振器

【課題】圧電発振器の低電源電圧化に対応可能とすると共に、安定した性能を有する圧電

発振器を提供することを目的とする。

【解決手段】圧電発振器1は、コルピッツ型の発振回路2と、発振回路2が出力する発振

信号より基本波周波数を濾波し、即ち通過させるフィルタ回路3と、発振回路2とフィル

タ回路3との間に接続されたダイオードD1とにより構成し、圧電発振器1には、ノイズ

を除去するためのバイパスコンデンサC5を介して電源電圧(Vcc)を印加している。

本発明においては、発振回路2とフィルタ回路3とをダイオードD1を経由して接続した

。

(もっと読む)

異常検出装置およびこれを備える電子機器

【課題】 内部電源が故障して内部発振回路が停止した場合にも、内部発振回路の異常を検出できる異常検出装置およびこれを備える電子機器を提供することである。

【解決手段】 異常検出装置10は、内部発振回路17と、監視回路19と、異常監視部21とを含み、内部発振回路17は、外部発振子12の発振状態を監視するための基準となる発振を行う。監視回路19は、外部電源22から電力供給を受けて稼動し、内部発振回路17の発振に基づいて、外部発振子12の発振を監視する。異常監視部21の少なくとも一部は、外部電源22から供給される電力によって稼動し、異常監視部21は、内部発振回路17に接続される。異常監視部21には、内部発振回路17から出力される発振が入力され、異常監視部21は、内部発振回路17の発振をカウントするカウンタ回路24を含む。

(もっと読む)

発振器

【課題】水晶振動子を使った発振器の起動特性を向上させる。

【解決手段】第1の端子と、第2の端子と、第1の端子と第2の端子との間に、直列に接

続された抵抗素子及びインダクタと、抵抗素子と並列に接続された振動子と、第1の端子

と第2の端子との間に接続されたコンデンサと、第1の端子と第2の端子との間に接続さ

れ、振動子を振動させる発振回路部と、を含み、インダクタの値と抵抗素子の抵抗値と振

動子の等価直列インダクタの値と振動子の等価直列抵抗の抵抗値とは、(インダクタの値

÷抵抗素子の抵抗値)<(振動子の等価直列インダクタの値÷振動子の等価直列抵抗の抵

抗値)の関係を満たす、ことを特徴とする発振器。

(もっと読む)

発振器

【課題】水晶振動子を使った発振器の起動特性を向上させる。

【解決手段】第1の端子と、第2の端子と、第1の端子と第2の端子との間に、直列に接続された抵抗素子及びインダクタと、抵抗素子と並列に接続された振動子と、第1の端子と第2の端子との間に接続されたコンデンサと、第1の端子と第2の端子との間に接続され、振動子を振動させる発振回路部と、を含み、インダクタの値と抵抗素子の抵抗値と振動子の等価直列インダクタの値と振動子の等価直列抵抗の抵抗値とは、(インダクタの値÷抵抗素子の抵抗値)<(振動子の等価直列インダクタの値÷振動子の等価直列抵抗の抵抗値)の関係を満たす、ことを特徴とする発振器。

(もっと読む)

表面波共振回路用作動回路及びそれを用いた発振回路

【課題】約百ナノ秒のオーダーで、瞬時に発振を起動することができる表面波共振回路用作動回路と、その表面波共振回路用作動回路を用いた発振回路を提供する。

【解決手段】表面波共振回路(X1)の作動回路は、静電キャパシタ(Co)と、表面波共振回路(X1)に電圧(Vx)を加える作動回路とを備えている。作動回路は、前記電圧(Vx)が加わえられた前記共振回路(X1)の作動期間の初期に、既定の周波数(Fo)において、前記静電キャパシタ(Co)と協働して共振する反動手段(L3)と、前記既定の周波数(Fo)での発振を決定する受動手段(R3)とを備えている。

(もっと読む)

発振回路、発振器

【課題】発振に必要な負性抵抗を小さくすると同時に回路の低消費電力を図ることのでき

る発振回路及び発振器を提供する。

【解決手段】発振回路10は、トランジスタM1とトランジスタM2とが差動接続される

クロスカップル型回路からなり、振動子SAWの共振点帯域で発振する。トランジスタM

1は第1ソース負荷回路としての抵抗器RL1に接続され、トランジスタM2は第2ソー

ス負荷回路としての抵抗器RL2に接続されている。また、トランジスタM1は第1ドレ

イン負荷回路としての抵抗器Rs1に接続され、トランジスタM2は第2ドレイン負荷回

路としての抵抗器Rs2に接続されている。第1ソース負荷回路のインピーダンスの大き

さが第1ドレイン負荷回路のインピーダンスの大きさ以上であり、且つ、第2ソース負荷

回路のインピーダンスの大きさが第2ドレイン負荷回路のインピーダンスの大きさ以上と

する。

(もっと読む)

圧電発振器

【課題】被覆材を用いて振動子電極を両面とも絶縁することなく直接液体に浸漬可能で、液相中・気相中を問わず安定して発振可能な圧電発振器を提供する。

【解決手段】所定の周波数で励振される圧電振動子Zxtと、圧電振動子Zxtを励振させる論理素子INVと、圧電振動子Zxtに並列接続される容量素子Ceと、論理素子INVの出力に接続される第1のインダクタz2および第1のパスコンデンサCp1と、論理素子INVの入力に接続される第2のインダクタz3および第2のパスコンデンサCp2と、を備え、論理素子INVの出力より第1のインダクタz2を介して接地すると共に、論理素子INVの入力より第2のインダクタz3を介して接地することにより、容量素子Ceと第1のインダクタz2と第2のインダクタz3とが、圧電振動子Zxtの発振周波数において共振するタンク回路を構成する。

(もっと読む)

発振器

【課題】 従来、発振周波数を選択するための負性抵抗の調整は製造段階で行うのみであって、経時変化に対応した調整は不可能であるという問題点があり、簡易な構成で、周波数選択特性を経時変化に応じて容易に調整することができる発振器を提供する。

【解決手段】 発振回路の周波数を選択可能な帰還ループに、インダクタンスLとバリキャップダイオードC3とを直列に接続した周波数選択回路10を設け、バリキャップダイオードC3の容量を電気的に制御することにより、負性抵抗を調整する発振器である。

(もっと読む)

発振装置

【課題】従来の発振装置では、負性抵抗は、比較的小さい値であった。

【解決手段】PNP型トランジスタと、NPN型トランジスタと、水晶振動子と、第1のキャパシタと、第2のキャパシタと、を含み、PNP型トランジスタのエミッタが、電源電位に接続されており、NPN型トランジスタのエミッタが、接地電位に接続されており、第1のキャパシタの一端が、接地電位に接続されており、第2のキャパシタの一端が、接地電位に接続されており、PNP型トランジスタのベース、NPN型トランジスタのベース、第1のキャパシタの他端、及び、水晶振動子の一端が相互に接続されており、PNP型トランジスタのコレクタ、NPN型トランジスタのコレクタ、第2のキャパシタの他端、及び、水晶振動子の他端が相互に接続されている。

(もっと読む)

発振装置

【課題】低電圧での動作が可能であり、また、トランジスタのベース電圧を安定化させることができるものの、負性抵抗が、比較的小さかった。

【解決手段】発振装置は、コレクタが電源電位に接続された第1のNPN型トランジスタと、第2のNPN型トランジスタと、前記第1のNPNトランジスタのエミッタ及び接地電位間に設けられた第1のキャパシタと、前記第2のNPN型トランジスタのベース及び前記接地電位間に設けられた第2のキャパシタと、前記第1のNPN型トランジスタのベース及びエミッタ間に設けられた第3のキャパシタと、前記第2のNPN型トランジスタのコレクタ及び前記電源電位間に設けられた第1の抵抗器と、前記第1のNPN型トランジスタのエミッタ及び前記第2のNPN型トランジスタのベース間に相互に並列接続された第2の抵抗器及び発振振動子と、を含む。

(もっと読む)

複合共振回路とそれを用いた発振回路

【課題】一般的な共振回路において可変キャパシタンス素子や可変インダクタンス素子を使用することなく、発振周波数やフィルタの周波数特性を制御し得る共振回路、及びかかる共振回路を使用した発振回路やフィルタ等を提供する。

【解決手段】増幅器の入力及び出力の間に互いに独立な正及び負帰還路を有し、該負帰還路に可変反周波数特性を有する反共振回路を含み、該正帰還路に前記反共振回路の反共振周波数の変化に追従する中心周波数において最大ゲインを有する可変帯域増幅器を含む発振回路。

(もっと読む)

1 - 20 / 37

[ Back to top ]