Fターム[5J079GA17]の内容

電気機械共振器を用いた発振回路 (23,106) | 発振のための増幅部の構成 (697) | 増幅部の変更、制御 (110) | 増幅要素の増減 (22) | 直列 (11)

Fターム[5J079GA17]に分類される特許

1 - 11 / 11

発振器

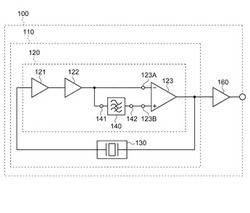

【課題】異常発振を抑圧する発振器を提供する。

【解決手段】発振信号を起動および増幅する増幅部120と、所望の発振周波数を決定する共振部130と、を備えた発振回路110と、発振回路110の出力端子に緩衝回路160が接続された発振器100であって、増幅部120は入出力用の2端子を有する低域濾波器140と、3段の増幅回路とを有し、増幅部120の1段目増幅器121と2段目増幅器122とが不平衡型増幅器で、3段目増幅器123がオペアンプであり、2段目増幅器122の出力端子が、低域濾波器140の入力端子と3段目増幅器(オペアンプ)123の反転入力端子に接続され、低域濾波器140の出力端子が、3段目増幅器(オペアンプ)123の非反転入力端子に接続されている。

(もっと読む)

電子装置およびその製造方法、並びに発振器

【課題】高い信頼性を有する電子装置を提供する。

【解決手段】本発明に係る電子装置100は、基板10と、基板10の上方に形成された機能素子20と、機能素子20が配置された空洞部1を画成する包囲壁40と、基板10の上方に形成され、機能素子20に接続された配線層30,32と、を含み、配線層30,32は、基板10と包囲壁40との間を通って、包囲壁40の外側まで延出され、包囲壁40は、窒化シリコン層42と、金属層およびシリコン層の少なくとも1層である導電層と、を有し、配線層30,32と導電層44との間には、窒化シリコン層42が配置されている。

(もっと読む)

MEMS発振器及びその製造方法

【課題】製品として求められる目標精度に比べて梁の膜厚ばらつきに起因する共振周波数のばらつきが大きくても、目標精度内の共振周波数を有するMEMS振動子を高い歩留りで得られるMEMS発振器を提供する。

【解決手段】本発明の一態様は、基板上に形成された複数のMEMS振動子10a〜10dと、前記複数のMEMS振動子のいずれか一つのMEMS振動子に電気的に接続され、且つ前記複数のMEMS振動子のうち前記一つのMEMS振動子以外の全てのMEMS振動子に電気的に接続されていない発振回路2とを具備し、前記複数のMEMS振動子それぞれは、梁構造を有しており、前記複数のMEMS振動子は、それぞれの梁構造が異なることによって共振周波数が異なるMEMS発振器である。

(もっと読む)

高周波コルピッツ回路

【課題】 高周波においても安定した発振を実現でき、回路規模を小さくできる高周波コルピッツ回路を提供する。

【解決手段】 発振用のトランジスタQ1に加え、帰還用のトランジスタQ2を設け、トランジスタQ1のコレクタがトランジスタQ2のベースに接続し、トランジスタQ2のコレクタには電源電圧が抵抗R5を介して印加されると共に出力端子に接続され、当該コレクタが帰還抵抗Rfを介してトランジスタQ1のベースに接続され、当該ベースには、水晶振動子、直列接続のコンデンサC1とコンデンサC2の一端が接続され、他端が接地され、トランジスタQ1のエミッタには、コンデンサC1とコンデンサC2との間の点が接続されると共に、抵抗R4を介して接地される高周波コルピッツ回路である。

(もっと読む)

水晶発振器

【課題】回路構成を簡易にして、起動特性及びデューティー比を良好に維持した水晶発振器を提供する。

【解決手段】発振段におけるCMOSからなる発振インバータ1の出力に同じくCMOSからなる伝達インバータ2を接続した水晶発振器において、伝達インバータ2には、発振インバータ1の起動時よりも伝達インバータ2が遅れて起動する、スイッチング素子5とスイッチング素子の導通を発振インバータの起動時よりも遅らせるタイマー回路6とからなるスイッチングタイマー回路4が設けられる。このような構成であれば、発振段の起動直後(電源投入直後)、伝達インバータが起動しないので、発振段の発振成長の初期過程にある微少振幅信号は、伝達インバータの次段回路に送出されない。したがって、発振インバータでの水晶発振は後段回路の影響を受けることなく安定して増加することができる。

(もっと読む)

発振回路

【課題】 容量性回路の発振限界を超えた発振が可能であることを理論的に明確にすると共に、具体的回路例を提供する。

【解決手段】 キャパシタが直列接続された圧電振動子と、圧電振動子に並列接続されたインバーターと、インバーターの出力端子にベースが接続されたトランジスタとを含み、インバーターの入力端子と出力端子との間に抵抗が、インバーターの入力端子と接地との間にキャパシタが接続され、トランジスタのベースとエミッタとの間にキャパシタが、トランジスタのエミッタと接地との間に抵抗が、トランジスタのエミッタと接地との間にキャパシタの並列回路が、トランジスタのコレクタと電源との間に抵抗が接続され、インバーターの電源端子は電源に、接地端子は接地に接続され、電源と接地との間には、パスキャパシタが接続され、トランジスタのコレクタを出力とする。

(もっと読む)

圧電発振回路

【課題】 圧電素子を用いた発振回路で起動時間の早い圧電発振回路が求められていた。

【解決手段】 本発明は、圧電素子と、発振回路からなる圧電発振回路において、発振開始時に使用する起動発振用回路と定常時に使用する定常発振用回路とを持ち、発振開始時に使用する起動発振用回路と定常時に使用する定常発振用回路とを切り替える切り替え回路を備え、起動時と定常時とを判断する判断回路を備えた圧電発振回路により、より早い起動特性を得ている。

(もっと読む)

自励発振回路

【課題】簡素な回路構成により、低消費電流化、低ノイズ化及び発振位相安定度の向上が可能な自励発振回路を実現する。

【解決手段】振動式センサの振動子を自励発振させる自励発振回路において、圧力を検出する振動子を有する振動式センサと、振動式センサからの出力を受ける差動増幅回路と、第1のエミッタフォロア回路と第2のエミッタフォロア回路とから構成され、振動式センサからの出力電圧を出力電流に変換するトランスコンダクタンスアンプとして動作する発振回路とを備える。

(もっと読む)

低消費電力回路

【課題】 起動動作時における電流の増大を必要最小限に抑え、安定した起動動作が可能で、小型な低消費電力回路を提供する。

【解決手段】 カレントミラー回路M1と、カレントミラー回路M1の出力端に一端を接続した第1分割抵抗R1、この第1分割抵抗R1に一端を接続した第2分割抵抗R2との直列回路からなるバイアス分割回路R12と、第1分割抵抗R1の一端に制御端子(ゲート端子)を、第2分割抵抗R2の他端に第2主電流端子を、GNDに第1主電流端子を接続した第1トランジスタN1と、第2分割抵抗R2の他端に制御端子(ゲート端子)を、カレントミラー回路M1の入力端に第2主電流端子を、第2主電源GNDに第1主電流端子を接続した、第1トランジスタN1と同一チャネル導電型の第2トランジスタN2とを含み、起動時に第1分割抵抗R1と第2分割抵抗R2との接続ノードに起動電流ISTを印加する。

(もっと読む)

ピアース型発振回路

【課題】確実な発振動作を得るとともに、高周波数帯で発振の実現と、周波数安定度がより高いピアース型発振回路を提供する。

【解決手段】反転増幅回路と、この反転増幅回路の出力回路と入力回路の間に圧電振動子を設けたピアース型発振回路において、

反転増幅回路は、水晶振動子を通した入力を反転増幅するエミッタ接地型のトランジスタQ1と、このトランジスタのコレクタと出力回路との間でカスコード接続され、該トランジスタQ1のコレクタからみて低入力インピーダンスを呈し、かつ出力回路からみて高出力インピーダンスを呈するベース接地型のトランジスタQ2で構成する。R2は負帰還抵抗。

(もっと読む)

発振回路および発振用集積回路

【課題】 圧電振動子の等価並列容量の中和を実現し、安定した発振起動性を得るとともに、大きな周波数可変量を確保する。

【解決手段】 水晶振動子1を反転増幅器2の入力端子IN、出力端子OUT間に接続してコルピッツ型の発振回路を構成し、反転増幅器45の入力端子を容量5を介して出力端子OUTに接続し、その出力端子を容量46を介して入力端子INに接続してミラー容量回路4を構成し、水晶振動子の両端に等価的に存在する並列容量を電気的に中和する。

(もっと読む)

1 - 11 / 11

[ Back to top ]