Fターム[5J081EE06]の内容

LC分布定数、CR発振器 (9,854) | 周波数決定素子 (1,325) | 分布定数 (166)

Fターム[5J081EE06]の下位に属するFターム

Fターム[5J081EE06]に分類される特許

1 - 13 / 13

発振回路

【課題】簡易な方法で、特性の劣化を抑制し発振周波数を調整することが可能な発振回路を提供すること。

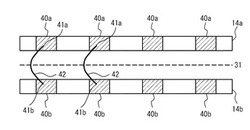

【解決手段】一対の負性抵抗回路と、前記一対の負性抵抗回路にそれぞれ接続された一対の伝送線路14a、14bと、前記一対の伝送線路にそれぞれ対称に設けられ、前記一対の伝送線路の間をボンディングワイヤによって互いに接続可能な一対のパッド40a、40bと、前記一対の負性抵抗回路の出力信号を合成する合成回路と、を有する発振回路。

(もっと読む)

アンテナとそれを用いた発振器

【課題】所望の周波数、特に100GHz以上のテラヘルツ帯において共振特性を良好とする新規なアンテナ及びそれを用いた発振器を提供する。

【解決手段】スロットアンテナは、スロットアンテナ本体2となる空隙と、この空隙に対して十字となるように空隙の長手方向に対して垂直方向に一つ以上設けたスリットリフレクタ部3となる空隙とが、導電性平板5に形成されて成り、所望されるインピーダンス又はアドミタンスの周波数特性が得られるようにスリットリフレクタ部3の配置場所、長さ及び幅が定められている。

(もっと読む)

2出力直交ローカル信号発振器

【課題】90°の位相差を持つ2つのローカル信号を発生するローカル信号源として使用可能な2出力直交ローカル信号発振器の提供。

【解決手段】第1及び第2のトランジスター14及び15を有し、共振器20を共有することにより、基本発振周波数にてプッシュ−プッシュ発振動作を行い、第1及び第2のトランジスターの一方から第1のローカル信号を出力する第1のプッシュ−プッシュ型発振器18と、第3及び第4のトランジスター16及び17を有し、共振器20を共有することにより、前記基本発振周波数にてプッシュ−プッシュ発振動作を行い、第3及び前記第4のトランジスターの一方から第2のローカル信号を出力する第2のプッシュ−プッシュ型発振器19とを有し、第1及び第2のプッシュ−プッシュ型発振器は、共振器の直交共振モードによって直交発振動作を行い、90°の位相差のある直交ローカル信号を出力することを特徴とする2出力直交ローカル信号発振器。

(もっと読む)

高周波発振器

【課題】高価な誘電体共振器やバラクタダイオードを使用することなく、廉価に制作することができ、また回路面積が小さく小型化が可能となるようにする。

【解決手段】誘電体基板1上に形成されたマイクロストリップ線路2において、増幅素子3の入力端のゲートが入力端側線路2aに接続され、出力端のドレインが出力端側線路2bに接続され、ソースが接地電極5に接続される。そして、上記誘電体基板1の裏面の接地面7の中に、空地領域7Eを介して線状の金属パターン8を形成し、この金属パターン8をマイクロストリップ線路2の伝送線路方向に配置することで、この金属パターン8の一方端を入力端側線路2a、他方端を出力側線路2bに容量性結合する。この金属パターン8の結合は、一端のみでもよい。これによれば、増幅素子3からの出力が、容量C1、インダクタンスL、容量C2を通って入力端へ帰還し、発振が行われる。

(もっと読む)

発振器

【課題】周波数を高くしても分布定数線路の線路長を長くできてQ値を向上できるとともに、製造誤差を小さく抑えることができる発振器を提供する。

【解決手段】1波長の線路長であって、両端をグランドに接地した分布定数線路16を有し、この分布定数線路16の一端から1/4波長の位置に設けた第1の中間タップに発振トランジスタ27のべースを接続するようにした。これにより、分布定数線路16の線路長が従来の1/4波長の線路長の分布定数線路より長くなり、その分Q値の向上が図れるとともに、製造誤差を小さく抑えることが可能となる。分布定数線路16の長さを1/2波長としても従来の1/4波長の長さの分布定数線路に比べて2倍長くできる。このようにしてもQ値の向上が図れ、また製造誤差を小さく抑えることが可能となる。

(もっと読む)

低ノイズ発振器

発振器は、トランジスタと、トランジスタの出力とトランジスタの制御電極との間に結合されている共振回路と、トランジスタのdcバイアス回路とを有する。dcバイアス回路は、第1電圧生成回路と、差動増幅器とを備えている。差動増幅器は、固定基準電圧に結合されている第1入力と、電圧生成回路に結合されている第2入力と、トランジスタの制御電極に結合されている出力とを含む。電圧生成回路は、差動増幅器の第2入力に、トランジスタの出力電極を通過する電流に関係する電圧を生成する。 (もっと読む)

2倍波発信器

【課題】回路全体の物理的サイズを変えることなく、かつ位相雑音を劣化させることなく出力電力を向上させることができる2倍波発振器を得る。

【解決手段】直列正帰還構成であり、かつ基本波信号の出力を抑制して回路内部で発生した1GHz以上200GHz以下の2倍波信号を出力する2倍波発振器であって、ベース端子、第1及び第2のエミッタ端子、並びにコレクタ端子を有するトランジスタ1と、前記ベース端子に接続された共振回路2と、2つのエミッタ端子のうちの一方に接続されたマイクロ波線路ショートスタブ3と、2つのエミッタ端子のうちの他の一方に接続され、線路長が基本波信号の半波長の整数倍に前記基本波信号の波長の4分の1を加えた長さであるマイクロ波線路ショートスタブ6とを設けた。

(もっと読む)

高周波発振器

【課題】高周波発振器全体の物理的サイズを変えることなく、且つ位相雑音特性を劣化せずに出力電力が増大する高周波発振器を提供する。

【解決手段】高周波発振器は、能動素子(5)の出力側の信号線路に基本波反射スタブ(9)を取り付けた高調波取り出し型の高周波発振器において、上記基本波反射スタブ(9)と出力端子(4)の間に介設され、高調波出力端子側負荷インピーダンスを高調波出力電力が最大になる予め求められた最適値に変換する高調波インピーダンス変換回路(3)を備える。

(もっと読む)

電圧制御発振器

【課題】ゲート制御電圧の範囲を精度良くかつ容易に調整することができる電圧制御発振器を提供する。

【解決手段】容量遷移制御電圧を印加するボディ端子領域tbdが制御電極Gの下部領域となるボディ領域に形成されている第1及び第2MOS可変容量素子C1a,C2aと、第1及び第2インダクタL1,L2と、クロスカップル型に組まれている第1及び第2MOSトランジスタM1,M2と、第1基準電圧源に結合される第1結合点n1と、第2基準電圧源に結合される第2結合点n2とを有する。第1及び第2MOS可変容量素子は、それぞれ、制御電極が制御電圧端子TVc1に共通に接続され、さらに、第1及び第2主電極S,Dが共通接続部sdで互いに接続されている。第1及び第2MOS可変容量素子の共通接続部は、それぞれ、対応する第1または第2インダクタを介して、第1結合点に結合されているとともに、対応する第1または第2MOSトランジスタを介して、第2結合点n2に結合されている。

(もっと読む)

ユーザ指定可能、低コスト、低ノイズであり、位相跳躍に影響されにくいマルチオクターブ帯域チューナブル発振器

【課題】同調帯域上で比較的低く均一な位相ノイズを維持しながら、マルチオクターブ帯域周波数選択性を有する電圧制御発振器を提供する。

【解決手段】電圧制御発振器100は、バイポーラトランジスタからなる能動素子104、チップ形態での実装が可能なマルチモード結合共振器120、遅波結合共振器124、進行波結合共振器128、ノイズフィルタリング回路網108、ノイズ除去回路網112、ノイズフィードバック・DCバイアス回路116及び位相補償回路網132等により構成されている。これらの構成により、広帯域線形同調レンジを実現しつつ位相ノイズを最小化し、動作周波数帯域全体にわたって均一な出力パワーと改善された高次高調波の遮断が実現できる。

(もっと読む)

可変インダクタを備える物品

【課題】本発明は、ミクロ機械の可変/同調可能なインダクタを提供する。

【解決手段】本発明のインダクタは、空間電磁継手を支持することができる少なくとも二つの素子と、その幾何学的関係を変化させるための手段とを備える。上記素子の間の幾何学的関係を変化させると、インダクタのインダクタンスが変化する。ある実施形態の場合には、変化する幾何学的関係は、二つの素子の間の空間である。上記空間は、上記素子の間の差動運動により変化する。他の実施形態の場合には、本発明は、上記可変インダクタを内蔵する共振回路を含み、オッシレータは、上記共振回路を含む。

(もっと読む)

発振回路及びこれを備えた通信装置

【課題】高レベルでしかも高Q値の出力を得ることができる発振回路及びこれを備えた通信装置を提供する。

【解決手段】発振回路1を第1スロット線路2と第2スロット線路3と第3スロット線路4とFET5で構成した。第1スロット線路2を出力ポートとし、第2スロット線路3を、ショートスタブ30とDCカット線路31で構成し、ショートスタブ30の長さをλg/2〜3λg/4に設定した。また、第3スロット線路4も、ショートスタブ40とDCカット線路41で構成し、ショートスタブ40の長さをλg/4〜λg/2に設定した。そして、ゲート電極Gとドレイン電極Dとが第2スロット線路3を、ドレイン電極Dとソース電極Sとが第3スロット線路4を、ソース電極Sとゲート電極Gとが第1スロット線路2をそれぞれ挟むように、FET5を実装した。帯域反射型共振器6は長さλg/4のショートスタブである。

(もっと読む)

発振信号出力装置

【課題】 発振信号を出力する発振信号出力装置において、電力効率を改善し、発振周波数の高速化を可能にする。

【解決手段】 発振器1は、電源Vddの電力の供給によって発振信号を出力する。抵抗R1は、発振器1と電源Vddの間に接続されている。パルス信号発生器2は、発振器1と電源Vddの間に接続され、Lレベルのパルス信号によって発振器1に電力が供給されるようにしている。これにより、発振器1は、パルス信号に応じて電源がオン/オフされるので、電力効率を改善することができる。また、抵抗R1は、発振器1の発振の立下りを速やかに行うようにするので、発振器1に高速の発振器を用いることが可能となり、発振周波数の高速化が可能となる。

(もっと読む)

1 - 13 / 13

[ Back to top ]