Fターム[5J081EE09]の内容

LC分布定数、CR発振器 (9,854) | 周波数決定素子 (1,325) | 分布定数 (166) | ストリップ線路共振器 (88)

Fターム[5J081EE09]に分類される特許

1 - 20 / 88

電圧制御発振器および関連システム

【課題】位相雑音および出力が改善された電圧制御発振器および関連システムを提供する。

【解決手段】電圧制御発振器は、第1の可変静電容量素子(120)と、第2の可変静電容量素子(122)と、可変静電容量素子(120、122)間に結合され、出力ノード(104)において、発振信号の振動周波数において可変静電容量素子(120、122)の間にインダクタンスを提供する誘導素子(132)とを含む。第1の可変静電容量素子(120)は第1の制御電圧ノード(110)および出力ノード(104)の間に結合され、第2の可変静電容量素子(122)は第1の制御電圧ノード(110)に結合され、第2の誘導素子(134)は第2の可変静電容量素子(122)および第2の制御電圧ノード(112)の間に結合される。

(もっと読む)

電圧制御発振器

【課題】5GHz以上の周波数帯域で出力周波数を調整するコルピッツ回路を用いた電圧制御発振器において、出力周波数の可変幅(調整幅)の劣化(低下)を抑えると共に、位相雑音の良好な特性を持つ電圧制御発振器を提供すること。

【解決手段】可変周波数帯域内における周波数fに対応する波長をλとすると、共振部1のバリキャップダイオード13とトランジスタ21のベース端子との間に直列となるように、線路長Dがλ/4で且つ特性インピーダンスが10Ω以下の伝送線路6を配置して、トランジスタ21のベース端子からバリキャップダイオード13側を見た時に、当該バリキャップダイオード13と伝送線路6とがいわば可変インダクタンス素子Lと等価になるようにする。

(もっと読む)

帰還型発振装置

【課題】設計および製造が容易で、装置のサイズが小さい帰還型発振装置を提供すること。

【解決手段】帰還型発振装置1において、入力端子から入力された信号を増幅して出力端子から出力するバイポーラトランジスタ10と、マイクロストリップラインによって構成され、バイポーラトランジスタの出力端子と入力端子とを結合して出力端子から入力端子に所定の周波数の信号を帰還してバイポーラトランジスタを発振させる結合回路15と、を有する。

(もっと読む)

高周波発振器

【課題】 位相雑音を劣化させずに2倍波の出力電力を増加できる高周波発振器を得る。

【解決手段】 第1から第3の端子を有する能動素子と、前記第1と第2の端子にそれぞれ接続され、所要の周波数において誘導性となる第1と第2のリアクタンス回路と、前記第3の端子に接続され、前記所要の周波数において容量性となる第3のリアクタンス回路と、前記能動素子の前記第3の端子と前記第3のリアクタンス回路の間に並列に接続され、前記所要の周波数の2倍の周波数においてインピーダンスがショートとなる第4のリアクタンス回路と、前記能動素子の前記第3の端子と前記第3のリアクタンス回路の間に並列に接続され、前記所要の周波数におけるリアクタンスが、前記所要の周波数における前記第4のリアクタンス回路のリアクタンスと絶対値が等しく符号が逆となる第5のリアクタンス回路と、を備える。

(もっと読む)

高周波発振器

【課題】小型に構成され、高調波と基本波との電力比を増加可能な高周波発振器を得る。

【解決手段】印加された電源電圧に基づいて、発振周波数の基本波で発振動作を行い、発振周波数の2倍波を出力する2倍波取り出し型発振器10と、2倍波取り出し型発振器10の出力端子に接続され、発振周波数の2倍波を通過帯域とする出力回路20とを備え、出力回路20は、2倍波取り出し型発振器10に電源電圧を供給する電源端子21と、2倍波取り出し型発振器10と電源端子21との間に直列に接続され、発振周波数の2倍波に対してほぼ1/4波長の長さを有する結合線路22と、2倍波取り出し型発振器10と電源端子21との間に直列に接続され、発振周波数の2倍波に対してほぼ1/4波長の長さを有する伝送線路23と、結合線路22の結合量に応じた出力電力を得る第1負荷抵抗24と、電源端子21に対して並列に接続されたキャパシタ25とを有する。

(もっと読む)

プッシュプッシュ発振器及び位相ずれ監視方法

【課題】位相ずれを確認する技術を提供する。

【解決手段】プッシュ・プッシュ発振回路100は、相互に逆位相で動作する、2つの発振器1、2と、2つの発振器1、2から出力された第1出力信号を合成する合成器101と、合成器101から出力された第2出力信号に含まれる第1出力信号の基本波を監視するための基本波監視回路102と、を備えている。即ち、基本波監視回路102を用いることで、合成器101から出力された第2出力信号に含まれる第1出力信号の基本波を確認することができる。第1出力信号の基本波を確認することで、合成器101に入力された2つの第1出力信号が逆位相であったか確認することができる。

(もっと読む)

アナログ回路

【課題】高い歩留りを得ながらゲートスロープを抑制することができるアナログ回路を提供する。

【解決手段】アナログ回路には、発振トランジスタ27と、発振トランジスタ27に対する負性抵抗を変更する負性抵抗変更回路と、が設けられている。負性抵抗変更回路には、可変抵抗回路及び可変容量回路が含まれている。可変抵抗回路には、抵抗体29、抵抗体31及びトランジスタ(スイッチ)35が含まれ、可変容量回路には、キャパシタ30及び可変容量ダイオード36が含まれている。

(もっと読む)

電子回路

【課題】負性抵抗回路において反射特性を向上させること。

【解決手段】制御端子、第1端子および第2端子を有する第1トランジスタとQ1、前記第1トランジスタの前記第2端子に接続された制御端子、第1端子およびDC電源が接続される第2端子を有する第2トランジスタQ2と、前記第1トランジスタの前記第1端子と前記第2トランジスタの前記第1端子との信号を前記第1トランジスタの制御端子に共通に帰還させる正帰還回路22と、前記第2トランジスタの前記第1端子と前記正帰還回路との間に接続された第1キャパシタC1と、前記第1トランジスタの前記第2端子と前記第2トランジスタの前記制御端子との間の第1ノードN1と、前記第2トランジスタの前記第1端子と前記第1キャパシタとの間の第2ノードN2と、をDC的に接続する経路12と、を具備する電子回路。

(もっと読む)

高周波二倍波発振器

【課題】本発明は、位相雑音の劣化原因によらず位相雑音を低減できる高周波二倍波発振器を提供することを目的とする。

【解決手段】トランジスタと、該トランジスタのベース側に接続された第一電気信号線路と、該第一電気信号線路に接続され他の端は接地された第一シャントキャパシタと、該トランジスタのコレクタ側に接続された第二電気信号線路と、該第二電気信号線路に接続され他の端は接地された第二シャントキャパシタと、該第一電気信号線路と該第二電気信号線路を接続する大容量キャパシタとを備える。該第一電気信号線路の線路長は、基本波信号の波長の1/4の値を奇数倍した長さから基本波信号の波長の1/16の長さを減算した長さと、基本波信号の波長の1/4の値を奇数倍した長さに基本波信号の波長の1/16の長さを加算した長さとの間の値である。

(もっと読む)

マイクロ波発振回路およびその実装方法

【課題】 スルーホールを削減してプリント基板の製造コストアップを防ぎ、基板の線膨張率の違いによる発振周波数ずれを防ぎ、基板に窓を空ける必要がなく、発振周波数範囲が狭くなるのを防ぎ、かつ中心周波数の調整が可能なマイクロ波発振回路の提供。

【解決手段】 マイクロ波発振回路100は、上部基板1と、その表面に設けられる第1表層パターン2と、第1表層パターン上に設けられ第1表層パターンと電気的接続される可変容量素子3と、上部基板の表面の第1表層パターンとは異なる位置に設けられる第2表層パターン4と、第2表層パターン上に設けられ第2表層パターンと電気的接続される発振素子5と、上部基板の裏面に設けられる第1および第2裏面パターン6,7と、下部基板8と、下部基板の表面に設けられる第3表層パターン9と、下部基板の裏面に設けられる第3裏面パターン10とを含む。

(もっと読む)

高周波帯電圧制御発振器

【課題】共振回路における発振周波数の公差を低減し、PLL回路に用いられる論理回路の低電圧化傾向の下でも、発振周波数の高周波化を図る。

【解決手段】発振周波数を可変制御するLC同調型の電圧制御発振器において、発振用トランジスタ1のエミッタ側で、接地電位となる一対のスルーホールH1 ,H2 の間に、同一線路長のマイクロストリップ線路からなる2つのショートスタブP1 ,P2 を形成し、これらショートスタブP1 とP2 との間に上記トランジスタ1のエミッタを接続する。即ち、ショートスタブP1 とP2 は、エミッタ接続点を中心に対称となる位置で並列に接続される。また、コンデンサC1 ,C2 でDCカットされたバラクタCvのカソードに、0〜5Vの制御用電圧Vtを印加すると共に、アノードに、基準電圧源6から例えば−5Vの基準電圧を印加する。

(もっと読む)

電圧制御発振器

【課題】マイクロストリップラインのトリミングによってQ値の劣化を招くことなく、各種の周波数帯への調整を可能とする。

【解決手段】電圧制御発振器は、発振用トランジスタのベースに接続された共振回路を有しており、この共振回路には、バラクタダイオードとともにマイクロストリップライン10が設けられている。マイクロストリップライン10は、その一端が制御端子に接続されており、他端がビア7を介してグランド電極に接続されている。またマイクロストリップライン10は、その一端に位置する入力導体部10bから他端に位置する接地導体部10eに至る導電路がスパイラル形状をなしており、導電路の途中が粗調用導電体10aを介してグランドに接続されている。

(もっと読む)

電圧制御発振回路

【課題】発振回路の出力周波数範囲を従来に対して拡大方向にもっていくことにより、発振周波数を目的とする周波数に合致させ易くした電圧制御発振回路を提供する。

【解決手段】発振に寄与するトランジスタTrのソース端子に、第1の誘導性素子Tscと、印加される電圧により容量が変化するダイオード素子C1〜C4により構成される容量性素子を直列接続したもの、が接続されているとともに、トランジスタTrのソース端子に、第2の誘導性素子Tsの一端が接続されており、第2の誘導性素子Tsの他端が接地されており、トランジスタTrのゲート端子に、第3の誘導性素子Tgを介してバイアス電圧端子Vggが接続されており、トランジスタTrのドレイン端子に、出力側の回路3を介して出力端子Voutが接続されている。

(もっと読む)

発振器及び位相同期回路

【課題】十分に高い周波数帯域において、広帯域にわたって柔軟に発振周波数を調整すること。

【解決手段】信号線131は、電源から直流電圧Vdcが印加されると、電源に接続された始端を節とし、終端を腹とする4分の3波長の定在波を発生させる。ストリップ132−1〜132−nは、それぞれスイッチ133−1〜133−nを介してグランド層に接続されている。スイッチ133−1〜133−nは、切替制御部140による制御に従って、それぞれストリップ132−1〜132−nとグランド層との接続及び非接続を切り替える。スイッチ133−1〜133−nの接続及び非接続を切り替えることにより、擬似的に信号線131とグランド層の間の距離が調節され、伝送線路部130における実効誘電率が変化して、定在波の周波数を調整することができる。

(もっと読む)

高周波発振器

【課題】高価な誘電体共振器やバラクタダイオードを使用することなく、廉価に制作することができ、また回路面積が小さく小型化が可能となるようにする。

【解決手段】誘電体基板1上に形成されたマイクロストリップ線路2において、増幅素子3の入力端のゲートが入力端側線路2aに接続され、出力端のドレインが出力端側線路2bに接続され、ソースが接地電極5を介して基板裏面の接地面7に接続される。そして、上記増幅素子3の上面に、例えば棒状の金属体10を絶縁性接着剤9によって接着し、この金属体10をマイクロストリップ線路2の伝送線路方向に配置することで、この金属体10の一方端を入力端側線路2a、他方端を出力端側線路2bに容量性結合する。この金属体の結合は、一端のみでもよい。これによれば、増幅素子3からの出力が、容量C12、インダクタンスL、容量C11を通って入力端へ帰還し、発振が行われる。

(もっと読む)

スプリット遅延ライン発振器における装置、システム及び方法

【課題】安全なデータ伝送を行うスプリット遅延ライン発振器における装置、システム及び方法を提供すること。

【解決手段】安全なデータ伝送を行うスプリット遅延ライン発振器における本装置は、第1装置における第1の変調/復調ブロックを有し、その第1の変調/復調ブロックは、第1の可変遅延を設定し、第1の変調/復調ブロックを通過する共有キャリア信号の周波数を変調し、第2装置における第2の変調/復調ブロックは、第2の可変遅延を設定し、第2の変調/復調ブロックを通過する共有キャリア信号の周波数を変調し、第1及び第2装置は、周波数変調された共有キャリア信号にデータを与えることで、共有する秘密情報を作成する。

(もっと読む)

オーム調節可能な発振周波数を有する発振器

調節可能な発振周波数を有する発振器は、端子で負性入力抵抗を示している能動素子、負性入力抵抗を示しているその能動素子の端子と連結した発振回路、および、その発振器の発振周波数が調節可能である調節可能なオーム抵抗を有する素子を含む。 (もっと読む)

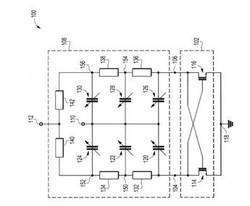

発振回路

発振回路10は、プッシュ−プッシュ型発振器12と、差動出力部14,15と、第1、第2の出力回路16,18とを備える。プッシュ−プッシュ型発振器12は第1、第2の分岐回路20,22を有する。第1、第2の分岐回路20,22の各々は共通のブリッジ回路28にそれぞれの分圧分岐回路24,26を備える。第1、第2の分圧分岐回路24,26の各々は、直列に接続された一対のマイクロストリップライン30,32;34,36をそれぞれ備える。第1、第2の分圧分岐回路24,26の各々は、それぞれのタップC,Dを有する。両方のタップC,Dは、第1の容量性部材42およびマイクロストリップラインのうちの少なくとも一方によって互いに接続されている。差動出力部は、第1、第2の出力端子14,15を備える。第1の出力端子14は第1の出力回路16を介して第1のノードAに接続されている。第2の出力端子15は第2の出力回路18を介して第2のノードBに接続されている。プッシュ−プッシュ型発振器12の第1、第2のノードA,Bの各々は、第1、第2の分岐回路20,22の両方の共通のノードA,Bである。  (もっと読む)

(もっと読む)

発振器

【課題】高い発振周波数で動作する場合であっても、十分なストリップライン長を確保することができ、製造誤差によるバラつきを防止すると共に、Qの低下を防止すること。

【解決手段】発振器10は、発振トランジスタ2と、前記発振トランジスタ2のベース−エミッタ間に設けられる第1の帰還コンデンサ4と、前記発振トランジスタ2のコレクタ−エミッタ間に設けられる第2の帰還コンデンサ5と、前記発振トランジスタ2のベースに一端が接続される共振用ストリップライン13と、前記発振トランジスタ2のエミッタ−グラウンド間に設けられるトラップ回路20と、を備え、前記共振用ストリップライン13は、発振周波数において高次共振モードとなる長さを有し、前記トラップ回路20は、前記高次共振モードより低次側の低次共振モードに相当する周波数の信号を減衰させるものである。

(もっと読む)

電圧制御発振回路

【課題】発振周波数を制御するPLL回路で生成可能な制御電圧の最大値を低電圧化しても、可変容量ダイオードに印加される電圧の可変範囲を広げることができ、しかも簡単な回路構成で実現でき、発振器の小型化を図ること。

【解決手段】この電圧制御発振回路1は、発振用トランジスタ2と、可変容量ダイオード16を有し発振用トランジスタ2に接続された共振回路13と、電源電圧が印加される電源端子T2とグラウンドとの間に介挿されると共に可変容量ダイオード16に対して並列に接続されたコレクタ抵抗RCと、コレクタ抵抗RCのグラウンド側の端部とグラウンドとの間に介挿され発振周波数を制御する制御電圧が印加される制御用トランジスタ21とを具備する。

(もっと読む)

1 - 20 / 88

[ Back to top ]