Fターム[5J081LL09]の内容

LC分布定数、CR発振器 (9,854) | 改善手段(発明内容) (679) | 特性の変更 (11)

Fターム[5J081LL09]に分類される特許

1 - 11 / 11

半導体装置

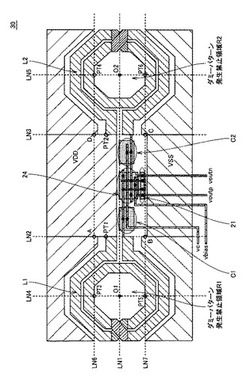

【課題】VCOに含まれるスパイラルインダクタとMOSバラクタを接続する配線に付加される寄生インダクタ、および/または寄生容量を低減することができる半導体装置を提供する。

【解決手段】LCタンクVCOは、第1および第2のスパイラルインダクタL1,L2と、第1および第2のMOSバラクタC1,C2とを備える。第1および第2のMOSバラクタC1,C2は、半導体基板に垂直な方向から見たときに、第1のスパイラルインダクタL1と第2のスパイラルインダクタL2の間の領域に配置される。

(もっと読む)

発振器

【課題】高い発振周波数で動作する場合であっても、十分なストリップライン長を確保することができ、製造誤差によるバラつきを防止すると共に、Qの低下を防止すること。

【解決手段】発振器10は、発振トランジスタ2と、前記発振トランジスタ2のベース−エミッタ間に設けられる第1の帰還コンデンサ4と、前記発振トランジスタ2のコレクタ−エミッタ間に設けられる第2の帰還コンデンサ5と、前記発振トランジスタ2のベースに一端が接続される共振用ストリップライン13と、前記発振トランジスタ2のエミッタ−グラウンド間に設けられるトラップ回路20と、を備え、前記共振用ストリップライン13は、発振周波数において高次共振モードとなる長さを有し、前記トラップ回路20は、前記高次共振モードより低次側の低次共振モードに相当する周波数の信号を減衰させるものである。

(もっと読む)

インピーダンス変換回路、高周波回路、及びインピーダンス変換回路のインピーダンス変換特性調整方法

【課題】誘電体チップ等の付加や、スタブ長の長いオープンスタブを用いることなく、インピーダンス変換の特性調整を可逆的に且つ微調整可能なようにしたインピーダンス変換回路及びそれを備えた高周波回路を構成する。

【解決手段】スタブST2の長さを固定したままスタブST1の長さを短くすると、インピーダンスZbはアドミッタンスチャート上を矢印A1で代表する方向に移動する。また、スタブST1の長さを固定したままスタブST2の長さを短くすると、インピーダンスZbはアドミッタンスチャート上の等コンダクタンス円上を矢印A2で代表して示すように移動する。したがって図中スミスチャートの中心とショート点とを直径とする円内では、インピーダンス軌跡は、スタブST1,ST2のトリミングによってインピーダンスは互いに可逆的に調整できることになる。

(もっと読む)

誘電体共振器型発振器及びそれを用いたレーダシステム

【課題】誘電体共振器型発振器(DRO)の量産においては、誘電体共振器を設置する位置を高い精度で調節する必要があり、組立作業に要する時間が増大してしまう。また、誘電体共振器と電磁的に結合させ、共振器を構成する伝送線路の先端の終端抵抗および接地手段を誘電体基板上に形成すると製造コストが高くなる。

【解決手段】DROの構成部品のうち、伝送線路のみを誘電体基板上に形成し、MMICチップ上の発振用能動素子、終端抵抗および接地手段を伝送線路と金属ワイヤ、金属リボン等で接続する。また、誘電体共振器から見て発振用能動素子側の伝送線路の中途に、オープンスタブを形成する。

(もっと読む)

発振器、および発振を開始する方法

発振信号がコールドスタートからの規定の定常状態条件に達する時を早める回路を含んでいる発振信号を生成するための装置。装置は、発振信号を生成するための発振回路と、発振回路に第1の電流を供給する第1の回路と、発振回路に第2の電流を供給する第2の回路と、を含み、第1および第2の電流は、発振信号が規定の定常状態条件に達するための時間分を縮小するのに適している。装置は、1以上の通信チャネルを確立するために低い負荷サイクルパルス変調を用いる通信システムに有益であるかもしれず、それによって装置はパルスのほぼ始めで発振信号を生成し始め、パルスのほぼ終わりに発振信号を終了する。  (もっと読む)

(もっと読む)

高周波共振器及び高周波発振器

【課題】0次共振周波数におけるQ値の劣化を招くことなく、高次の共振周波数を減衰させることができる高周波共振器を得ることを目的とする。

【解決手段】入力端子1と出力端子2の間に縦続接続されている複数の直列共振回路3−nと、一端が複数の直列共振回路間の接続点に接続されて、他端が接地されている複数の並列共振回路4−mとから構成して、複数の直列共振回路3−n内に抵抗6a,6bを装荷する。これにより、0次の共振周波数におけるQ値の劣化を招くことなく、高次の共振周波数を減衰させることができる。

(もっと読む)

発振制御装置

【課題】 VCOのf/v感度のばらつきを補正することで、VCOの安定動作とC/N劣化などの特性の劣化防止を図ることができる発振制御装置を提供する。

【解決手段】 可変共振器2を備えるVCO1と分周器6と位相比較器7とLPF8とによって構成されるPLLにおいて、可変共振器制御信号生成部10が、LPF8の出力電圧を入力してVCO1のf/v感度を検出して可変共振器制御信号を生成し、可変共振器制御信号によって可変共振器2の容量を制御する。具体的には、電圧検知回路5がLPF8の出力電圧を入力して所定の電圧を検知すると、データラッチ回路4が電圧検知回路5の検知した電圧に基づいた可変共振器制御信号を可変共振器2へ送信して可変容量の制御を行う。その結果、PLLの構成素子のばらつきや温度変化があってもVCO1のf/v感度を最適値に制御することができる。

(もっと読む)

電圧制御発振器とその周波数調整方法

【課題】十分なシールド効果が得られると共に、前記レーザーによる貫通等が起こらず、高い信頼性が得られる電圧制御発振器を提供する。

【解決手段】積層構造の基板1の内部にストリップライン共振器9を形成する。基板1の内部に周波数調整用のトリミング電極19を設ける。基板1の主面(表面または裏面)から照射されるレーザーによるトリミング溝20が、第1段階のトリミング溝20Aと、第2段階のトリミング溝20Bとからなる。前記第1段階のトリミング溝20Aは、トリミング始点22A側が深く形成される。第2段階のトリミング溝20Bは、第1段階のトリミング溝20Aより深く、前記トリミング電極を貫通する深さに形成される。また、第2段階のトリミング溝20Aは、第1段階のトリミング溝20Aのトリミング始点22A側の深く形成された部分25以外の部分の少なくとも一部に重ねて形成される。

(もっと読む)

エバネッセントモード形結合共振器を使用する広帯域電圧制御発振器

1つの態様では、本発明は、能動素子の2つの端子の間に接続された複数の共振器を有する能動素子と、複数の共振器の間に接続された少なくとも1つの共振器とを含む電圧制御発振器を含んでいる。この少なくとも1つの共振器は、好ましくは、発振器の中に存在する選択された量のエネルギーを蓄積できるエバネッセントモード形バッファとして動作する。  (もっと読む)

(もっと読む)

熱ドリフトがユーザ指定可能な電圧制御発振器

電圧制御発振器(200)は、共振器(240)、同調ダイオード回路網(234)および能動装置(210)にわたってそれらに結合されたスロット切込プリント基板回路網(230)を含む。スロット切込プリント基板回路網(230)は、共振器(240)、同調ダイオード回路網(234)および能動装置(210)の間で共通結合コンデンサとしての機能を果たすよう働く。

(もっと読む)

(もっと読む)

発振回路

【課題】出力高調波が少なく安定性が高いフィルタ帰還型の特性を有し、発振周波数を広い範囲で制御することができる発振回路を提供する。

【解決手段】増幅回路10の出力は、周波数特性の異なる2つのバンドパスフィルタ13、14に分配回路11により所定の比率に分配されて供給される。バンドパスフィルタ13、14の出力は加算回路15により加算される。さらに、この加算後の出力は増幅回路10の入力に帰還され、この増幅回路10により増幅される。このような処理により、増幅回路10の出力の一部が入力側に正帰還され、所定周波数の信号の増幅が繰り返されて、所定周波数にて発振する出力信号Voutが生成される。このとき、制御回路12により、前記分配回路11によって分配される前記所定の比率を変更することにより、出力信号Voutの発振周波数が制御される。

(もっと読む)

1 - 11 / 11

[ Back to top ]